Цифровое устройство фазовой синхронизации

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и повьшает помехоустойчивость при малом времени вхождения в синхронизм. -За счет большого количества импульсов, поступивших на вход вычитания реверсивного счетчика 8, в нем записывается отрицательное число, знак которого с приходом тактового импульса с частотой f записывается в D-триггер 9 и устанавливает широкую полосу фильтра 5 нижних частот, обеспечивающую малое время вхождения в синхронизм. В D-триггер 9 с приходом тактового импульса с частотой f записывается потенциал, соответствующий положительному числу, который переключает параметры фильтра 5 на параметры, соответствующие узкой шумовой полосе. Это позволяет уменьшить дисперсию ошибки синхронизации в установившемся режиме. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

ÄÄSUÄÄ 1358103 А1 (51) 4 Н 04 L 7/02 к, 1, >

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOIVIY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 393 71 73 /24-09 (22) 26.07,85 (46) 07.12,87. Бюп. У 45 (72) Н.И.Козленко, Ю.В.Левченко, А.P.Ïîïoâ и Л.И.Алгазинова (53) 621.394.662(088.8) (56) Авторское свидетельство СССР

У 1116545, кл. Н 04 L 7/02, 1982. (54) ЦИФРОВОЕ УСТРОЙСТВО ФАЗОВОЙ СИНХР О НИЗАЦИИ (57) Изобретение относится к радиотехнике и повышает помехоустойчивость при малом времени вхождения в синхронизм. -За счет большого количества импульсов, поступивших на вход вычитания реверсивного счетчика 8, в нем записывается отрицательное число, знак которого с приходом тактового импульса с частотой f записывается в D-триггер 9 и устанавливает широкую полосу фильтра 5 нижних частот, обеспечивающую малое время вхождения в

-синхронизм. В D-триггер 9 с приходом тактового импульса с частотой f тч записывается потенциал, соответствующий положительному числу, который переключает параметры фильтра 5 на параметры, соответствующие узкой шумовой полосе. Это позволяет уменьшить дисперсию ошибки синхронизации в установившемся режиме. 2 ил.

1358103 2 ла переноса (займа), если код прямой (дополнительный), разрешает прохождение тактового импульса на первый (второй) выход преобразователя через элементы И 16 и 17.

Частота выходных тактовых импульсов с преобразователя 3 пропорциональна абсолютной величине кода, снимаемого с выхода ЦФНЧ 5, и частоте тактовых импульсов f, поступающих на регистр 15. Покажем это на примере.

Пусть на вход четырехразрядного сумматора 14 поступает положительный код, равный единице. С приходом тактовых импульсов и „ на регистр 15, к содержимому реги™стра добавляется единица. Для того, чтобы возник сигнал переноса в сумматоре 14, на регистр 15 должно поступить 16 тактовых импульсов. Если на входы сумматора 14 поступает код, равный двум, то сигнал переноса на выходе сумматора

14 возникает в два раза чаще, т.е. через восемь импульсов и т.д.

Аналогично, при поступлении на преобразователь 3 дополнительного кода, равного единице (соответствун)щего отрицательному рассогласованию), и

16 тактовых импульсов t íà выходе переноса сумматора 14 возникает сигнал. Если на вход преобразователя 3 поступает дополнительный код,равный двум, то сигнал переноса на выходе сумматора 14 возникает в два раза чаще и т.д.

С выходов преобразователя 3 сигналы поступают на входы управления блока 11 добавления-вычитания импульсов. В зависимости от того, на какой вход блока 11 поступают сигналы с преобразователя 3, блок 11 добавления-вычитания вводит дополнительный или стирает один из импульсов в импульсной последовательности. формируемой формирователем 12 из сигнала опорного генератора 13. Изменение числа импульсов на единицу в импульсной последовательности на входе делителя 7 частоты приводит к дискретному сдвигу фазы выходного сигнала на величину

2)) ) р ) 55 где D

Изобретение относится к радиотехнике и может быть использовано для фазовой синхронизации в приемниках дискретной информации.

l)

Цель изобретения — повышение поме" хоустойчивости при малом времени вхождения в синхронизм.

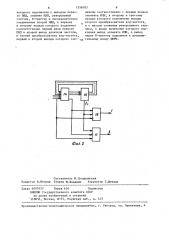

На фиг. 1 представлена структурная электрическая схема цифрового устройства фазовой синхронизации; на фиг. 2 — структурная схема первого, второго и третьего преобразователей код-частота.

Цифровое устройство фаэовой синхронизации содержит первый 1 и второй 2 (ЦФД), первый 3 и второй 4 преобразователи код-частота, ЦФНЧ 5, элемент ИЛИ 6,делитель 7 частоты, реверсивный счетчик 8, D-триггер 9, третий преобразователь 10 код-частота, блок 11 добавления-вычитания, формирователь 12 импульсов, опорный генератор 13.

Преобразователь код-частота (фиг.

2) содержит сумматор 14, регистр

15, первый 16 и второй 17 элементь1

И.

Устройство работает следующим образомм. 30

На первый вход цифрового фазового детектора 1 поступает входной сигнал, на второй вход — импульсы с делителя 7 частоты.

В зависимости от фазового сдвига импульсов делителя 7 частоты и входного сигнала на выходе цифрового фазового детектора 1 формируется код, абсолютная величина и знак которого соответствуют значению фазового рас- 40 согласования входного и выходного сигналов. При отсутствии фазового рассогласования с выхода ЦФД 1 на вход ЦФНЧ 5 и первого преобразователя 3 код-частота поступает нулевой 45 код. ЦФНЧ 5 предназначен для уменьшения действия помех на точность подстройки фазы, а также для получения требуемых динамических характеристик.

С выхода ЦФНЧ 5 сигнал поступает на 50 входы первого слагаемого сумматора первого преобразователя 3 код-частота. На вторые входы сумматора 14 поступает код, снимаемый с регистра 15.

При поступлении тактовых импульсов и „на регистр 15 в нем записывается результат сложения выходного кода

ЦФНЧ 5 с содержимым регистра 15. Появление на выходе сумматора 14 сигна— коэффициент деления частоты выходного делителя.

При данном алгоритме работы блоков частота выходного сигнала связана с

1358103 выходным кодом U ЦФНЧ 5 линейной зависимостьюю

27i U

Е(Б) = f +

О D c 1

35 ется тем, что на вход вычитания реверсивного счетчика 8 с преобразователей 4.и 10 поступают импульсы при дополнительном коде и с преобразователя 4 — при прямом коде рассогласования, На вход сложения реверсивного счетчика 8 поступают импульсы с преобразователя 10 при прямом коде рассогласования.

Таким образом, за счет большого количества импульсов, поступивших на вход вычитания реверсивного счетчика

8, в последнем записывается отрицательное число, знак которого с приходом тактового импульса с частотой

50 где fr — тактовая частота, поступающая на преобразователь 3; — частота выходного сигнала, соответствующая нулевому ко- 10 ду °

Код с выхода ЦФД 1 поступает также на первые входы преобразователя 4, который выполнен так же, как преобразователь 3, и работает аналогично.

Выходные импульсы преобразователя 4, снимаемые с первого и второго выхода, через элемент ИЛИ 6 поступают на вход вычитания реверсивного счетчика 8.

Преобразователь-10, на который посту- 20 пает выходной код ЦФД 2, выполнен и работает аналогично преобразователю 3.

Выходные импульсы преобразователя 10, снимаемые с первого выхода, поступают через элемент ИЛИ 6 на вход вычитания реверсивного счетчика 8, а снимаемые с второго выхода поступают на вход слежения реверсивного счетчика 8.

На ЦФД 1 и 2 с двух выходов делителя 7 поступают сдвинутые на чет- З0 верть периода относительно друг друга тактовые импульсы, В работе цифрового устройства фазовой синхронизации можно выделить два основных режима: вхождение в синхронизм и слежение °

В режиме вхождения в синхронизм количество импульсов, поступивших за время, равное периоду импульсов Т

1 40 на вход вычитания реверсивно Э

ro счетчика 8, превышает количество импульсов, поступивших на вход сложения того же счетчика. Это объясняf записывается в D-триггер 9 и устага навливает широкую полосу ЦФНЧ 5, обеспечивающую малое время вхождения в синхронизм.

В установившемся режиме фазовое рассогласование между входным сигналом и сигналом, снимаемым с первого выхода делителя 7,имеет малое значение, т.е. импульсы, снимаемые с выхода делителя 7, располагаются в нуле входного сигнала. Поэтому на выходе

ЦФД 1 присутствует шумовая составляющая °

Так как импульсы, снимаемые с второго выхода делителя 7, сдвинуты по фазе на четверть периода по отношению к импульсам, снимаемым с первого выхода делителя 7, то с выхода

ЦФД 2 снимаются как шумовая, так и сигнальная составляющие, соответствующие фазовому рассогласованию T /2.

В результате среднее число импульсов, поступающих на вход сложения реверсивного счетчика 8 за период времени, определяемый тактовой частотой f больше, чем число импульсов, поступающих на вход вычитания реверсивного счетчика 8. В D-триггер 9 с приходом тактового импульса с частотой

fr, записывается потенциал, соответствующий положительному числу, который переключает параметры ЦФНЧ 5 на параметры, соответствующие узкой шумовой полосе. Это позволяет уменьшить дисперсию ошибки синхронизации в установившемся режиме.

Формула изобретения

Цифровое устройство фаэовой синхронизации, содержащее последовательно соединенные первый цифровой фазовый детектор (ЦФД), первый вход которого является входом цифрового устройства фазовой синхронизации, цифровой фильтр нижних частот (ЦФНЧ), первый преобразователь код-частота, блок добавления-вычитания, к тактовому входу которого подключен выход опорного генератора через формирователь импульсов, и делитель частоты, выход которого подключен к второму входу первого ЦФД и является выходом цифрового устройства фазовой синхронизации, о т л и ч а ю щ е е с я тем, что, с целью повышения помехозащищенности при малом времени вхождения в синхронизм, введены второй преобразователь код-частота, входы

1358103

Фиг. 2

Составитель И. Грацианская

Редактор В.Петраш Техред M.Ходанич Корректор С.Шекмар

Заказ 6009/57 Тираж 636 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 которого подключены к выходам первого ЦФД, элемент ИЛИ, реверсивный счетчик, D-триггер и последовательно соединенные второй ЦФД, к первому и второму входам которого подключен соответственно первый вход первого

ЦФД и второй выход делителя частоты, и третий преобразователь код-частота, первый и второй выходы которого соединены соответственно с первым входом элемента ИЛИ, к второму и третьему входам которого подключены выходы второго преобразователя код-частота, и с. входом сложения реверсивного счетчика, к входу вычитания которого подключен выход элемента ИЛИ, а выход через D-триггер подключен к дополнительному входу ЦФНЧ.