Устройство цикловой синхронизации

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи и обеспечивает повышение точности синхронизации путем контроля установления синхронизма при приеме контрольной информации без увеличения времени вхождения в синхронизмГ Устр-во содержит блок 1 опознавания сосредоточенной синхрогруппы, нако- . питель 2 по выходу из синхронизма, накопитель 3 по входу в синхронизм, ,элементы И 4,9, ИЛИ 5, делитель-распределитель (ДР) 6, блок 7 вьщеления контрольной комбинации. (КК), блок 8 контроля фронтов КК, накопитель 10 ошибок, блок 11 стробирования, формирователь 12 сигналов сброса, формирователь 13 интервала анализа, эле- . мент памяти (ЭП) 14 и формирователь 15 тактового сигнала. Если блок 1 обнаруживает синхрогруппу, логическая 1 с его выхода заносится в накопитель 3, а если не обнаруживает - в накопитель 2. При заполнении накопителя 2 сигнал с его выхода поступает на установочньй вход ДР 6 и на ЭП 14, устанавливая его в состояние Отсутствие синхронизма. При этом ДР 6 сдвигает сигналы на своих выходах на один такт. Если синхрогруппа обнаруживается, то по сигналу заполнения накопителя 3 ДР 6 фиксирует временное положение сигналов на своих выходах, ЭП 14 устанавливается в состояние Синхронизм, разрешая анализ информации, передаваемой по контрольному каналу (блоки 7-13). Это обеспечивает подтверждение истинности синхронизма. 1 ил. i (Л со СП 00

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН цу 4 Н 04 L 7/08

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

Ыи

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3921148/24-09 (22) 02.07.85 (46) 07.12.87. Бюл. Р 45 (72) В.А. Коган и M.Ä. Сафир (53) 62 1.394.662(088.8) (56) Авторское свидетельство СССР

В 403!05, кл. Н 04 M 3/04, 1970.

Колтунов M.Н. и др. Синхронизация по циклам в цифровых системах связи.- М.: Связь, 1980, с. 115., (54) УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ (57) Изобретение относится к электросвязи и обеспечивает повышение точности синхронизации путем контроля установления синхронизма при приеме контрольной информации без увеличения времени вхождения в синхронизм.

Устр-во содержит блок 1 опознавания сосредоточенной синхрогруппы, накопитель 2 по выходу из синхронизма, накопитель 3 по входу в синхронизм, элементы И 4,9, ИЛИ 5, делитель-распределитель (ДР). 6, блок 7 выделения контрольной комбинации, (КК), блок 8

„.80„„1358104 А 1 контроля фронтов КК, накопитель 10 ошибок, блок 11 стробирования, формирователь i2 сигналов сброса, формирователь 13 интервала анализа, элемент памяти (ЭП) 14 и формирователь

15 тактового сигнала. Если блок 1 обнаруживает синхрогруппу, логическая "1" с его выхода заносится в накопитель 3, а если не обнаруживает— в накопитель 2. При заполнении накопителя 2 сигнал с его выхода поступает на установочный вход ДР 6 и на

ЭП 14, устанавливая его в состояние Отсутствие синхрониэма . При этом

ДР 6 сдвигает сигналы на своих выходах на один такт. Если синхрогруп- а ф па обнаруживается, то по сигналу залолнения накопителя 3 ДР 6 фиксирует (/) временное положение сигналов на своих выходах, ЭП 14 устанавливается в состояние "Синхронизм", разрешая анализ информации, передаваемой по контрольному каналу (блоки 7-13). >,щ

Это обеспечивает подтверждение истинности синхронизма. 1 ил. Сд

1358104

Изобретение относится к электро связи и может быть использовано при передаче дискретной информации для циклоного фазирования многоканальной

5 аппаратуры, н которой используется временное разделение каналов и последовательный поиск синхрокомбинации.

Цель изобретения — повышение точности синхронизации путем контроля 10 установления синхронизма при приеме контрольной информации без увеличения времени вхождения в синхронизм.

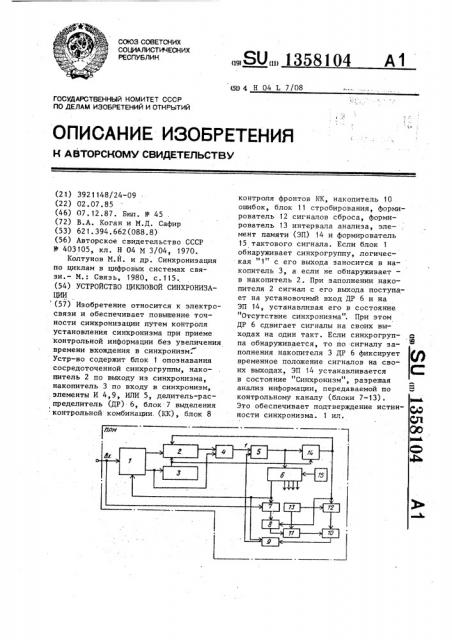

На чертеже представлена структурная функциональная схема устройства 15 цикловой синхронизации.

Устройство циклоной синхронизации содержит блок 1 опознавания сосредоточенной синхрогруппы, накопитель 2 по выходу из синхронизма, накопитель 20

3 по входу в синхронизм, элемент И 4, элемент ИЛИ 5, делитель †распределитель 6, блок 7 выделения контрольной комбинации, блок 8 контроля фронтов контрольной комбинации, дополнительный элемент И 9, накопитель 10 ошибок, блок 11 стробиронания, формирователь

12 сигналов сброса, формирователь 13 интервала анализа, элемент 14 памяти и формирователь 15 тактового сигнала. 30

Устройство цикловой синхронизации работает следующим образом.

Дискретная информация в виде двоичных сигналов поступает на сигнальный вход блока 1 опознавания сосредоточенной синхрогруппы, который по каждому сигналу с управляющего выхода делителя-распределителя 6 анализирует наличие на соответствующей позиции цикла синхрогруппы. Если на анализи- 40 руемой позиции цикла синхрогруппа обнаружена, то с соответствующего выхода блока 1 опознавания сосредоточенной синхрогруппы логическая "1" записывается в накопитель 3 по входу 45 в синхронизм, в противном случае логическая "1" записывается в накопитель 2 по выходу из синхронизма, по заполнении которого сигнал через элемент И 4 и элемент HJIH 5 поступа- 50 ет на установочный вход делителя-распределителя 6, который сдвигает сигналы на управляющем и селектирующих выходах на один такт, и на соответствующий вход элемента 14 памяти, кото- 55 рый устанавливает состояние Отсутствие синхронизма". Если на анализируемой позиции цикла синхрогруппа не обнаружена, то с соответствующего выхода блока 1 опознавания сосредоточенной синхрогруппы сигнал соотнетственно поступает на вход накопителя

3 по вход(в синхронизм, который обнуляет свое значение, и на другой вход элемента И 4, который пропускает сигнал с ньжода накопителя 2 по выходу из синхронизма, по которому делитель-распределитель 6 каждый раэ сдвигает сигналы на своих выходах на один такт. Если же синхрогруппа обнаруживается блоком 1 опознавания сосредоточенной синхрогруппы на одной и той же позиции цикла, то накопитель 3 по входу в синхронизм по соотнетствующим сигналам заполняет свое значение и сигнал с его выхода соответственно поступает на вход сброса накопителя 2 по выходу из синхронизма, который обнуляет свое значение, и другой вход элемента 14 памяти, который устанавливает состояние нСинхронизм . При этом делитель-распределитель 6 фиксирует временное положение сигналов на своих выходах, которые он формирует из импульсов которые поступают с выхода формирователя

15 тактового сигнала.

В состоянии "Отсутствие синхронизма" элемент 14 памяти формирует сигнал, по которому накопитель 2 по выходу из синхронизма уменьшает свою емкость, а блок 8 контроля фронтов контрольной комбинации и накопитель

10 ошибок через формирователь 12 сигналов сброса прекращают работу на все время поиска синхронизма.

В состоянии "Синхронизм" элемент

14 памяти формирует сигнал, по которому разрешается анализировать информацию, передаваемую по контрольному каналу, наличие которого предусматривается при делении передаваемой дис1 кретной информации и которому выделяется определенная позиция в цикле, отстоящая на известное число, обычно на половину позиций в цикле, от позиции, где находится синхрогруппа. Эта особенность учитывается при анализе информации контрольного канала с целью подтверждения истинности состояния Синхронизм", так как при ложном состоянии "Синхронизм" блок 7 выделения контрольной комбинации выделяет позиции в цикле, не соответствующие тем, на которых передается информация контрольного канала. В этом случае

1358104

Составитель А. Яврумов

Редактор В. Бугренкова Техред М.Ходанич Корректор H. Иаксимишинец

Подписное

Заказ 6009/57 Тираж 636

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 сигнал "Авария КК" с выхода блока 8 контроля фронтов контрольной комбинации поступает на блок 11 стробирования, который пропускает его на вход накопителя 10 ошибок в течение интер5 вала, определяемого формирователем

13 интервала анализа, который при этом через формирователь 12 сигналов сброса управляет сбросом накопителя

10 ошибок. Накопитель 10 ошибок предназначен для защиты от случайных ошибок в контрольном канале. Сигнал с его выхода через дополнительный элемент И и через элемент ИЛИ соответст- 15 венно поступает на установочный вход делителя-распределителя 6„ который сдвигает сигналы на своих выходах на один такт, и на соответствующий вход элемента 14 памяти, который ус- 20 танавливает состояние Отсутствие синхронизма".

Формула изобретения

Устройство цикловой синхронизации, содержащее блок опознавания сосредоточенной синхрогруппы, сигнальный вход которого является входом устройства, формирователь тактового сигнала 30

t выход которого соединен с тактовым входом делителя-распределителя, селектирующие входы которого являются выходами устройства, причем управляющий выход делителя-распределителя соединен с входом считывания блока опознавания сосредоточенной синхрогруппы, первый и второй выходы которого соответственно соединены с входом накопителя по входу в синхронизм, 40 который объединен с входом элемента

И, и счетным входом накопителя по выходу из синхронизма, вход сброса и выход которого соответственно соединены с выходом накопителя по входу в синхронизм и с другим входом эле мента И, о т л и ч а ю щ е е с я тем, что, с целью повышения точности синхронизации путем контроля установения синхронизма при приеме контольной информации без увеличения времени вхождения в синхронизм, введены формирователь сигналов сброса, формирователь интервала анализа и последовательно соединенные блок выделения контрольной комбинации, блок контроля фронтов контрольной комбинации, блок стробирования, накопитель ошибок, дополнительный элемент И, элемент ИЛИ и элемент памяти, при этом другой вход элемента памяти соединен с входом сброса накопителя по выходу из синхронизма, к управляющему входу которого подключен выход элемента памяти, вход запрета формирователя сигналов сброса и вход блокировки блока контроля фронтов контрольной комбинации, информационный вход блока выделения контролвной комбинации подключен к сигнальному входу блока опознавания сосредоточенной синхрогруппы, вход считывания которого соединен с соответствующим входом блока выделения контрольной комбинации и с другим входом дополнительного элемента И, а выход элемента И подключен к другому входу элемента ИЛИ, выход которого подключен к установочному входу делителяраспределителя, причем выходы стробирования и контроля формирователя интервала анализа подключены соответственно к другому входу блока стробирования и входу контроля формирователя сигналов сброса, выход которого подключен к входу сброса накопителя ошибок.