Полупостоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано для хранения слов различной длины. Целью изобретения является повышение информационной емкости устройства. Поставленная цель достигается за счет введения первого 8 и второго 9 коммутаторов и формирователя 5 управляющих сигналов. Устройство работает с поляризованными и укороченными словами.2 ил. со ел ;О 00 Ю te. /

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (Ш

А1 (5ц 4 G it С 17/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3861623/24-24

„(22) 28.02.85 (46) 15 ° 12.87. Бюл. Р 46 (72) Г.А. Бородин, И.В.. Суворова

,и Л.Н. Паращук (53) 681.327.66(088.8) (56) Шигин А.Г., Дерюгин A.À. Цифровые вычислительные машины (память

ЭВМ). И.: Энергия, 1976, с. 150, рис. 5 ° 17, с. 161, рис.6.7.

Авторское свидетельство СССР

У 860136, кл. С 1 »7/00, 1979. (54) ПОЛУПОСТОЯННОЕ ЗАПОМИНАЯ)ЩЕЕ

УСТРОЙСТВО (57) Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано для хранения слов различной длины. Целью изобретения является повышение информационной емкости устройства. Поставленная цель достигается sa счет введения первого 8 и второго 9 коммутаторов и формирователя 5 управляющих сигналов. Устройство работает с поляризованными и укороченными словами. 2 ил.

1359802

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано для хранения слов различной длины.

Целью изобретения является повышение информационной емкости устройства.

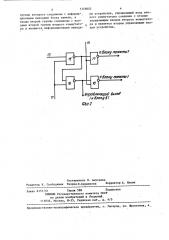

На фиг. 1 представлена структурная схема устройства; на фиг. 2— реализация формирователя управляющих сигналов.

Полупостоянное запоминающее устройство с перестраиваемой структурой содержит блок 1 памяти, который имеет адресные входы первой 2 и второй

3 группы и входы 4 управления, формирователь 5 управляющих сигналов, первый 6 и второй 7 селекторы, первйй 8 и второй 9 коммутаторы, информационный выход 10 устройства, первый управляющий 11, второй управляющий

12, адресный 13, выборки 14 входы.

Формирователь 5 содержит элементы

ИЛИ-НЕ 15-18.

Устройство работает следующим образом.

Режим работы с полнораэрядными словами.

На вход 11 подают сигнал "1".

Вследствие чего формирователь 5, вы" рабатывает сигнал обращения к обоим блокам памяти одновременно. На входы 2 поступает адрес ячейки, к которой производится обращение; На входы

-4 поступает сигнал управления режимов записи-считывания. В режиме записи на вход 12 устанавливают "1", что означает, что полноразрядное слово, поступающее на вход 10 через коммутаторы 9 и 8 (часть разрядов через коммутатор 9, а часть через коммутатор

8), поступает на входы блока 1, причем с выхода коммутатора 8 они поступают через селектор 7. В режиме считывания на вход 12 подают "0", что обеспечивает выдачу информации через коМмутаторы 9 и 8 на входы-выходы, причем на входы коммутатора 9 информация поступает через селектор 6.

Режим работы с укороченными (в данном случае половинными) словами.

На вход 11 подают сигнал "0".

Для того, чтобы полностью использовать информационную емкость количество адресов увеличивается вдвое, что осуществляется формирователем 5, который в зависимости от сигнала на ши10 ется..

Формула изобретения

55 не 13 ("0" или "1") осуществляет стробирование обращения либо к одной, либо к другой половине блока 1 памяти. Информация через селектор 7 с одной группы информационных шин распределяется на две группы для записи в одну и другую половины блока 1 памяти.

При считывании информация поступает только через селектор 6 (с одной и другой групп входов), далее через коммутатор 9 на выход 10. Таким образом, при записи укороченных слов оставшаяся часть разрядов используется для записи другого слова, т.е. количество слов увеличиваПолуцостоянное запоминающее устройство, содержащее блок памяти, информационные выходы которого соединены с входами первого селектора, информационные входы первой группы— с выходами второго селектора, управляющие входы блока памяти являются группой управляющих входов устройства, отличающееся тем, что, с целью повышения информационной емкости устройства, оно содержит первый и второй коммутаторы и формирователь управляющих сигналов, первый информационный вход которого является адресным входом устройства, а второй информационный вход соединен с управляющим входом второго селектора, первым управляющим входом первого коммутатора и является информационным входом устройства, информационные выходы группы формирователя управляющих сигналов соединены с входайи "Обращение" блока памяти, один информационный выход формирова" теля управляющих сигналов соединен с управляющим входом первого селектора, третий информационный вход формирователя управляющих сигналов является входом выборки устройства, выходы первого селектора соединены с входами первого группы второго коммутатора, выходы которого соединены с входами первой группы второго селектора и информационными входами второй группы блока памяти, входы второй группы второго селектора соединены с выходами первого .коммутатора, входы первой

1359802

Составитель Л. Амусьева .

Редактор Н. Слободяник ТехредЛ.Сердюкова Корректор A. Ильин

Заказ 6157/51 Тирах 588 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ухгород, ул. проектная, 4 группы которого соединены с информа-, ционными выходами блока памяти, а входы второй группы соединены с входами второй группы второго коммутато5 ра и являются информационными выходами устройства, управляющий вход второго коммутатора соединен с вторым управляющим входом второго коммутатора и является вторым управляющим входом устройства