Устройство для идентификации линейных стационарных объектов

Иллюстрации

Показать всеРеферат

Изобретение относится к области аналоговой вычислительной техники и может быть использовано для интерпретации экспериментальных зависимостей, / Г-I Г-1 JoKm - Пуск в частности для решения задач технической диагностики, задач коррекции динамических характеристик измерительных и управляющих систем. Цель изобретения - повышение быстродействия устройства. Устройство состоит из интеграторов 1(1), 1(2),,..., 1(2п-2), источника эталонного напряжения 2, инверторов 3(1), 3(2), ..., 3(п+1), перестраиваемых масштабных блоков 4, соединенных в матрицу-размерностью п строк на п+1 столбцов, сумматоров 5(1), 5(2), ..., 5(п), блока управления 6. Значения всех идентифицируемых параметров определяются за время реализации одного тестового сигнала , что и обусловливает повышение быстродействия устройства. I ил. S (Л со :л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК д1 (19) (11) (5)) 4 G 05 В 23/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21 ) 3957360/24-24 (22 ) 23.09.85 (46) 23.12.87. Бюл. Р 47 (71) Институт проблем моделирования в энергетике АН УССР (72) А.Ф. Верлань, Н.A. Максимович и А.Е. 1(оваленко (53) 62-50 (088. 8) (56) Авторское свидетельство СССР

У 703779, кл. 5 05 В 23/02, 1978.

Авторское свидетельство СССР

N- 1038922, кл. G 05 В 23/02, 1983. (54) УСТРОЙСТВО ДЛЯ ИДЕНТИФИКАЦИИ

ЛИНЕЙНЫХ СТАЦИОНАРНЫХ ОБЪЕКТОВ (57) Изобретение относится к области аналоговой вычислительной техники и может быть использовано для интерпретации экспериментальных зависимостей, в частности для решения задач технической диагностики, задач коррекции динамических характеристик измерительных и управляющих систем. Цель изобретения — повышение быстродействия устройства. Устройство состоит из интеграторов 1(1), 1(2), ° .., 1(2n-2), . источника эталонного напряжения 2, инверторов 3(1), 3(2), ..., 3(n+1), перестраиваемых масштабных блоков 4, соединенных в матрицу. размерностью и строк íà и+1 столбцов, сумматоров

5 (1) 5 (2) .. ° 5 (и) блока управления 6. Значения всех идентифицируемых параметров определяются за время реализации одного тестового сигна<0 ла, что и обусловливает повышение быстродействия устройства. 1 ил.

20 ключен к входу r-го инвертора и вторым входам с 4(rn — и+1)-ro no

55

1 136

Изобретение относится к вычислительной технике и может быть использовано для интерпретации экспериментальных зависимостей, в частности для решения задач технической диагностики, задач коррекции динамических характеристик измерительных и управляющих систем.

Целью изобретения является повышение быстродействия устройства.

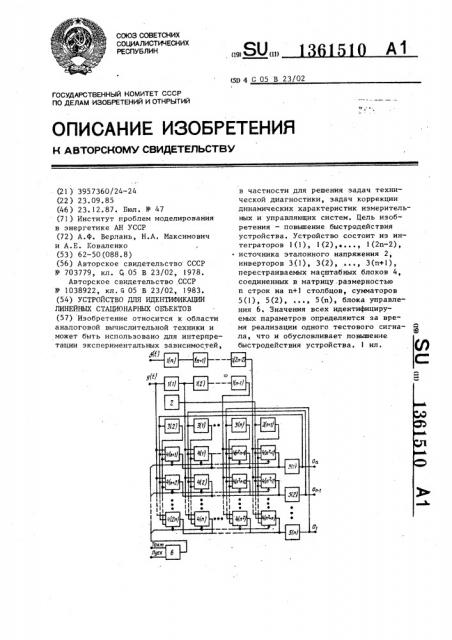

На чертеже приведена структурная схема устройства.

Устройство состоит из 2п-2 интеграторов 1(1), 1(2), ..., 1(2n-2), источника 2 эталонного напряжения, и+1 инверторов 3(1), 3(2), 3(п+1), n + n перестраиваемых масштабных блоков 4(1), 4(2), 4 (n + н), п сумматоров 5 (1), 5 (2), 5 (п) и блока 6 управления, где

n — количество идентифицируемых параметров. Здесь и везде в дальнейшем цифрами в скобках, следующими за номером позиции (цифрой не в скобках) показаны порядковые номера совершенно ! одинаковых по своему техническому исполнению соответственно блоков, узлов, элементов, а просто цифрами в скобках, стоящими около контура блока, узла, элемента — порядковые номера его входов и выходов ° Выход первого интегратора 1(l) подключен к входу второго интегратора 1(2) и к первым входам с 4(1)-го по 4(n)-й перестраиваемых масштабных блоков, первый вход устройства (вход тесто. вого сигнала y(t)) подключен к вхо. ду первого интегратора 1(1) и к первым входам с 4(n+1)-го по 4(2n)-й перестраиваемых масштабных блоков, выход каждого следующего 1(i)-ro интегратора до 1(п-2)-ro включительно подключен к входу 1(i+I)-ro интегратора и первым входам с 4(in+1)-го по 4(in+n)-й перестраиваемых масштабных блоков, выход 1(n-1)-ro интегратора подключен к первым входам с

4(n -n+1)-го по 4(n )-й перестраиваz емых масштабных блоков, второй вход устройства (вход реакции объекта

f(t) подключен к первым входам с

2 а

4(n +l)-го по 4(n +n)-й перестраиваемых масштабных блоков через последовательно соединенные с )(и)-ro no

1(2п-2)-й интеграторы, выход источника 2 эталонного напряжения подключен к вторым входам с 4(n +1)- о по

2

4(n +n)-й перестраиваемых масштабных

15lO

2 блоков, выход каждого 3(j)-го инвертора (j = О, и+1) подключен к третьим входам с 4(jn — n +1)-го по

4 (jn)-й перестраиваемых масштабных блоков, и+1 входов каждого 1-го сумматора (1 = l,n) подключены соответственно к выходам 4(nm + 1) = x(m =

= O,n) перестраиваемых масштабных блоков, выход первого сумматора 5(1) подключен к входу второго инвертора

3 (2) и к вторым входам с 4 (n+1)-ro по 4(2n)-й перестраиваемых масштабных блоков, выход второго сумматора

5(2) подключен к входу первого инвертора и вторым входам с первого

4(1) по 4(n)-й перестраиваемых масштабных блоков, выход каждого следующего r-ro сумматора (r = 3,n) под4(rn)-й перестраиваемых масштабных блоков, выход каждого сумматора является выходом устройства, каждыи

S-й выход блока управления (S = 1 n) подключен к управляющим входам (nm +

+ S) = х (m = On} перестраиваемых масштабных блоков, Устройство работает следующим образом.

Импульс запуска нПуск поступает на соответствующий вход блока 6 управления, запускает тактовый генератор и формирователь тестового сигнала y(t). Блок управления распределяет тактовые импульсы на свои выходы в соответствии с их порядковым номером, Первый тактовый импульс поступает на первый его выход, второй тактовый импульс — на второй его выход и т.д., последний тактовый импульс на последний его выход. По окончании каждого S-го тактового импульса (S

l,п) в соответствии с величиной и знаком напряжения на первых входах устанавливаются коэффициенты передачи с второго или третьего входа на выход (nm + S) = x(m = O,n) перестраиваемых масштабных блоков. Длительность одного тактового импульса в и раз меньше длительности тестового сигнала у(t). По окончании последнего тактового импульса в соответствии с законами Кирхгоффа распределение потенциалов в устройстве определяется системой линейных алгебраических уравнений и а; — А; = -Е,F + а./k (1) ъ!

1361510 о О о где а, — выходные напряжения сумматоров 5; 1 — коэффициенты усиления сумматоров 5; E, — напряжение источника 2 эталонного напряжения, его величина однозначно определяется динамическим диапазоном операционных усилителей сумматоров 5. Полагая

1: ж, Е, = 1 и и-1 раз дифферен- цируя (1), получаем дифференциальное уравнение (n-1)-го порядка и

+a;d y(t) dt = f(t), которое является исходнои математической моделью идентифицируемого объекта.

Таким образом, цель изобретения достигается тем, что все идентифицируемые параметры в устройстве огределяются за время реализации одного тестового сигнала в то время, как в известных устройствах. используется несколько реализаций тестового сигнала. б о р м у л а изобретения

Устройство для идентификации линейных стационарных объектов, содержащее источник эталонного напряжения, первый и второй сумматоры, первый и второй инверторы, первый, второй и третий перестраиваемые масштабные блоки, первый, второй, третий, четвертый и пятый интеграторы, блок управления, первый, второй и третий выходы которого подключены к управляющим входам соответственно первого, второго и третьего перестраиваемых масштабных блоков, выход первого интегратора подключен к первому входу первого перестраиваемого масштабного блока, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, оно содержит и-2 сумматоров, и-1 инверторов, n +

+ n — 3 перестраиваемых масштабных блоков, 2n †. 7.интеграторов, где n— количество идентифицируемых параметров, выход первого интегратора подключен к входу второго интегратора

ВНИИПИ Заказ 6281/46

Произв.-полигр. пр-тие, и к первым входам с второго по и-й перестраиваемых масштабных блоков, первый вход устройства подключен к входу первого интегратора и к первым входам с (и+1)-го по 2п-й перестраиваемых масштабных блоков, выход каждого следующего i-го интегратора до (n-2)-ro включительно подключен к входу (i+1)-го интегратора и первым входам с (in+I)-ro по (in+n)-й перЪстраиваемых масштабных блоков, выход (п — 1)-го интегратора подключен к первым входам с (п — n + 1)-го по п -й

2 2 перестраиваемых масг.табных блоков, второй вход устройства подключен к г 2 первым входам с (n +1)-го по (n +n)-й перестраиваемых масштабных блоков через последовательно соединенные с и-го по (2n-2)-й интеграторы, выход источника эталонного напря)ения под 2 ключен к вторым входам с (n +1)-го L по (n +n) é перестраиваемьж масштабных блоков, выход каждого j-ro инвер25 тора подключен к третьим входам с (jn. — n + 1)-ro no jn-й перестраиваемых масштабных блоков, и+1 входов

1-го сумматора подключены соответственно к выходам (пт + 1) = х (т = О,n) перестраиваемых масштабных блоков, выход первого сумматора подключен к входу второго инвертора и к вторым ! входам с (n+1 )-го по 2п-й нерестраиваемых масштабных блоков, выход второго сумматора подключен к входу первого инвертора и вторым входам с первого по п-й перестраиваемых масштабных блоков, выход каждого следующего r-го сумматора подключеч к

4р входу r-го инвертора и вторым входам с (rn-и+1)-го по rn-й перестраиваемь)х масштабных блоков, выход каждого сумматора является выходом устройства, первый выход блока управления подклю45 чен к управляющим входам (пш+1)=х (m = l,n) перестраиваемых ма<— штабных блоков, второй выход блока управления подключен к управляющим входам (пт+2)=х (т = l,п) перестраиваемых масштабных блоков, третий выход блока управления подключен к управляющим входам (nm+3)=x (m=1,n) перестраиваемых масштабных блоков, каждый следующий S-й выход блока управления подключен к управляющим

:выходам (nm + S)=x (m = O,n) перестраиваемых масштабных блоков.

Тираж 863 По писное

r Ужгород, ул. Проектная,р 4