Устройство для синхронизации памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для построения унифицированных блоков синхронизации запоминающих устройств. Цель изобретения - упрощение устройства. Устройство содержит реверсивный счетчик 1, дешифратор 3, элементы И 4, элементы 5 задержки, блок 6 элементов ИЛИ,элемент И-НЕ 9, элемент И 10, элемент ИЛИ-НЕ 11, первый 16 и второй 17 элементы ЗАПРЕТ. Устройство может работать в режиме настройки и в рабочем режиме. Режим настройки заключается в подборе элемента 5 задержки, обеспечивающего формирование временной диаграммы работы памяти с максимально возможным быстродействием. 1 ил. €

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (51) 4 G 06 F 1/04

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

5 г

ГОСУДАРСТ8ЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4111365/24-24 (22) 16.05.86 (46) 23.12.87. Бюл. 1Ф 47 (72) Н.Д.Ткаченко, Б.И.Ермишкин, П.Е.Ливитчук, И.А.Скоков и А,В,Арская (53) 681 ° 327 (088.8) (56) Папернов А.А. Логические основы

ЦВТ. — М.: Советское радио, 1972, с. 42-60.

Авторское свидетельство СССР

Ф 1101805, кл. G 06 F 1/04, 1982. (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ

ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть ис„„SU„„1361528 А 1 пользовано для построения унифицированных блоков синхронизации запоминающих устройств. Цель изобретения — упрощение устройства. Устройство содержит реверсивный счетчик 1, дешифратор 3, элементы И 4, элементы

5 задержки, блок 6 элементов ИЛИ,элемент И-НЕ 9, элемент И 10, элемент

ИЛИ-НЕ 11, первый 16 и второй 17 элементы ЗАПРЕТ. Устройство может работать в режиме настройки и в рабочем режиме. Режим настройки заключается в подборе элемента 5 задержки, обеспечивающего формирование временной диаграммы работы памяти с максимально возможным быстродействием. 1 ил.

1 i 36152

Изобретение относится к вычислительной технике и может быть использовано для построения унифицированных блоков синхронизации запоминаюВ щих устройств °

Цель изобретения — упрощение устройства.

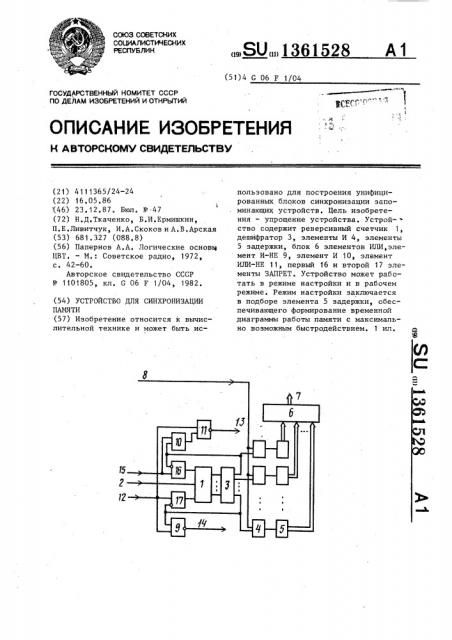

На чертеже изображена структурная схема устройства для синхронизации памяти.

Устройство содержит реверсивный счетчик 1, вход установки в "0" ко-торого является установочным входом

2 уотройства, дешифратор 3, группу элементов И 4, элемент 5 задержки, блок 6 элементов ИЛИ, выходы которого являются выходами 7 синхронизации устройства, тактовый вход 8 которого соединен с одним из выходов элементов И 4. Устройство также содержит элемент И-HE 9, элемент И 10, элемент ИЛИ-HF. 11. Устройство имеет вход

12 "Неисправность памяти", выход 13

"Конец настройки памяти", выход 14 индикации неисправности памяти, вход

15 "Исправность памяти". Устройство также содержит первый 16 и второй 17 элементы ЗАПРЕТ.

Устройство может работать в режиме ЗО настройки и в рабочем режиме, пульса на вход 15 содержимое реверсивного счетчика вновь увеличивается на единицу.

Таким образом, в режиме настройки временная диаграмма ОЗУ постоянно сжимается и, следовательно, увеличивается его быстродействие. Процесс заканчивается установкой оптимальной для данных условий временной диаграммы, Если величины задержек каждого из элементов 5 задержки выбраны достаточно большими и обеспечивают правильное функционирование памяти, то имеет место успешное окончание тестирования при формировании временной диаграммы с помощью последнего элемента 5 задержки.

В этом случае во избежание переполнения реверсивного счетчика 2 его суммирующий вход блокируется сигнаВ начале режима настройки на установочный вход 2 устройства подается сигнал, обнуляющий реверсивный счетчик 1, при этом на старшем выходе дешифратора 3 пдявляется низкий потенциал, а на младшем выходе — высокий, таким образом, на выходе дешифратора устанавливается код, стробирующий элемент И 4.

Затем с помощью 3ВМ или средств встроенного контроля (не показаны) начинается тестирование накопителя, при этом на вход 8 устройства периодически поступают импульсы запуска, 4> которые через элемент И 4 проходят на вход элемента 5 задержки. Величины задержек последнего рассчитываются на наиболее неблагоприятные условия работы оперативного запоминающего устройства (ОЗУ), поэтому на выходах 7 элементов ИЛИ 6 формируется последовательность синхронизирующих сигналов, обеспечивающая функционирование памяти с достаточным запасом по временным параметрам. По окончании тестирования в устройство выдается положительный импульс, причем в случае правильного прохождения тес8 2 та он поступает на вход 15, а в случае обнаружения ошибки — на вход 12.

Если положительный импульс поступает на вход 12, то через элемент И-НЕ 9 он выдается на выход 14 устройства, как признак неисправности накопителя, и через элемент ИЛИ-НЕ 11 — на выход

13, как признак конца настройки.

Выдача этих .двух сигналов свидетельствует о наличии в памяти неисправности, не зависящей от его временной диаграммы, Если положительный импульс поступает на вход 15, то он проходит элемент ЗАПРЕТ 16 и увеличивает на единицу содержимое реверсивного счетчика 1, в результате чего на младшем выходе дешифратора 3 появляется высокий потенциал, т.е. на выходах дешифратора 3 устанавливается код, стробирующий элемент И 4.

Затем вновь начинается тестирование памяти, причем импульсы запуска проходят в этом случае через следующий элемент И 4 на вход следующего элемента 5 задержки. Поскольку величины задержек последнего выбираются несколько меньшими, чем у предыдущего элемента, то на выходах 7 вырабатывается более сжатая последовательность синхронизирующих сигналов. Если после завершения второго тестирования положительный импульс поступает на вход 12, то он проходит "через второй элемент ЗАПРЕТ 17 и возвращает счетчик в исходное состояние. Одновременно с выхода 13 устройства выдается признак конца настройки. В случае поступления положительного имФормула изобретения

Устройство для синхронизации памяти, содержащее реверсивный счетчик, дешифратор, группу элементов И, блок элементов ИЛИ, элементы задержки, элемент И-НЕ, элемент И и элеСоставитель В.Рудаков

Редактор В,Бугренкова Техред M.Äèäûê. Корректор А. Тяско

Заказ 6283/47 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб, д» 4/5

Прбизводственно-полиграфическое предприятие, r. Ужгород, ул, Проектная, 4 з 13 лом с младшего выхода дешифратора 3, а положительный импульс, пришедший на вход 15, через элементы И 10 и

ИЛИ-НЕ 11 проходит на выход 13 как признак конца настройки.

Появление признака конца настройки на выходе 13 свидетельствует о готовности ОЗУ к работе, и с этого момента устройство переходит в рабочий режим. При изменении условий процесса вычислений может возникнуть необходимость в переходе на новую временную диаграмму. Тогда вновь необходимо провести тестирование накопителя. Во избежание потери данных это можно сделать посредством считывания всех ячеек памяти и одновременной их проверки с помощью дополнительных контрольных разрядов в кодовом слове. При использовании памяти на динамических запоминающих микросхемах специальных затрат времени на контрольное считывание как правило не требуется, так как в этом случае оно может быть совмещено с режимом регенерации. После завершения контрольного считывания всех ячеек, как и в режиме настройки, на входы 1 и 12 устройства подается положительный импульс, меняющий состояние реверсивного счетчика 1.

Об установке временной диаграммы, соответствующей новым условиям работы, свидетельствует выдача признака конца настройки с выхода 13.

61528 4 мент ИЛИ- НЕ, причем выходы разрядов реверсивного счетчика подключены к входам дешифратора, выходы которого

5 соединены с первыми входами элементов И группы, вторые входы которых объединены и являются тактовым входом устройства, выходы элементов И подключейы к входам соответствующих элементов задержки, выходы которых соединены с соответствующими входами блока элементов ИЛИ, выходы которого являются выходами синхронизации устройства, вход установки в "0" реверсивного счетчика является установочным входом устройства, первые входы элемента ИЛИ-HE и элемента И-НЕ объединены и являются входом "Неисправность памяти" устройства, второй вход элемента ИЛИ-НЕ подключен к выходу элемента И, первый вход которого является входом "Исправность памяти" устройства, выходы элемента ИЛИ-НЕ и элемента И-НЕ являются соответственно выходом "Конец настройки памяти" и выходом индикации неисправности памяти, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, в него введены два элемента ЗАПРЕТ,причем управляющий вход первого элемента ЗАПРЕТ и второй вход элемента И подключены к старшему выходу дешифратора, выход первого элемента ЗАПРЕТ подключен к суммирующему входу реверсивного счетчика, вычитающий вход ко35 торого соединен с выходом второго элемента ЗАПРЕТ, второй вход элемента И-НЕ и управляющий вход второг"о элемента ЗАПРЕТ соединены с младшим

40 выходом дешифратора, информационные входы первого и второго элементов

ЗАПРЕТ соединены соответственно с входом Исправность памяти" и входом

"Неисправность памяти" устройства.