Микропрограммный автомат

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и микроэлектроники и предназначено для цифровой обработки информации. Цель изобретения - повышение быстродействия устройства . Автомат содержит регистр 1 адреса , блок 2 памяти, регистр 3 и блок 4 синхронизации. Цель достигается за счет изменения структуры блока синхронизации. Эти изменения позволяют использовать в цикле работы автомата часть или всю вычислительную информацию из предыдущего цикла его работы. 3 ил. Вмды /V ВыАоды Г7С С СО СГ No-i. Сл сд

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (И) А1

@ О /

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21 ) 3986889/24-24 (22) 03.10.85 (46) 23.12.87. Бюл. М 47 (71) Могилевскии машиностроительный институт (72) Б.А.Вислович (53) 681.325(088 ° 8) (56) Титце У., Шенк К. Полупроводниковая схемотехника.-M.:Nèð, 1983, с.344, рис.20.1.

Клингман Э. Проектирование микропроцессорных систем.-N.:Ìèð, 1980, с.б3, рис,3.7. (50 4 О 06 У 9 22 9 00 (54) МИКРОПРОГРАММНЫЙ АВТОМАТ (57) Изобретение относится к области вычислительной техники и микроэлектроники и предназначено для цифровой обработки информации, Цель изобретения — повышение быстродействия устрой. ства. Автомат содержит регистр l адреса, блок 2 памяти, регистр 3 и блок 4 синхронизации. Цель достигается за счет изменения структуры блока синхронизации. Эти изменения позволяют использовать в цикле работы автомата часть или всю вычислительную информацию из предыдущего цикла его работы. 3 ил.

13

Изобретение относится к вычислительной технике и микроэлектронике и предназначено для цифровой обработки ,информации.

Цель изобретения — повышение быст, родействия устройства.

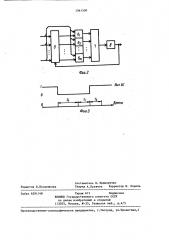

На фиг.1 изображена структурная схема микропрограммного автомата; на фиг.2 — структурная схема блока синхронизации; на фиг.3 — временная диаграмма изменения выходного сигнала блока синхронизации.

Автомат (фиг.1) содержит регистр ) адреса, блок 2 памяти, регистр 3 и блок 4 синхронизации.

Блок синхронизации (фиг.2 } содержит регистр 5, группу элементов

ИСКЛЮЧАЮЦЕЕ ИЛИ б,, 6,... б „,, m — чис— ло входных сигналов автомата, элемент ИЛИ 7 и генератор 8 синхроимпульсов. i

На временной диаграмме изменения выходного сигнала блока синхронизации (фиг.3) обозначены: T — время чтения информации из блока памяти;

Т„ — минимальная длительность синхроимпульса.

Автомат работает следующим образом.

В начальный момент времени автомат находится в исходном положении.

Регистр адреса и регистр автомата, а также регистр блока синхронизации установлены в нулевое состояние, Выходной сигнал генератора синхроимпульсов имеет нулевое значение и раз.решает прием информации в первую ступень триггеров регистра автомата. В следующий момент автомат запускается и на выходе генератора синхроимпульсов устанавливается сигнал, соответствующий уровню логической единицы.

Этот сигнал разрешает прием вектора входных сигналов на регистр адреса, который представляет собой одноступен чатый регистр, а также прием вектора входных сигналов в первую ступень регистра блока синхронизации. При этом на выходах регистра адреса присутствует вектор входных сигналов автомата, а на выходах регистра блока синхронизации — предшествующий ему вектор. Если эти векторы совпадают, то действия, необходимые дпя обработки

61550

55 вектора входных сигналов, автоматом .уже выполнены и автомат находится в состоянии ожидания. В противном слу- чае генератор синхроимпульсов запускается и блокирует регистр автомата на время выполнения указанных действий. Если изменение вектора входных сигналов произошло тогда, когда автомат находился в состоянии ожидания, то время реакции автомата равно нулю.

Если же изменение произошло во время блокировки регистра автомата, то время реакции не превышает величину (>д+ > ) °

Формула изобретения

Микропрограммный автомат, содержащий регистр адреса, блок памяти, регистр и блок синхронизации, причем вход автомата соединен с информационным входом регистра адреса, выход которого соединен с входом старшей части адреса блока памяти, вход младшей части адреса которого соединен с выходом регистра, информационный вход которого соединен с выходом кода адреса блока памяти, выход кода микроопераций которого является выходом автомата, выход блока синхронизации соединен с синхровходами регистра и регистра адреса, о т л и ч а ю щ и и с я тем, что, с целью повышения быстродействия устройства, выход регистра адреса соединен с группой входов задания режима блока синхронизации, причем .блок синхронизации содержит регистр, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент ИЛИ и генератор синхроимпульсов, причем информационные входы регистра блока синхронизации и первые входы элементов ИСКЛЮЧАЮЦЕЕ ИЛИ группы соединены с соответствующими входами группы входов за,дания режима блока, вторые входы элементов ИСКЛЮЧАЮЦЕЕ ИЛИ группы соединены с выходами регистра блока синхронизации, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы соединены с входами элемента ИЛИ, вход которого соединен с входом запуска генератора синхроимпульсов, выход которого соединен с выходом блока синхронизации и синхровходом регистра блока синхронизации.

1361550

Фиг.2

8их.K

Яремя

Фиг.3

Составитель В. Криворучко

Техред А.Кравчук Корректор Н. Король

Редактор В. Бугренкова

Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д.4/5

Заказ 6291/48

Производственно-полиграфическое предприятие, r.Óæãîðîä, ул,Проектная,4