Устройство для контроля умножения по модулю три

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для обнаружения неисправностей арифметических устройств вычислительных машин при выполнении операции умножения нормализованных двоичных кодов. Цель изобретения - повьппение быстродействия устройства. Сомножители поступают на регистр 1 множиif теля и регистр 3 множимого, С помощью блока 2 анализа разрядов множителя и группы 4 узлов свертки по модулю три блоки формирования контрольного кода группы 5 формируют контрольные слова частичных произведений, которые складываются на шестиразрядном сумматоре 6, Результат сложения шестиразрядного сумматора 6 сворачивается узлом 7 свертки по модулю три и складывается на втором сумматоре 8 по модулю три с кодом свертки по модулю три регистра 3 множимого. На первом сумматоре 9 по модулю три формируется остаток по модулю три произведения . Выходные коды первого и второго сумматоров 9, 8 по модулю три сравниваются в блоке 10 сравнения, выход исправления которого является выходом устройства, 2 з.п,ф-лы, 4 ил. 0 (Л 00 05 ел сд 05 IPut.1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)4 6 06 Г 11

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4016690/24-24 (22) 03.02.86 (46) 23.12.87. Бюл. N - 47 (72) 10.С. Варакин (53) 681.3(088.8) (56) Патент СНА У 3873820, кл. G 06 F 11/08, опублик. 1976.

Авторское свидетельство СССР

N - 595737, кл. G 06 F 11/08, 1978. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УМНОЖЕНИЯ ПО МОДУЛЯ ТРИ (57) Изобретение относится к вычислительной технике и может быть использовано для обнаружения неисправностей арифметических устройств вычислительных машин при выполнении операции умножения нормализованных двоичных кодов. 1,ель изобретения — повышение быстродействия устройства. Сомножители поступают на регистр 1 множи„„SU„„1361556 А1 теля и регистр 3 множимого. С помошью блока 2 анализа разрядов множителя и группы 4 узлов свертки по модулю три блоки формирования контрольного кода группы 5 формируют контрольные слова частичных произведений, которые складываются на шестиразрядном сумматоре 6. Результат сложения шестиразрядного сумматора 6 сворачивается узлом 7 свертки по модулю три и складывается на втором сумматоре

8 по модулю три с кодом свертки по модулю три регистра 3 множимого. На первом сумматоре 9 по модулю три формируется остаток по модулю три произведения. Выходные коды первого и вто- д рого сумматоров 9, 8 по модулю три Ж сравниваются в блоке 10 сравнения, выход исправления которого является выходом устройства. 2 з.п.ф-лы, 4ил. С

1361556

Изобретсние относится к вычислительной технике и может быть использовано для обнаружения неисправностей арифметических устройств вычисли/ 5 тельных машин при выполнении операции умножения нормализованных двоичных кодов. Целью изобретения является повышение быстродействия устройства.

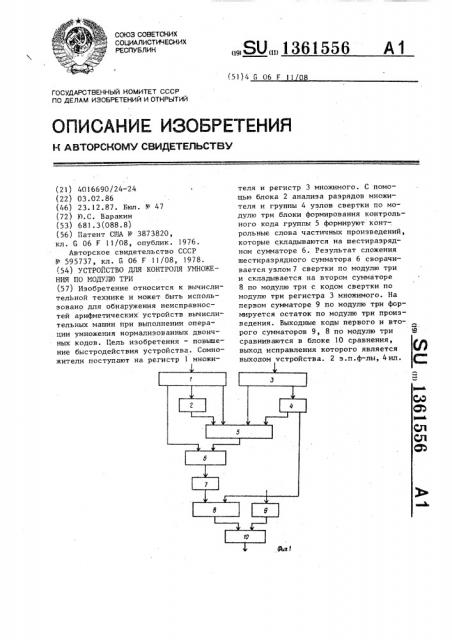

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 функциональная .схеМа блока анализа разрядов множителя и соединение его с регистром множителя; на фиг. 3 схема подключения узлов свертки rpyriпы к выходам регистра множимого; на фиг. 4 — функциональная схема блока формирования контрольного кода группы и подключение его к другим узлам устройства.

Устройство (фиг. 1) содержит регистр 1 множителя, блок 2 анализа разрядов множителя, регистр 3 множимого, группу 4 узлов свертки по мо- 25 дулю три, группу 5 блоков формирования контрольного кода, шестиразрядный сумматор 6, узел 7 свертки по мо— дулю три, второй сумматор 8 по модулю три, первый сумматор 9 по модулю три, 30 блок 10 сравнения.

Блок 2 анализа разрядов множителя (фиг. 2) содержит элемент И 11, две группы элементов И-ИЛИ 12 и 13.

Блок 5 формирования контрольного кода группы содержит элементы И 14 и

15, элементы ИЛИ-.НЕ 16 и 17, элемент

HE 18 и группу 19 полусумматоров.

Устройство для контроля умножения по модулю три работает следующим об- 40 разом.

В регистр 1 множителя и регистр 3 множимого поступают коды сомножителей. В блоке 2 анализа разрядов множителя и с помощью элементов И-ИЛИ 12 и 13 первой и второй групп и элемента И 11 формируются управляющие сигналы наличия и отсутствия частного сдвига (на фиг. 2 обозначены для удобства сигналами С,. и HC,.).

Выходы старших (К-1) разрядов регистра 3 множимого (кроме самого старшего ) соединены с входами первого узла свертки по модулю три группы 4 (К вЂ” количество разрядов первого час55 тичного произведения, участвующих в формировании результата умножения) .

На входы каждого последующего узла свертки по модулю три группы 4 добавляются выходы двух очередных разрядов регистра 3 множимого к тем выходам, которые подключены к входам предыпущего узла.

B блоках формирования контрольного кода группы 5 формируется контрольное слово для каждого частичного произведения. Так, например, для первого частичного произведения код с выхода первого узла свертки по модулю три группы 4 передается на выходы элемента НЕ 18 и полусумматоров группы 19 первого блока формирования контрольного кода группы 5, образующие выходы этого блока, без сдвига при наличии сигнала HCI со сдвигом на один разряд влево при наличии сигнала CI, прямо или инверсно через второй и третий полусумматоры группы 19 в зависимости от значения сигнала на выходе второго разряда регистра 1 множителя. В случае передачи кода свертки по сигналу Cl в младший разряд первого контрольного кода вдвигается

Аналогично контрольные слова формируются для последующих частичных произведений. Контрольные слова сумM мируются на — -входовом шестиразряд2 ном сумматоре 6, на входы переносов которого в младший разряд поступают сигналы с выходов всех 2 t-x раэряM-К дов регистра 1 множителя (— — — + 1 <

2 (— -) .

Эти сигналы учитывают единицу дополнительного кода у частичных произведений, все разряды которых участвуют в формировании результата. умножения. Результат сумматора 6 сворачивается узлом 7 свертки по модулю три, результат которой в свою очередь складывается на втором сумматоре 8 по модулю три со сверткой множимого. Далее в блоке 10 сравнения результат второго сумматора 8 по модулю три сравнения со сверткой по модулю три результата умножения, получаемой на выходе первого сумматора 9 по модулю три.

Рассмотрим конкретный пример контроля умножения. Пусть множитель имеет код 110000, а множимое — 111111.

Все группы зарядов множителя, кроме последней, сформируют в блоке 2

13615

+ 0100!1 анализа разрядов множителя упранляюшие сигналь1 НС; С, равные нулям.

Для старшей группы разрядов в блоке анализа разрядов множителя сформи5 руются сигналь НС=1; С=О; а=1.

В блоке формирования сверток разрядон множимаго для данных кодов сформируются 1СВ=1 и 2СВ=О для каждой свертки, 10

Во всех блоках формирования контрольного кода группы 5, кроме последнего, с помощью управляющих сигналов

НС=О; С=О; а=О сформируются контрольные слова, равные по значению 100000.

Б последнем блоке формирования контрольного кода частичного произведения с помощью управляющих сигналов НС=1: С=О; а=-1 сформирупотся контрольные слова, равные по значению

010011

Учить вая, что на входы переносов в младший разряд многовхадавого шестиразрядного сумматора 6 поступает сигнал а=1, формируемый н последнем блоке формирования контрольного кода группы 5, результат на выходе шестиразрядного сумматора 6 будет иметь следующее sначение

1010100 35

Свертка результата шестиразрядного сумматора 6 равна для данного случая значению 00 на выходе узла 7

I свертки по модулю три).

На сумматоре 8 по модулю три код 40

00 суммируется со значением СВИ=01, н результате на выходе формируется код 01, который и является контрольным кодом устройства.

В устройстве умножения по анало- 45 гичнь м управляющим сигналам НС; С формируются частичные произведения н дополнительном коде.

0 О О О О О О О

О 0 0 0 0 0 0 0 50

+11000000

1 1 1 l 1 1 1

1, 1 О 1 1 1 1 О 1

Свертка результата умножения с учетом переноса из старшего разряда результата имеет значение 01, т.е. совпадает с результатом устройства для контроля умножения по модулю три.

56 4

В данном примере младшие разряды частичных произведений (отмечены знаком Х) могут быть отброшены, при этом в устройстве контроля умножения все равно будет сформирована правильная контрольная свертка, равная свертке усеченного результата умножения.

4|ормyлаиз обретения

1. Устройство для контроля умножения по модулю три, содержащее регистры множителя и множимого, первый сумматор по модулю три и блок сравнения, причем выход первого сумматора по модулю три соединен с первь м информационным входом блока сравнения, информацианнь е входы регистров множителя и множ:мого являются соответственно входами множителя и множимаго устройства, информационный вход первого сумматора по модулю три является входом произведения устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, н него введены узел свертки по модулю три, группа узлов свертки по модулю три, в-.îðîé сумматор по модулю три, шестиразрядный сумматор, блок анализа разрядов множителя, входы каждого J ãо узла свертки кода и группа блоков формирования контрольного кода, причем информационный выход регистра множителя соединен с информационным входом блока анализа разрядов множителя, информационные входы каждого j-ro узла свертки и по модулю три группы соединены с прямыми выходами всех р-х разрядов регистра

m-k множимого (1 j < ----- + 1 2 < р 4

Э k + 2 (J -1) ), прямые выходы всех

t-х разрядов регистра множителя соединены с соответствующими входами переноса шестиразрядного сумматора

m-k П1 (----- + 1 и ---) информационный

2 2 выход шестиразрядного сумматора соединен с входом узла свертки по модулю три, выход которого соединен с первым информационным входом второго сумматора по модулю три, второй информационный вход которого соединен

m-k с выходом (----- + 1)-ro узла сверт2

56 6

5 13615 ки по модулю три группы, выход второго сумматора по модулю три соединен с вторым информационным входом блока сравнения, выход несравнения которого является выходом неисправности устройства, каждый r-й информационный выход группы всех формирователей контрольного кода группы соединен с соответствующим входом слагаемого

r"го разряда шестиразрядного сумма- 1д тора, выход каждого узла свертки по модулю группы соединен с информационным входом соответствующего формирователя контрольного кода группы, входы признака дополнения и признака инверсии каждого t-го формирователя конITl трольного кода группы (1- (---) соеди2 нены с прямыи выходом (k+1+2 (f,-1)) -ro gp разряда и прямым выходом 2f-ro разряда регистра множителя, вход признака сдвига первого формирователя контрольного кода группы соединен с прямыи выходом первого разряда регистра 25 множителя, каждый i-й выход признака сдвига группы блока анализа разрядов множителя соединен с входом признака сдвига (i+1)-го формирователя контрольного кода группы, выходы призна- 3р .isa отсутствия сдвига группы блока анализа разрядов множителя соединены с входами признака отсутствия сдвига соответствующего формирователя контрольного кода группы. 35

2. Устройство по п. 1, о т л и— ч а ю щ е е с я тем, что блок анализа разрядов множителя содержит элемент И и две группы элементов

И-ИЛИ, причем первый и второй входы элемента И соединены соответственно с инверсным входом первого разряда и прямым входом второго разряда информационного входа блока, первый вход каждого i-го элемента И-ИЛИ 45 первой группы соединен с прямым входом 2 (i+1)-го разряда информационноro входа блока (1 1 <--- - 1), где

50

M - разрядность регистра множителя, второй и третий входы каждого 1-го элемента И-ИЛИ первой группы соединены с инверсными входами (21+1)-го и 2 i--го разрядов информационного входа блока соответственно, четвертый вход каждого 1-го элемента И-ИЛИ первой группы соединен с инверсным входом 2(i+1)-го разряда информационного входа блока, пятый и шестой входы каждого i-го элемента И-ИЛИ

Ъ первой группы соединены с прямыми входами (2i+1)-ro и 2 i ãî разрядов информационного входа блока соответственно, выход элемента И и выходы элементов И-ИЛИ первой группы образуют группу выходов признаков сдвига группы, первый и второй вход каждого

i-го элемента И-ИЛИ второй группы соединены с прямым входом 21-го и инверсным входом (21+1)-го разрядов информационного входа блока соответственно, третий и четвертый входы каждого i-го элемента И-ИЛИ второй группы соединены с инверсным входом

2i-ro и прямым входом (2i+1)-ro разрядов информационного входа блока, выходы элементов И-ИЛИ второй группы образуют группу выходов признаков отсутствия сдвига блока.

3. Устройство по и. 1, о т л и— ч а ю щ е е с я тем, что блок формирования контрольного кода группы содержит элемент НЕ, два элемента И, два элемента И-ИЛИ и группу полусумматоров, причем выходы элемента НЕ и полусумматоров группы образуют группу информационных выходов блока, вход элемента НЕ объединен с первыми входаии всех полусумиаторов группы и образует, вход признака инверсии блока, первые входы первого и второго элементов И-ИЛИ образуют информационный вход блока, выходы первого и второго элеиентов И и первого, второго элементов И-ИЛИ соединены с вторыми входами первого, второго, третьеro и четвертого полусумматоров группы соответственно, второй вход пятого полусумматора группы объединен с вторыми входами первого и второго элементов И-ИЛИ, первым входом первого элемента И и образу-ет вход признака сдвига блока, первый вход первого элемента И-ИЛИ объединен с третьим входом второго элемента И-ИЛИ, первый вход второго элемента И-ИЛИ объединен с первым входом второго элемента И, третий вход первого элемента

И-ИЛИ объединен с четвертым входом второго элемента И-ИЛИ, вторым входом второго элемента И, и образует вход признака отсутствия сдвига блока, второй вход первого элемента И является входом признака дополнения блока..1361556

Фиг. 2

С2 НС2 С1 1

1361556

Ppj(jr+I)

ТОК

2 ГВ4

Hey

Cf а1 рр (3)

УГВN+2) гсгИ+2) ис2

С2 и 2

Составитель В. Гречнев

РедактоР В. БУгРенкова ТехРед А.Кравчук Корректор А. Зимокосов

Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, E-35, Раушская наб„, д. 4/5

Заказ 6291/48

Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная, 4