Устройство для адресации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике. Цель изобретения - расширение области применения за счет увеличения объема подключаемой оперативной памяти. Устройство содержит К магистралей 1 микроЭВМ, процессор 2, блок 3 непереключаемой памяти, блоки 4 памяти, кo p тaтop 6, дешифратор 7 адреса, регистр 8, согласователи магистралей, формиро ватели старших разрядов адреса. Все блоки 4 памяти имеют одинаковые адреса для процессора 2. Выбор конкретного блока 4 памяти осуществляется занесением номера страницы памяти в регистр 8. 1 табл., 3 ил. Q е (Л z о СП о:

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

4 А1 (19) (11) (бц 4 (з 06 F 12/08

OllMCAHHE ИЗОБРКт Ния

Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ фиг.1

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4098165! 24-24 (22) 26.05.86 (46) 23.12.87. Бюл. 11 47 (71) Каунасский политехнический институт им.Антанаса Снечкуса (72) Э,П.Кумяляускас, В.Ч.Синкявичюс С.И.Дайлиде и К-. В.А.Волкас (531 681.325 (088.8) (56) Фролов Г.И. и др. Автоматизированные системы контроля объектов,—

N.: Высшая школа, 1984 °

МикроЭВМ "Электроника 60", Центральный процессор М2. Техническое описание и инструкция по эксплуатации. 3.852.382.ТО.

Приборы и техника эксперимента, 1985, У 3.

Черняк А.И. Диспетчер памяти для микроЭВМ "Электроника 60". -М., с.98-99. (54) УСТРОЙСТВО ДЛЯ АДРЕСАЦИИ (57) Изобретение относится к вычислительной технике. Цель изобретения— расширение области применения за счет увеличения объема подключаемой оперативной памяти. Устройство содержит К магистралей 1,микроЭВМ, процессор 2, блок 3 непереключаемой памяти, блоки 4 памяти, коммутатор

6, дешифратор 7 адреса, регистр 8, согласователи магистралей, формирователи старших разрядов адреса. Все блоки 4 памяти имеют одинаковые адреса для процессора 2. Выбор конкретного блока .4 памяти осуществляется занесением номера страницы памяти в регистр 8. 1 табл., 3 ил.

1361564

30 соединен с первыми входами с первого 35 по (К+1)-й формирователей старших разрядов адреса, с второго по (К+2)-й выходы шифратора соединены с вторыми входами с первого по (К+1)-й формирователей старших разрядов адреса, 40 соответственно информационные входывыходы и младшие разряды адресного

;входа С-го блока памяти (С=1,...,К+1) соединены с разрядами входа-выхода

Разряды первого выхода шифВыходы шифратора

Страница памяти

Страница .памяти

Г 1 (двоичн. ) ° .. 6 5 4 (дес. ) 3 2

0000

0001 ... 0 0 0

Изобретение относится к вычислительной технике.

Цель изобретения — расширение области применения за счет увеличения объема подключаемой оперативной памяти

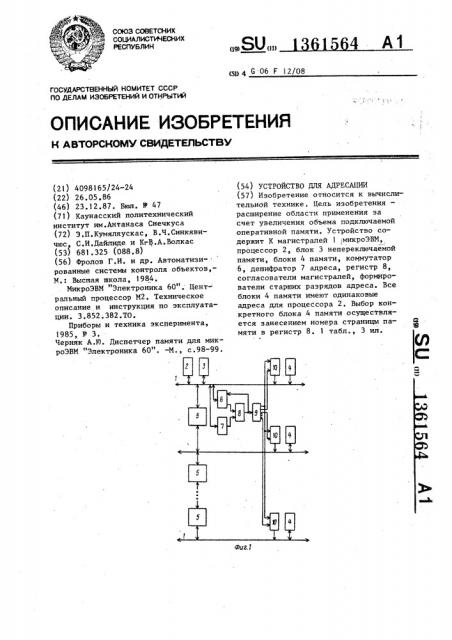

На фиг.1 представлена структурная схема устройства для адресации; на фиг.2 — структурная схема формирователя старших разрядов адреса; на фиг.3 — распределение адресов памяти между блоками памяти.

Устройство содержит (фиг.1) общие .магистрали 1, микроЭВМ, центральный процессор 2, блок 3 непереключаемой памяти, блоки 4 памяти, согласователи 5 магистралей, коммутатор 6, дешифратор 7, регистр 8, шифратор 9 и формирователи 10 старших разрядов адреса.

Формирователь 10 (фиг.2) содержит два элемента И 11 и 12.

Устройство работает следующим образом.

Процессор 2 имеет доступ по магистрали 1 к блоку 3 непереключаемой памяти, который настроен так, что старшие разряды адреса РАД 16 и РАД

17 не влияют на его работу. Блок 3 занимает физические адреса адресного пространства ЭВМ, как показано на фиг.3. Блок 4 памяти содержит три модуля, которые настроены на определенный код дополнительных адресных разрядов РАД 16 и РАД 17 (коды 01, 10 и 11). Код 00 в устройстве не используется ни одним модулем блока

4 и предназначен для выключения всех блоков 4 данной магистрали.

Активизация определенного блока 4 памяти обеспечивается занесением в регистр 8 номера активной страницы памяти. К регистру 8 процессор 2 имеет доступ как для записи, так и для чтения через коммутатор 6. Дешифратор 7 адреса настроен на свободный адрес из зоны адресов внешних устройств, В зависимости от значения номера активной страницы, занесенного в регистр 8, процессору 2 программно доступен один иэ блоков 4 памяти.

Активизация определенного блока

4 происходит согласно таблице.

Формула изобретения

Устройство для адресации, содержащее дешифратор адреса, регистр, коммутатор, блок памяти, вход дешифратора адреса соединен с разрядами адресного входа устройства, выход дешифратора адреса соединен с входом выборки регистра, выход которого соединен с информационным входам коммутатора, информационный вход-выход которого соединен с входом-выходом разрядов данных устройства, выход коммутатора соединен с информационным входом регистра, о т л и ч .а ющ е е с я тем, что, с целью расширения области применения эа счет увеличения объема подключаемой оперативной памяти, в него введены К-блоков памяти, шифратор, (К+1) формирователей старших разрядов адреса, причем выход регистра соединен с входом шифратора, первый вход-выход которого данных и разрядами адресного входа устройства, выходы С-го формирователя старших разрядов адреса соединены со старшими разрядами адресного входа С-ro блока памяти.

1361564

Продолжение таблицы

Разряды первого выхода шифратора 9

Выходы шифрлторл 9

Страница памяти

Страница памяти (двоичн.) ... 6 5 4 3 2 (дес.) 2 1

О 0 О О 1

О О 0 О 1

О О О 1 О

0010

0011

0100

О 1 О

О . 0

0101

О О. О 1 О

0110

О О 1 О

0lll

О О

О

1 О

1000

О О 1 О

1 1 О 0

О 1 О О

О 1 О О

1001

1010

О

1011

1100

РАД16

РАД17 ор рали фиг.2! 361564

Составитель А.Трунов

Техред А. Кравчук

Редактор В.Бугренкова

Корректор Н Король

Заказ 6292/49

Тираж 671

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, r.Óæãîðoä, ул.Проектная, 4