Элемент памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к микроэлектронике и может быть использовано в интегральных схемах запоминающих устройств. Целью изобретения является повьшение быстродействия элемента памяти. Поставленная цель достигается за счет введения узла смещения 4, подключенного к шинам 5, 6 и блокам 2, 3 выборки информации. Шина 5 одновременно является шиной питания триггера, что позволяет не подключать выводы элемента памяти к двум различным шинам выборки и питания . В результате разрядные шины 7, 8 пересекаются с меньшим количеством строчных шин. Емкости разрядных шин уменьшаются, и,следовательно,уменьшается время их перезаряда в режиме выборки. 2 ил. с

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

А1 (19) (11) (51) 4 С l1 С 11/40

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ, (4

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4005485/24-24 (22) 07,01,86 (46) 23.12.87. Бюл. У 47 (71) Московский институт электронной техники (72) В,А.Братов, B.È.Ñòàðoñåëüñêèé, В.И,Суэтинов и Л.Н.Кравченко (53) 681.327,66(088.8) (56) Ohwada К. et all. GaAs 256-bit

static RAM. — Electron. Letters, 1982, v. 18, Р7.

Ino M. et all ° Estimation of

GaAs Static RAM Perfomance. — IEEE

trans, 1982, v. 29, N 7. (54) ЭЛЕМЕНТ ПАМЯТИ (57) Изобретение относится к микроэлектронике и может быть использовано в интегральных схемах запоминающих устройств. Целью изобретения является повышение быстродействия элемента памяти. Поставленная цель достигается за счет введения узла смещения 4, подключенного к шинам 5, 6 и блокам 2, 3 выборки информации.

Шина 5 одновременно является шиной питания триггера, что позволяет не подключать выводы элемента памяти к двум различным шинам выборки и питания. В результате разрядные шины 7, 8 пересекаются с меньшим количеством строчных шин. Емкости разрядных шин уменьшаются, и,следовательно, уменьшается время их перезаряда в режиме выборки. 2 ил.

1 136

Ъ

Изобретение относится к микроэлектронике и может быть использовано в интегральных схемах запоминающих устройств.

Цель изобретения — повышение быстродействия элемента памяти.

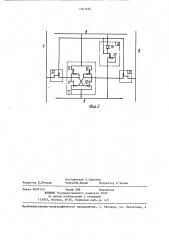

На фиг. t приведена структурная схема элемента памяти, на фиг. 2 электрическая схема элемента памяти.

Элемент памяти содержит триггер блоки 2 и 3 выборки информации, узел 4 смещения, шину 5 выборки, шину 6 нулевого потенциала, две разрядные шины 7 и 8. Триггер 1 выполнен на транзисторах 9-12, узел 4 смещения состоит из транзистора 13 и диода 14.

Транзисторы 9 и 10 триггера 1 являются нормально открытыми, а транзисторы 11 и 12 — нормально закрытыми, транзисторы блоков 2 и 3 выбор- ки — нормально закрытыми, транзистор

13 узла 4 смещения — нормально открытым.

Шина 5 выборки элемента памяти одновременно является шиной питания для триггера 1, что позволяет не подключать выводы элемента памяти к двум различным шинам выборки и питания. В результате разрядные шины 7 и 8 пересекаются с меньшим количеством строчных шин. Емкости разрядных шип уменьшаются, и, следовательно, уменьшается время их перезаряда в режиме выборки.

Элемент памяти работает следующим образом.

В режиме хранения на шине 6 поддерживается нулевой потенциал, на " шине 5 — потенциал U, < U — U где U — напряжение отпирания барьерного перехода U — пороговое напряжение нормально закрытых транзисто1626 ров, Узел .4 -.мещения выдает потенциал, сдвинутый на величину Uz..

I кр Ч> Ь

При этом транзисторы блоков 2 и 3 выборки оказываются запертыми, В режиме выборки потенциал на ши» не 5 повышается до величины

10 1выв = 2Пв а на выходе узла 4 — до величины

15 При этом транзисторы блоков 2 и 3 отпираются и подключают выходы триггера 1 к разрядным шинам 7 и 8 соответственно, с которых производится считывание информации. При записи

20 на шины 7 и 8 подается записываемая информация.

Формула и э о б р е т е н и я

Элемент памятй, содержащий триггер, вход питания которого подключен к шине выборки элемента памяти, а вход нулевого потенциала — к шине нулевоГо потенциала элемента памяти, 30 два блока выборки, информационные .входы которых соединены с прямым и инверсным выходами триггера соответственно, выходы блоков выборки подключены к прямой и инверсной разрядным шинам элемента памяти соответственно, отличающийся тем, что, с целью повышения быстродействия, элемент памяти содержит узел смещения, первый и второй входы

40 которого подключены к шине выборки и шине нулевого потенциала элемента памяти соответственно, а выход соединен с входами разрешения выборки .первого и второго блоков выборки.

1361626

Составитель С.Королев

Техр ед M. Дидык Корректор С.Черни

Редактор В.Петраш

Заказ 6297/52

Тираж 588 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб.,д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4