Формирователь серий задержанных импульсов

Иллюстрации

Показать всеРеферат

Изобретение может быть использовано в гидрои радиолокации при слежении по дальности. Цель изобретения - повышение точности формирования временной расстановки импульсов и расширение области применения устройства . Формирователь содержит генератор 1 импульсов тактовой частоты, RS-триггер 3, двухвходовый элемент И 4, двоичный счетчик 5, регистр 6 кода задержки и схему 7 сравнения кодов. В устройство введены вычислитель 2 и формирователь 8 импульсов. Наличие формирователя 8 импульсов позволяет уменьпшть триггерный шум выходного сигнала, а также предотвращает появление на выходе устройства ложных импульсов, которые могут возникать в момент перезаписи вычисленного значения кода в регистр 6 кода задержки. 1 з.п. ф-лы, 2 ил. (Л С Ьымд 5 : 55

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) А1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ,(21) 3966624/24-21 (22) 11.11.85 (46) 23.12.87. Бюл. 9 47 (72) В.M.Âoèíà, И.С.Романив и .А.В.Тимченко (53) 621 . 374 (088. 8) (56) Авторское свидетельство СССР

Ф 457158, кл. Н 03 H 9/30, 1974. (54) ФОРМИРОВАТЕЛЬ СЕРИЙ ЗАДЕР)МАННЫХ

ИМПУЛЬСОВ (57) Изобретение может быть использовано в гидро- и радиолокации при слежении по дальности. Цель изобретения — повышение точности формирования временной расстановки импульсов (59 4 Н 03 Н 9/30 Н 03 К 5/156 и расширение области применения устройства. Формирователь содержит генератор 1 импульсов тактовой частоты, RS-триггер 3, двухвходовый элемент

И 4, двоичный счетчик 5, регистр 6 кода задержки и схему 7 сравнения кодов. В устройство введены вычисли-тель 2 и формирователь 8 импульсов.

Наличие формирователя 8 импульсов позволяет уменьшить триггерный шум выходного сигнала, а также предотвращает появление на выходе устройства ложных импульсов, которые могут возникать в момент перезаписи вычисленного значения кода в регистр 6 кода задержки.. 1 з.п. ф-лы, 2 ил.

13

Изобретение относится к цифровым устройствам задержки импульсных сигналов и может использоваться в качестве формирователя опорного сигнала при слежении по дальности, например, в гидро- и радиолокации.

Цель изобретения — повышение точности формирования временной расстановки импульсов и расширение области применения устройства.

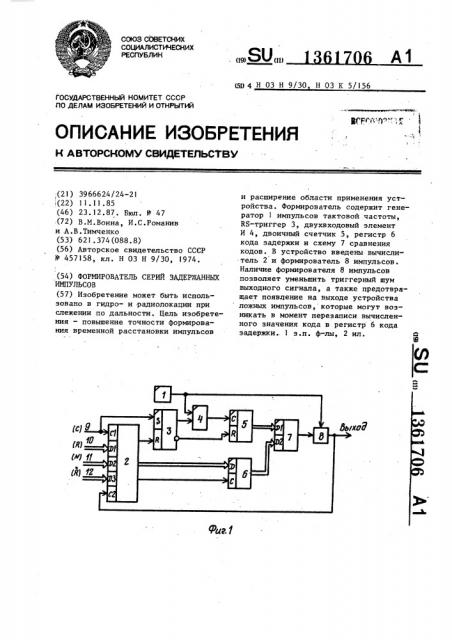

На фиг.l приведена блок-схема предлагаемого устройства; на фиг.2 блок-схема вычислителя.

Формирователь серий задержанных импульсов содержит генератор 1 импульсов тактовой частоты, вычислитель 2, RS-триггер 3, двухвходовый элемент И 4, двоичный счетчик 5, регистр 6 кода задержки, схему 7 сравнения кодов, формирователь 8 импульсов. Кроме того, на фиг.l обозначены шина 9 синхронизации G, шина 10 кода дальности R, шина 11 номера кода N, шина 12 кода скорости R.

Вычислитель 2 содержит дешифратор . 13, двухвходовый элемент ИЛИ 14, счетчик 15, постоянное запоминающее устройство (ПЗУ) 16, сумматор 17.

Генератор 1 тактовых импульсов подключен непосредственно к тактовому входу формирователя 8 импульсов, а через элемент И 4 — к счетному входу счетчика 5. Выходы счетчика 5 соединены с первой группой входов схемы

7 сравнения кодов, вторая группа входов которой подсоединена к выходам регистра 6, а выход через формирователь 8 импульсов соединен с выходом устройства и счетным входом вычислителя 2. Информационный и тактовый выходы вычислителя 2 соединены с соответствующими входами регистра 6, а выход останова — с входом установки в нулевое состояние RS-триггера

3. Первая группа входов вычислителя

2 соединена с шиной 10 кода дальности, вторая — с шиной 12 кода скорости, а третья - с шиной 11 номера кода. Синхронизирующий вход вычислителя 2 и вход установки в единичное состояние RS-триггера 3 соединены с шиной 9 синхронизации. Прямой выход

RS-триггера 3 соединен с вторым входом двухвходового элемента И 4, а инверсный — с входом установки нуля счетчика 5.

В вычислителе 2 шина 10 кода дальности соединена с первой группой

61706 2 входов сумматора 17, шина 12 кода скорости — с первой группой входов

ПЗУ 16, шина 11 номера кода непосред ственно — с второй группой входов

5 блока 16; а через дешифратор 13 — с входами предустановки счетчика 15, информационные выходы которого соединены через третью группу входов ПЗУ

16 с второй группой входов сумматора .

17, выходы которого являются информационными выходами вычислителя 2.

Счетный вход счетчика 15 и первый вход элемента ИЛИ 14 соединены вмес1r те и являются счетным входом вычислителя 2. Вход разрешения предустановки счетчика 15 и второй вход элемента ИЛИ 14 соединены с и;иной 9 синхронизации. Выход элемента ИЛИ 14 является тактовым выходом вычислителя 2, а выход переноса счетчика 15 — выходом останова вычислителя 2.

Устройство работает следующим образом.

25 Пусть в исходном состоянии на шины 10-12 поданы соответствующие коды, в результате чего вычислителем 2 вычислен и подан на информационные входы регистра 6 кода задержки код M

З0 отвечающий заданной дальности, т.е. положению первого выходного импульса, а RS-триггер 3 находится в нулевом состоянии. При этом на инверсном выходе RS-триггера 3 присутствует логическая единица, удерживающая счетчик

5 в нулевом состоянии. Элемент И 4 закрыт, так как на его второй вход подается логический ноль с прямого ю выхода RS-триггера 3.

40 Формирование опорного сигнала заданного вида начинается с прихода запускающего импульса с шины 9 синхронизации. Этот импульс устанавливает RS-триггер 3 в состояние логической единицы, открывая тем самым элемент И 4 и разрешая прохождение импульсов тактовой частоты на вход счетчика 5. Запускающий импульс также поступает на тактовый выход вычислителя 2 и записывает в регистр 6 вычисленное значение кода М . После этого вычислитель 2 переходит к вычислению требуемой задержки для второго импульса выходного сигнала, учитывая поданные на шины 10-12 коды, которые преобразуются вычислителем

2 в величину M, = M + ЬМ,, где

hM — код расстояния между первым и вторым импульсами выходного сигнала. формируется значение кода М,. Запускающий импульс поступает через элемент ИЛИ 14 на тактовый выход вычислителя 2 и на вход разрешения предустановки счетчика 15, записывая в последнем код с выхода дешифратора 13.

Код на выходе счетчика 15 изменяеT выходной код ПЗУ 16, в результате чего на выходе сумматора 17 формируется новое значение кода задержки M

После формирования устройством первого импульса выходного сигнала, который поступает на счетный вход вычислйтеля 2, т.е. на С-вход счетчика

15 и.через элемент ИЛИ 14 на тактовый выход, записывая значение М1 в регистр 6, выходное значение кода

I счетчика 15 уменьшается на единицу.

В результате этого формируется новое значение кода М . Далее вычислитель

2 функционирует аналогично. После записи в регистр 6 кода М„, соответствующего последнему импульсу выходного сигнала, по выходному коду счетчика 15 ПЗУ 16 и сумматор 17 вырабатывают код, который может отвечать начальной дальности, например М . После генерации последнего импульса выходного сигнала счетчик 15 переходит в нулевое состояние, на его выходе переноса генерируется импульс, поступающий через выход останова блока 2 на вход установки нуля RS-триггера 3, устанавливая тем самым в ноль счетчик 5. Генерация импульсов выходного сигнала прекращается, а вычислитель

2 приведен в исходное состояние. !

Таким образом, за счет применения в известном устройстве блоков 2,3 и

8 с соответствующими связями можно повысить точность формирования временной расстановки импульсов и расширить его функциональные возможности.

Формула изобретения

1. Формирователь серий задержанных импульсов, содержащий генератор импульсов, подключенный через двухвходовый элемент И к счетному входу счетчика, выходы которого соединены с первой группой входов элемента

55 сравнения, к второй группе входов ко° торого подсоединены выходы регистра кода задержки, RS-триггер, вход установки в единичное состояние которого соединен с шиной синхронизации, а з 136! 706

Счетчик 5 подсчитывает импульсы тактовой частоты от генератора 1 и через время Т = М,/F, где Р— тактовая частота, выходное значение кода счетчика 5 сравнивается со значением, записанным в регистре 6 кода задержки, и на выходе схемы 7 сравнения появится импульс, по которому формирователь 8 импульсов сформирует первый выходной импульс заданной длительности. Этот импульс поступает на счетный вход вычислителя 2 и через последний на его тактовый выход ° В результате этого в регистр 6 записы- 15 вается код, значение которого соответствует временному положению второго импульса выходного сигнала М<, а блок 2 переходит к вычислению кода временного положения третьего импуль- 20 са выходного сигнала.

Счетчик 5 продолжает накапливать импульсы от генератора 1 и в момент времени Т, = M,/F на выходе формирователя 8 импульсов генерируется вто- 25

/ рой импульс выходного сигнала. Далее работа устройства повторяется аналогично. После формирования последнего импульса выходного сигнала вычислитель 2 не передает выходной импульс 30 на тактовый выход, а формирует импульс по выхбду останова, который устанавливает RS-триггер 3 в нулевое состояние и обнуляет счетчик 5. Таким образом, устройство возвращается в исходное состояние.

Наличие формирователя 8 импульсов позволяет уменьшить триггерный шум выходного сигнала, а также предотвращает появление на выходе устройства 40 ложных импульсов, которые могут появиться в момент перезаписи вычисленного значения кода в регистр 6 кода задержки.

Вычислитель 2 работает следующим образом, Пусть в начальном положении счетчик

15 находится в нулевом состоянии. Дешифратор 13 дешифрирует код N и подает на входы предустановки счетчика

15 код, соответствующий количеству импульсов в выходном сигнале. ПЗУ 16 по нулевому выходному значению кода на выходе счетчика 15 и соответствующим кодам на шинах 11 и 12 подает на вторую группу входов сумматора 17 поправку к заданному по первой группе входов коду дальности.R. В результате этого на выходе сумматора 17

61706 6

2. Формирователь по и.1, о т л ич а ю шийся тем, что вычислитель содержит сумматор, первая группа входов которого является первой группой входов вычислителя, а выходы являются информационными выходами вычислителя, вторая группа входов сумматора соединена с выходами постоянного запоминающего устройства, первая группа входов которого является второй группой входов вычислителя, третья группа входов которого подключена к второй группе входов постоянного запоминающего устройства и через дешифратор — к входам предустановки счетчика, счетный вход которого является счетным входом вычислителя и соединен с первым входом элемента ИЛИ, выход которого является тактовым выходом вычислителя, а другой вход соединен с входом разрешения предустановки счетчика и является синхронизирующим входом вычислите25 ля, информационные выходы счетчика подключены к третьей группе входов постоянного запоминающего устройства, а его выход переноса является выходом останова вычислителя.

5 13 прямой выход соединен с вторым входом двухвходового элемента И, о т— л и ч а ю шийся тем, что, с целью повышения точности формирования временной расстановки импульсов и расширения области применения, в него введены вычислитель, формирователь импульсов и три шины управления, причем первая информационная группа входов вычислителя соединена с первой шиной управления, вторая — с второй шиной управления, а третья — с третьей шиной управления, синхронизирующий вход вычислителя соединен с шиной синхронизации, информационный и тактовый выходы вычислителя соединены с соответствующими входами регистра кода задержки, выход останова вычислителя соединен с входом установки в нулевое состояние RS-триггера, инверсный выход которого соединен с входом установки нуля счетчика, выход элемента сравнения через формирователь импульсов соединен с выходом устройства и счетным входом вычислителя, а выход генератора импульсов дополнительно соединен с тактовым входом формирователя импульсов.

Фие. 1

Составитель А.Титов

Редактор П.Гереши Техред М.Дидык Корректор M.Øàðîøè

Заказ 6303/56

Тираж 900 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r, Ужгород, ул. Проектная, 4