Генератор возвратных последовательностей @ -го порядка

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для генерирования последовательностей весов возвратных последовательностей различного порядка. Цель изобретениярасширение функциональных возможностей за оч-ет генерации весов различных возвратных последовательностей. Генератор содержит п резисторов 1, блок 2 синхронизации, сумматор 3, блок 4 коммутаций и ввода начальных условий, п элементов И, п элементов ИЛИ. Поставленная цель достигается за счет введения блока 4 коммутаций и ввода начальных условий п элементов И, -п элементов ИЛИ. 1 з.п. ф-лы, 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (5D 4 G Ob F 1/02.% р,, ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ НОМИТЕТ СССР

r1O ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4092620/24-24 (22) 11.05,8b (46) 30.12.87. Бил. М 48 (72) А.B.Òêà÷åíêo и В,В.Дудкин (53) 681.325(088.8) (56) Авторское свидетельство СССР

11 - 1091146, кл. G 06 F 1/02, 1983.

Авторское свидетельство СССР

У 6629?b, кл. G 06 F 1/02, 1979. (54) ГЕНЕРАТОР ВОЗВРАТНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ п-ГО ПОРЯДКА (57) Изобретение относится к вычислительной технике и предназначено

„.Я0„„1363170 А1 для генерирования последовательностей весов возвратных последовательностей различного порядка. Цель изобретения.расширение функциональных возможностей за счет генерации весов различных возвратных последовательностей.

Генератор содержит и резисторов 1, блок 2 синхронизации, сумматор 3, блок 4 коммутаций и ввода начальных условий, п элементов И, п элементов

ИЛИ. Поставленная цель достигается за счет введения блока 4 коммутаций и ввода начальных условий п элементов И, и элементов ИЛИ. 1 з.ц. ф -лы, 2 ил.

1 13631

Изобретение относится к вычислительной технике и может быть использовано для моделирования рядов различных возвратных последовательностей.

Выражение (1) позволяет моделировать унарную систему счисления и огромный класс возвратных последовательностей.

0 при п О;

S ((пn)),1 при Оп,1; (1)

1 А-А

S (n-(-j ) при пр, > А-Ь

При В=О, Аса, y =1 выражение (! задает классическую двоичную систему счисления.

Цель изобретения — расширение функциональных возможностей за счет способности генерировать последовательности весов различных возвратных последовательностей, Сущность изобретения состоит в реализации выражения (1) .

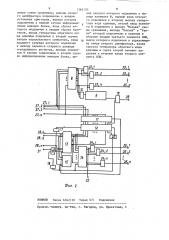

На фиг. 1 изображен генератор возвратных последовательностей и-го порядка; на фиг. 2 — блок коммутаций и ввода начальных условий.

Генератор содержит и разрядных регистров 1.1; 1,2...1.п (где n=1 — ). блок 2 синхронизации, сумматор 3, блокз0

4 коммутаций и ввода начальных ус ловий, и элементов И 5.1, 5.,?...5.п, и элементов ИЛИ 6.1,6.2...6.п информационные выходы 7.1, 7.2...7.п.

Блок 4 коммутаций и ввода начальныхЗ5 условий содержит первый дешифратор 8, генератор 9 кода единицы, первый элемент ИЛИ 10, и-разрядный регистр 11, схему 12 сравнения, параллельный сумматор 13, второй дешифратор 14, гене- 40 ратор 15 обратного кода единицы, второй. элемент ИЛИ 16, два элемента !7 и 18 задержки, элемент И 19, третий элемент 20, вход 21 управления, вход

22 сброса, группу из п sJIeMeHT0B I! 45

23 ° 1...23.n, n триггеров 24.1...24.п, первую группу и выходов 25.1...25.п, вторую группу и выходов 26.1...26.п первую группу и входов 27.1...27.п вторую группу и входов 28.1...28.п, 50 выход 29.

Блок 4 коммутаций и ввода начальных условий служит для ввода начальных условий в i первых регистров, а также подключения к сумматору выходов соответствующих регистров 1-n., в зависимости от принятых для данного случая А, В, 70 2

Для того, чтобы рассмотреть работу генератора возвратных последовательностей и-го порядка, проанализируем сначала работу блока коммутаций и ввода начальных условий, Блок коммутаций и ввода начальных условий работает следующим образом.

На входные шины 27.1, 27.2...27.п поступает значение (+В) в двоичной классической системе счисления, записывается в регистр 11 и поступает на входы дешифратора 8. В зависимости от значения (+В) на выходе дешифратора 8 с номером (+В) появляется логическая "1", которая через элемент

ИЛИ 10 включает генератор,9 и открывает соответствующий элемен!г И .23,1, 23.2...23.п. Генератор 9 выдает последовательным кодом единицу, которая через элемент И поступает на соответствующую выходную шину 25.1, 25.2...25.п. Тем временем на входные шины 28.1, 28.2...28.п поступает значение (? +А) в двоичной классической системе счисления и записывается в триггеры параллельного сумматора 13.

По сигналу на управляющей шине 21 значение (? +А) выдается из сумматора 13 на входы схемы 12 сравнения и дешифратора 14. По сигналу с выхода элемента 17 задержки происходит сравнение значений (2 +А) и (+В) в схеме 12 сравнения, выдается сигнал (2 +А) > (+В) или(2 +А) < (+В) . Если (2 +А) (+В), то сигнал через элемент

ИЛИ 10 поступает на вход управления дешифратора 14, на выходе дешиф ратора с номером (2 +А) появляется сигнал "1", который запоминается соответствующим триггером 24.i и подключает выходную шину 26.i, Этим же сигналом запускается генератор 15 который выдает параллельным кодом на входы сумматора 13 обратный код единицы. По этому же сигналу, задержанному в элементе 18 задержки, происходит выдача результата на вход схемы 12 сравнения, которая по сигналу с выхода элемента 17 задержки производит сравнение значений (2 +А-1) и (+В). Если (? +А-1)В (!+В), то процесс, только что описанный, повторяется до тех пор, пока (2/+А-i} не станет меньше +В. В этом случае сигнал 1 поступает на вход элемента

I I 1Ь

И 19. Если генератор 9 уже выдал код

1, то с выхода элемента И 19 по шине

29 включается блок 2 синхронизации генератора.

Формула изобретения

1. Генератор возвратных последовательностей п-го порядка, содержащий п регистров, блок синхронизации, сумматор, причем первый выход блока cmr- хронизации подключен к управляющим 50 входам всех регистров, второй выход блока синхронизации подключен к управляющему входу сумматора, выход первого регистра подключен к первому информационному выходу генератора, 55 о т,л и ч а ю шийся тем, что, с целью расширения функциональных возможностей за счет генерации последовательности весов различных возврат3 13631

Генератор 15 формирует обратный код единицы разрядностью, равной разрядности параллельн< сумматора 13.

Таким образом, блок 4 коммутаций

5 и ввода начальных условий вводит в первые (II +В) регистров значение единицы и подключает выходы регистров

l.i с номерами i6 (+В; 2)+A) к входу сумматора 3 генератора возвратных последовательностей и-го порядка.

При необходимости смоделировать другую возвратную последовательность подается сигнал на шину 22 сброса, затем вводятся новые значения (+В) и (2 +А).

ПосЛе того, как введены начальные условия и сформированы подключения соответствующих регистров l.i с номером i б j(+B; 2 +А к входам суммато20 ра 3 подается сигнал управления на вход блока 2 синхронизации, который формирует синхросигнал на регистры

l.i и сумматор 3. В регистрах осуществляется перезапись информации из младших в старшие, а в регистр

1.1 записывается число, явившееся результатом суммирования содержимого регистров l.i с номерами И(+В; 2 +

+А) . Далее блок синхронизации вновь выдает синхросигнал на регистры, чуть позже — на сумматор, происходит аналогичный процесс перезаписи чисел в следующие регистры l,i и суммирования. Информация снимается с информационного выхода 7 (+В).

Очевидно, что, изменяя значения А, В, в выражении (1), можно синтезировать любую возвратную последовательность, которая используется в качестве базовой функции системы

40 счисления с естественной избыточно- стью.

4 ных последовательностей, в него введены и элементов ИЛИ, элементов И, блок коммутаций и ввода начальных условий, причем выходы i-х (i=1,...,n) регистров подключены к первым входам соответствующих i-x элементов И, вторые входы которых подключены к соответствующим выходам первой группы из п выходов блока коммутаций и ввода начальных условий, каждый -й выход второй информационной группы выходов которого подключен к (п-i+1)-му входу всех элементов ИЛИ с первого по i-й группы элементов ИЛИ, выход сумматора подключен к (и+1)-му входу первого элемента ИЛИ группы, выходы

i-х регистров подключены к (и-i+1)-му входу (i+1)-ro элемента ИЛИ группы, выходы i-x элементов И подключены к соответствующим входам сумматора, вход запуска блока синхронизации подключен к выходу запуска блока коммутаций и ввода начальных условий, выходы регистров с второго по и-й подключены к соответствующим выходам с второго по п-й генератора.

2. Генератор по п. 1, о т л ич а ю шийся тем, что блок коммутаций и ввода начальных условий содержит два дешифратора, параллельный сумматор, генератор кода единицы, генератор обратного кода единицы, два элемента задержки, три элемента

ИЛИ, схему сравнения, и-разрядный регистр, элемент И, группу из и элементов И, и триггеров, причем вход п-разрядного регистра и вход первого дешифратора подключен к первой группе информационных входов блока, выходы пешифратора подключены к первым входам элементов И группы, к и входам первого элемента ИЛИ, выход которого подключен к входу пуска генератора кода единицы, первый выход которого подключен к вторым входам элементов

И группы, вторая группа информационных входов блока подключена к первой группе информационных входов параллельного сумматора, выход которого подключен к группе информационных входов второго дешифратора и первой группе входов схемы сравнения, вторая группа входов которой подключена к выходу и-разрядного регистра, вход управления блока подключен к первому входу второго элемента ИЛИ, выход которого подключен к входу управления параллельного сумматора и через первый элемент задержки к входу управ13631

27. Л г7ъ 3

ПвП

Фиг. 2

BHHH1IH Заказ 6362/39 Тираж 671 Подписное

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4 ления схемы сравнения, выходы второго дешифратоора подключены к входам установки триггеров, выходы которых подключены к первой группе информаци5 онных выходов блока, вход сброса которого подключен к входам сброса триггеров, выход генератора обратного .ко1ца единицы подключен к второй группе входов параллельного сумматора, вход младшего разряда которого подключен к выходу переноса старшего разряда и-разрядного регистра, выходы элементов И группы подключены к второй группе информационных выходов блока, вы70

6 ход запуска которого подключен к выходу элемента И, первый вход которого подключен к второму выходу генератора кода единицы, второй вход элемента И подключен к выходу "Меньше" схемы сравнения, выходы "Больше" и "Равно" которой подключены к первому и второму входам третьего элемента ИЛИ, выход которого подключен к управляюшему входу второго дешифратора, входу запуска генератора обратного кода единицы и через второй элемент задержки к второму входу второго элемента HJIH.