Устройство для сравнения чисел в пределах поля допуска

Иллюстрации

Показать всеРеферат

Изобретение относится.к автоматике и вычислительной технике и может быть использовано при реализации технических средств цифровых вычислительных машин. Цель изобретения - повышение быстродействия устройства . Устройство для сравнения чисел содержит регистр 1 числа, сумматор 2, счетчик 3, элементы И 7, 8, 9, выходы которых являются выходами устройства, регистр 14 поля допуска , счетчик 15 поля допуска, триггеры 16, 17, элементы И 18, 19, ИЛИ 20, 21, элемент НЕ 22, элемент задержки 23. В устройстве поле Д допуск а представляется в виде последовательности импульсов, и разность fcpas- ниваемых чисел А и В сравнивается с этой последовательностью импульсов. Если разность А-В сравниваемых чисел соответствует полю Д допуска, то на выходе устройства появляется сигнал Равно (А В). Если разность (А-В) Д, то появляется сигнал - ше (), если (А-В), то-на выходе устройства появляется сигнал Меньше (). 1 ил. i (Л :о 35 : ЭР

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (51) 4 G 06 F 7 02

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

14

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ "Мио:;;,, r ль л-в д в (21) 3986718/24-24 (22) 04. 12. 85 (46) 30. 12. 87. Бюл. 11- 48 (71) Институт технической кибернетики АН БССР (72) А.Я.Кулешов и,В.П.Лутович (53) 681 325,5(088.8) (56) Авторское свидетельство СССР

У 809168, кл. G 06 F 7/04, 1979.

Авторское свидетельство СССР

У 1008730, кл. С 06 F 7/02, 1981. (54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ЧИСЕЛ

В ПРЕДЕЛАХ ПОЛЯ ДОПУСКА (57) Изобретение относится,к автоматике и вычислительной технике и может быть использовано при реализации технических средств цифровых вычислительных машин. Цель изобретения — повышение быстродействия устройства. Устройство для сравнения чисел содержит регистр I числа, сумматор 2, счетчик 3, элементы И 7, 8, 9, выходы которых являются выхода" ми устройства, регистр 14 поля допуска, счетчик 15 поля допуска, триггеры 16, 17, элементы И 18, 19, ИЛИ

20, 21, элемент HE 22, элемент задержки 23. В устройстве поле Д допуска представляется в виде последовательности импульсов, и разность срав" ниваемых чисел А и В сравнивается с этой последовательностью импульсов.

Если разность А-В сравниваемых чисел соответствует полю Д допуска, то на выходе устройства появляется сигнал

"Равно" (A = В) ° Если разность (A-В) > Д, то появляется сигнал Больme" (А В), если (А-В) (Д, то. на выходе устройства появляется сигнал

"Меньше" (А В) . 1 ил.

136318) Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств цифровых вычис5 лительных машин.

Цель изобретения — повышение быстродействия устройства °

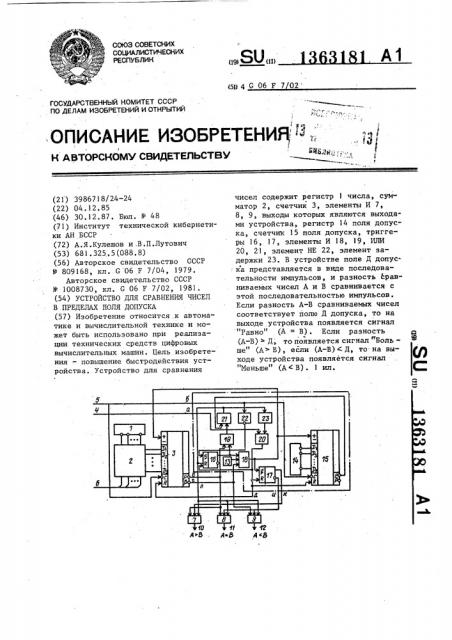

На чертеже представлена блок-схема усТройства, 10

Устройство для сравнения чисел содержит регистр 1 числа, сумматор

2, счетчик 3, вход 4 начальной установки устройства, вход 5 запуска устройства, входы 6 числа, элементы 1."

И 7-9, выходы 10-12 устройства, генератор 13 импульсов, регистр 14 поля допуска, счетчик 15 поля допуска, триггеры 16 и !7, элементы И 18, 19, ИЛИ 20, 21, элемент НЕ 22, и элемент 2р

23 задержки.

Устройство работает следующим образом.

Перед началом работы устройства оператор заносит, например, при по- 25 мощи тумблерного набора в регистр 1 первое сравниваемое число В, которое принимается за максимальное значение, а в регистр 14 поля допуска — код D поля допуска сравниваемых чисел А и 30

В (цепи установки первого сравниваемого числа В в регистр 1 устройства и кода D поля допуска сравниваемых .чисел А и В в регистр 14 поля допуска на чертеже не показаны).

Затем на вход 4 устройства подается сигнал начальной установки устройства ° Сигнал начальной установки устройства поступает на вход первого элемента ИЛИ 20, с выхода которого 40 он поступает на нулевые установочные входы счетчика 15 поля допуска, первого 16 и второго 17 триггеров, устанавливая их в нулевые состояния и далее на нулевой установочный вход счетчика 3, устанавливая его в нулевое состояние.

При поступлении второго сравниваемого числа А на входы 6 в сумматоре

2 происходит вычитание (А-В), поскольку в сумматор 2 с регистра 1 поступает обратный код первого сравниваемого числа В. Затем с учетом времени операции вычитания (А-В) в сумматоре 2 на вход 5 запуска устройства поступает сигнал "Пуск". Сигнал

"Пуск" низкого уровня поступает на вход предварительной записи счетчика 3, осуществляя запись результата вычитания (А-В) в счетчик 3. Сигнал

"Пуск" с входа 5 устройства поступает также и на вход предварительной записи счетчика )5 поля допуска, осуществляя запись обратного значения кода D поля допуска сравниваемых чисел. Проинвертированный элементом

НЕ 22 сигнал "Пуск" поступает на единичный установочный вход первого триггера 16, устанавливая его в единичное состояние. Сигнал высокого уровня с прямого выхода первого триггера 16 поступает на первые входы первого и второго элементов И 18, 19. Если второе сравниваемое число

A больше первого сравниваемого числа

В, то знаковый разряд сумматора 2 будет установлен в единичное состояние, следовательно, с прямого выхода старшего разряда счетчика 3 (выход переноса) на второй вход второго элемента И 19. Сигнал высокого уровня с выхода элемента И 19 поступает через второй элемент ИЛИ 21, элемент

23 задержки, необходимый для задержания сигнала на время фиксации результата сравнения, и первый элемент

ИЛИ 20 на нулевые установочные входы счетчика )5 поля допуска, первого 16 и второго 17 триггеров, с инверсного выхода старшего разряда счетчика

3 (выход заема) — на третий вход первого элемента И 18, препятствуя прохождению счетных импульсов, поступающих на его второй вход с генератора 13 счетных импульсов.

С прямого выхода старшего разряда счетчика 3 сигнал высокого уровня поступает также на первые входы элементов И 7, 8. Поскольку второй триггер 17 находится в нулевом состоянии, на второй вход элемента И 7 поступает сигнал высокого уровня.

На вторых входах элементов И 8, 9 присутствует сигнал низкого уровня, поступающий с прямого выхода второго триггера 17.

Сигнал высокого уровня с выхода второго элемента ИЛИ 21 поступает на третьи входы элементов И 7-9. На выходе 10 элемента И 7 появится сигнал высокого уровня, разрешая индикацию результата сравнения "Больше" (А В).

На других выходах 11 и 12 элеглентов

И 8, 9 будут сигналы низкого уровня, поскольку на их вторых входах присутствует сигнал низкого уровня. Затем сигнал высокого уровня,.задержанный

3 13631 элементом 23 задержки, поступает на второй вход первого элемента ИЛИ 20.

Сигнал высокого уровня с выхода первого элемента ИЛИ 20 производит усВ тановку в нулевое состояние счетчика

15 поля допуска, первого 16 и второго 17 триггеров и счетчика 3, подготовив устройство к сравнению следующего числа А с В. 10

Если число А равно В с учетом поля допуска или без него, то знаковый разряд сумматора 2 будет находиться в нулевом состоянии. В этом случае сигнал низкого уровня поступает на 16 второй вход элемента И 19, препятствуя прохождению сигнала высокого уровня, поступающего с прямого выхода первого триггера 16 на выход элемента И 19.

С инверсного выхода старшего разряда счетчика 3 поступает сигнал высокого уровня на третий вход первого элемента И 18, разрешая прохождение счетных импульсов, поступающих на 25

его второй вход с генератора 23 счетных импульсов. С выхода первого элемента И 18 счетные импульсы поступают на счетный вход счетчика 15 поля допуска, в котором записан обратный 3р код D поля допуска сравниваемых чисел А и В, на единичный установочный вход второго триггера 17, устанавливая его в единичное состояние, и на счетный вход счетчика 3.

Счетные импульсы будут поступать на счетный вход счетчика 3 до тех

1 бор, пока старший разряд счетчика 3 не установится в единичное состояние или пройдет заданное число импульсов, 40 раное полю D допуска сравниваемых чисел А и В плюс единица (0+1).

Если в процессе поступления счетных импульсов на счетный вход счетчика 3 его старший разряд установится 4> в единичное состояние, то сигнал высокого уровня с прямого выхода старшего разряда счетчика 3 поступает на второй вход элемента И 19, на первом входе которого присутствует сигнал 50 высокого уровня.

Сигнал высокого уровня с прямого выхода старшего разряда счетчика 3 поступает на первые входы элементов

И 7, 8. На второй вход элемента И 8 поступает сигнал высокого уровня, поскольку второй триггер 17 установлен в единичное состояние. Сигнал высокого уровня с выхода второго элемента И 19 через элемент ИЛИ 21 поступает на второй нулевой установочный вход первого триггера 16, устанавливая его в нулевое состояние.

Сигнал низкого уровня с прямого выхода первого триггера поступает на первый вход элемента И 18, запрещая прохождение счетных импульсов с генератора 23 счетных импульсов. Сигнал высокого уровня с выхода второго элемента ИЛИ 21 поступает на третьи входы элементов И 7-9. На выходе ll элемента И 8 появится сигнал высокого уровня, разрешающий индикацию результата сравнения "Равно" (А = В). На других выходах 10, 12 элементов И 7, 9 будут сигналы низкого уровня, поскольку на втором входе элемента И 7 и на первом входе элемента И 9 присутствуют сигналы низкого уровня.

Сигнал высокого уровня с выхода второго элемента ИЛИ 21 через элемент

24 задержки поступает на .второй вход первого элемента ИЛИ 20, с выхода которого сигнал высокого уровня поступает на нулевые установочные входы счетчика 15 поля допуска, первого 16 и второго 17 триггеров, устанавливая их в нулевые состояния и на нулевой установочный вход счетчика 3, устанавливая его в нулевое состояние. Таким образом устройство подготовлено для сравнения следующего числа A с В.

Если в процесс поступления счетных импульсов на счетный вход счетчика 3 его старший разряд не установится в единичное состояние, то сигнал высокого уровня поступает с инверсного выхода старшего разряда счетчика 3 на третий вход первого элемента

И 18, разрешая прохождение счетных импульсов с генератора 13 счетных импульсов на счетный вход счетчика

15 поля допуска. При этом второй триггер 17 находится в единичном состоянии. Сигнал высокого уровня с инверского выхода старшего разряда счетчика 3 поступает на первый вход элемента И 9. На второй вход элемента И 9 поступает сигнал высокого уровня с прямого выхода второго триггера 17. Поскольку в счетчике 15 поля допуска записан обратный код D поля допуска, то поступление (D+1)го импульса вызывает переполнение счетчика 15 поля допуска. Сигнал высокого уровня с выхода переполнения счетчика 15 поля допуска поступает

63181

5 13 на в:мрой вход элемента ИЛИ 21. С выхода элемента ИЛИ 21 сигнал высокого уровня поступает на нулевой установочный вход первого триггера, устанавливая его в нулевое состояние.

Сигнал низкого уровня с прямого выхода первого триггера 16 поступает на первый вход элемента И 18, запрещая прохождение счетных импульсов с генератора 23. Сигнал высокого уровня с выхода второго элемента ИЛИ 21 поступает на третьи входы элементов И 7-9.

На выходе 12 элемента И 9 появится сигнал высокого уровня, разрешающий индикацию результата сравнения "Меньше" (А < Б) . На других выходах 10 и

ll элементов И 7, 8 будут сигналы низкого уровня, поскольку на первых входах элементов И 7, 8 присутствуют сигналы низкого уровня. Сигнал высокого уровня с выхода элемента ИЛИ 21 через элемент 23 задержки поступает на второй вход первого элемента ИЛИ

20 и далее — на нулевые установочные входы счетчика 15 поля допуска, первого 16.и второго 17 триггеров, устанавливая их в нулевые состояния, и на нулевой установочный вход счетчика 3, устанавливая его в нулевое состояние. Таким образом устройство подготовлено для сравнения следующего числа А с В. формула изобретения

Устройство,для сравнения чисел в пределах поля допуска, содержащее регистр числа, сумматор, счетчик, два триггера, два элемента И, первый элемент ИЛИ, элемент задержки, регистр поля допуска, счетчик поля допуска, три выходных элемента И, причем инверсные выходы регистра числа, входы которого являются входами первого сравниваемого числа устройства; соединены с соответствующими входами сумматора первой группы, вход начальной установки устройства подключен к первому входу элемента ИЛИ, выход которого подключен к входам установок в нулевое состояние счетчика и счетчика поля допуска, счетный вход которого соединен с выходом первого элемента. И, первый вход которого подключен к прямому выходу первого триггера, первые входы выходных элементов

И объединены, прямой выход второго триггера подключен к второму входу первого выходного элемента И, выход которого является выходом А ) Б устройства, инверсный выход второго триггера соединен с вторым входом второго выходного элемента И, выход которого является выходом А В устройства, выход третьего выходного

)p элемента И является выходом А = В устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены второй элемент ИЛИ, генератор импульсов и эле15 мент НЕ, причем вход запуска устройства соединен с входами разрешения записи счетчика и счетчика поля допуска и через элемент НŠ— с входом установки в единичное состояние пер2р вого триггера, прямой выход которого дополнительно подключен к первому входу второго элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого под25 ключен к первым входам выходных элементов И и первому входу установки в 0 первого триггера и через элемент задержки соединен с вторым входом первого элемента ИЛИ, выход кото30 рого дополнительно подключен к второму входу установки в "0" первого триггера и входу установки в "0" второго триггера, вход установки в

"1" которого соединен с выходом первого элемента И и счетным входом

35 счетчика, а инверсный выход соединен дополнительно с вторым входом третьего выходного элемента И, третий выход которого соединен с третьим вхо п дом первого выходного элемента И, вторым входом второго элемента И и прямым выходом старшего .разряда счетчика, инверсный выход старшего разряда которого соединен с третьим вхо45 дом второго выходного элемента И и вторым входом первого элемента И, третий вход которого подключен к выходу генератора импульсов, инверсные выходы регистра поля допуска соединены с соответствующими информационными входами счетчика поля допуска, выход переполнения которого подключен к второму входу второго элемента

ИЛИ, информационные входы счетчика соединены с соответствующими выхода55 ми сумматора, входы второй группы которого являются входами второго сравниваемого числа устройства.