Сигнатурный анализатор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к устройствам контроля и диагностики. Целью изобретения является расширение функциональных воз12 Синх.. можностей за счет программного задания интервалов контроля при выполнении циклических программ. Анализатор содержит генератор 1 импульсов, D-триггер 2, формирователь 3 сигнатур, формирователь строба 4, два блока ассоциативной памяти 5, 6, счетчик 7, мультиплексор 8, три элемента И 9, 10, И. Анализатор позволяет отслеживать конкретные циклы при выполнении вложенных подпрограмм наряду с программным заданием интервалов контроля в микропроцессорных системах и отслеживать программные интервалы в системах и ЭВМ с совмещенной магистралью адрес-данные. 1 ил. ел со О5 оо ьо

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (59 4 G 06 F 11 00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ 1 3

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

12 Сикх.

15 (21) 3994251/24-24 (22) 23.12.85 (46) 30.12.87. Бюл. ¹ 48 (72) А. Н. Бучнев и Е. И. Карпунин (53) 681.3(088.8) (56) Кирьянов К. Г. К теории сигнатурного анализа. — Техника средств связи.

Серия РИТ, 1980, № 2, с. 9 — 11.

Авторское свидетельство СССР № 1140123, кл. G 06 F ll/!6, 1983. (54) СИ ГНАТУР НЫЛ АНАЛИЗАТОР (57) Изобретение относится к вычислительной технике, в частности к устройствам контроля и диагностики. Целью изобретения является расширение функциональных воз„„SU„„1363210 А 1 можностей за счет программного задания интервалов контроля при выполнении циклических программ. Анализатор содержит генератор импульсов, D-триггер 2, формирователь 3 сигнатур, формирователь строба 4, два блока ассоциативной памяти 5, 6, счетчик 7, мультиплексор 8, три элемента

И 9, 10, 11. Анализатор позволяет отслеживать конкретные циклы при выполнении вложенных подпрограмм наряду с программным заданием интервалов контроля в микропроцессорных системах и отслеживать программные интервалы в системах и ЭВМ с совмещенной магистралью адрес — данные.

1 ил.

1363210

Изобретение относится к вычислительной технике, в частности к устройствам контроля и диагностики, и может быть использовано для поиска неисправностей в цифровых устройствах различной степени сложности и назначения.

Целью изобретения является расширение функциональных возможностей за счет возможности программного задания интервалов контроля при выполнении циклических программ.

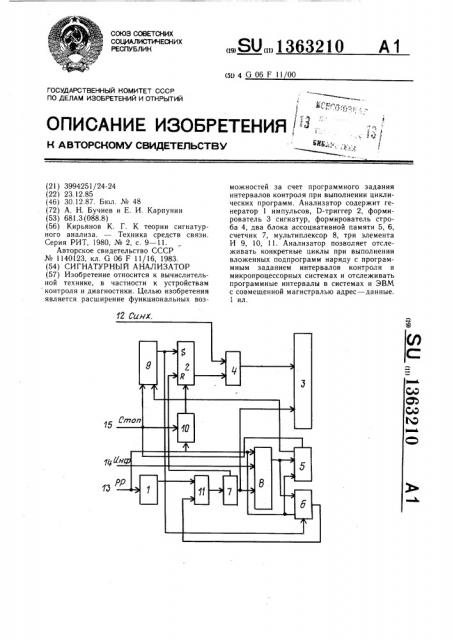

На чертеже представлена функциональная схема сигнатурного анализатора.

Анализатор содержит генератор 1 импульсов, D-триггер 2, формирователь 3 сигнатур, формирователь 4 строба, два блока 5 и 6 ассоциативной памяти, счетчик 7, мультиплексор 8, три элемента И 9, 10 и 11, вход 12 синхронизации, вход 13 выбора режима анализатора, информационный вход 14, выход 15 «Стоп» анализатора.

Сигнатурный анализатор может работать в двух режимах: начальной установки и запуска и сбора сигнатуры.

Начальная установка. В исходном состбянии на входе 13 логического анализатора поддерживается состояние лог. «О».

Генератор 1 импульсов, получив сигнал разрешения» выдает синхросигналы через элемент И 11 на вход счетчика 7. Адресный код с выхода счетчика 7 поступает через мультиплексор 8 на блоки 5 и 6 ассоциативной памяти для занесения в соответствующие ячейки логических значений нуля или единицы. Блоки 5 и 6 ассоциативной памяти находятся в режиме записи, так как на входе 13 поддерживается состояние лог. «О». Установка информации производится в блоках 5 и 6 ассоциативной памяти, которые находятся в режиме записи, так как на входе 13 поддерживается состояние лог. «О». Установка информации производится в блоках 5 и 6 ассоциативной памяти переключением соответствующих тумблеров. После заполнения блоков 5, 6 памяти в счетчик 7 заносится информация, значение которой соответствует числу повторений квалификаторного слова, которое должно встретиться после слова запуска заданное число раз, чтобы сигнатурный анализатор начал сбор сигнатуры.

Режим запуска и сбора сигнатуры определяется установкой на управляющем входе 13 лог. «1». Мультиплексор 8 переключает направление передачи информации. Сигнал с информационной группы входов 14 поступают на адресные входы блоков 5 и 6 ассоциативной памяти через мультиплексор 8.

Генератор 1 импульсов блокируется. Блок 5 ассоциативной памяти работает в режиме чтения, управляющий вход 13 находится в состоянии лог. «1». При появлении на первом выходе первого блока 5 ассоциативФормула изобретения

50. циклических программ, анализатор содержит

5

40 !

45 ной памяти сигнала лог. «1», выход формирователя 4 строба установится в состояние лог. «1», разрешая работу в режиме чтения второму блоку 6 ассоциативной памяти, сняв блокировку. Появление на выходе второго блока 6 ассоциативной памяти сигнала лог. «О» вызывает увеличение значения счетчика 7 на единицу. Этот процесс повторяется до тех пор, пока счетчик 7 не переполнится; устанавливая D-триггер 2 в единицу. С этого момента разрешается прохождение синхросигнала со входа

12 устройства на тактирующий вход формирователя сигнатур через элемент И 9.

Формирователь сигнатур будет сворачивать информацию, поступающую с объекта контроля, пока с выхода первого блока 5 ассоциативной памяти не появится сигнал останова — лог. «1». Он установит в нуль D-триггер 2 и формирователь 4 строба, блокируя поступление тактирующего сигнала на формирователь 3 сигнатур.

Сигнатурный анализатор, содержащий генератор импульсов, формирователь строба, три элемента И, мультиплексор, первый блок ассоциативной памяти и формирователь сигнатур, причем синхровход анализатора подключен к первому входу первого элемента И, выход которого подключен к синхровходу формирователя сигнатур, входы установки и сброса формирователя строба соединены соответственно с первым и вторым выходами первого блока ассоциативной памяти, группа адресных входов которого соединена с группой выходов мультиплексора, управляющий вход которого соединен с входом управления чтением/записью первого блока ассоциативной памяти, первым входом второго элемента И и является входом выбора режима анализатора, первая группа информационных входов мультиплексора является группой информационных входов анализатора, вторая группа информационных входов мультиплексора объединена с группой информационных входов формирователя сигнатур, выход генератора импульсов соединен с первым входом третьего элемента И, отличающийся тем, что, с целью расширения функциональных возможностей за счет обеспечения возможности программного задания интервалов контроля при выполнении счетчик, триггер и второй блок ассоциативной памяти, группа адресных входов которого соединена с группой выходов мультиплексора, вход чтения второго блока ассоциативной памяти соединен с выходом формирователя строба и информационным входом триггера, вход записи и выход второго блока ассоциативной памяти подключены соответственно к управляющему

13632I0

Составитель С. Старчикин

Редактор А. Доли нич Техред И. Верес Корректор М. Максимишинец

3а каз 5966/41 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

11303ф, Москва, 7K — 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 входу мультиплексора и второму входу третьего элемента И, выход которого соединен со счетным входом счетчика, группа разрядНых выходов которого соединена с второй группой информационных входов мультиплексора, выход переполнения счетчика соединен с синхровходом триггера, нулевой вход и выход которого соединены соответственно с выходом второго элемента И и вторым входом первого элемента И, второй вход второго элемента И соединен с входом сброса формирователя строба и является выходом «Стоп» анализатора, вход блокировки генератора импульсов подключен к входу выбора режима анализатора.