Устройство для защиты информации в блоках памяти при отключении питания

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к устройствам для защиты информации в блоках памяти при отключении питания. Цель изобретения - повышение надежности хранения записанной в блоках памяти информации . Устройство содержит резервный источник 1 питания, переключатель 2, формирователь 3 сигналов блокировки, управляющий вход 4, вход 5 внешнего источника питания, формирователь 6 сигналов разблокировки , триггеры 7, 8, элементы ИЛИ - НЕ 9, 10, формирователи 11, 12 выходных сигналов, нелинейный элемент 13, интегрирующий элемент 14, формирователь 15 напряжения питания, формирователь 16 управляющих сигналов, стабилизатор 17. выход 18. 1 ил. сл со о: оо to го N5 ГО

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1363222 A 2 (S0 4 G 06 F 12 16 G 11 С 29 00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ (!3 "

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ (61) 999115 (21) 4074271/24-24 (22) 25.04.86 (46) 30.12.87. Бюл. № 48 (72) С. С. Степанов, Э. П. Твеленев, М. И. Фомин и В. И. Чуканов (53) 681.327 (088.8) (56) Авторское свидетельство СССР № 999115,.кл. G 11 С 29/00, 1981. (54) УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ИНФОРМАЦИИ В БЛОКАХ ПАМЯТИ ПРИ

ОТКЛЮЧЕНИИ ПИТАНИЯ (57) Изобретение относится к вычислительной технике, в частности к устройствам для защиты информации в блоках памяти при отключении питания. Цель изобретения — повышение надежности хранения записанной в блоках памяти информации. Устройство содержит резервный источник 1 питания, переключатель 2, формирователь 3 сигналов блокировки, управляющий вход 4, вход 5 внешнего источника питания, формирователь 6 сигналов разблокировки, триггеры 7, 8, элементы ИЛИ—

НЕ 9, 10, формирователи 11, 12 выходных сигналов, нелинейный элемент 13, интегрирующий элемент 14, формирователь

15 напряжения питания, формирователь 16 управляющих сигналов, стабилизатор 17. выход 18. 1 ил.

1363222

Изобретение относится к вычислительной технике, в частности к устройствам для защиты информации в блоках памяти при отключении питания.

Цель изобретения — повышение надежности хранения записанной в блоках памяти информации.

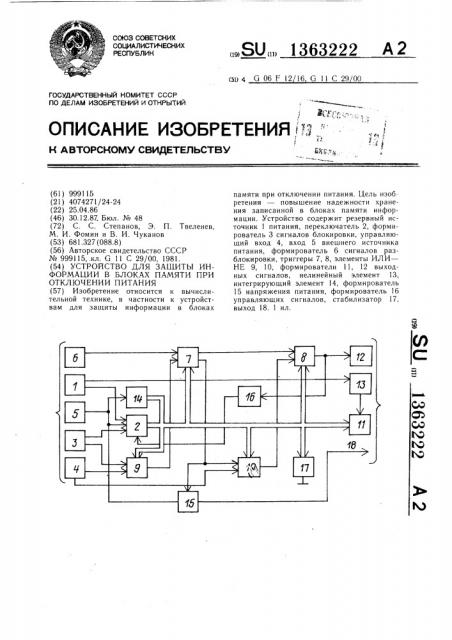

На чертеже изображена структурная схема устройства для защиты информации в блоках памяти.

Составитель В. Рудаков

Редактор Л. Пчолинская Техред И. Верес Корректор И.Муска

Заказ 5966 41 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 разитный тиристор до такой величины, что прямой ток прекращается после окончания помехи. В момент подачи напряжения от внешнего источника питания (не показан) с положительным выбросом напряжения и с большой скоростью изменения внешнего питающего напряжения ограничение напряжения питания с помощью стабилизатора 17 и одновременное интегрирование фронта напряжения питания интегрирующим элементом 14 возможно только

УстРойство содержит Резервный источник при наличии формирователя 15 устраняю1 питания, переключатель 2, формирова- щего прохождение положительного выброса тель 3 сигналов блокиРовки, УпРавлЯюшии питаюшего напряжения через выход 18 и вход 4, вход 5 внешнего источника пита- зашитные диодные структуры входов комниЯ, фоРмиРователь 6 сигналов Разблоки 15 плиментарных микросхем памяти (не показаРовки, пеРвый 7 и втоРой 8 тРиггеРы, ны). Включение формирователя 15 начинаетпервый 9 и второй 10 элементы ИЛИ вЂ” НЕ ся после временной выдержки, определяемой пеРвый фоРмиРователь 11 выходных сигна- формирователем 6 сигнала разблокировки, и лов, УпРавлЯющий входом питаниЯ блока снятия сигнала блокировки с триггера 7. памЯти, втоРой фоРмиРователь 12 выходных формирователь 16 формирует плавный фронт сигналов, нелинейный элемент 13, выпол- 20 напряжения внешнего источника питания. ненный, например, в виде последовательно При наличии сигнала «Выбор схемы» соединенных диода и РезистоРа (не пока- на управляющем входе 4 и при снятом заны), интегРиРУюший элемент 14, включаю сигнале «Блокировка» триггера 7 происхоший в себЯ последовательно соединенные дит разблокировка триггера 8, который раздиоды, времЯзадаюший РезистоР и фильт- 5 решает работу формирователю 12 и через

РУющие конденсаторы питаниЯ (не показа- формирователь 16 включает силовой транны), фоРмиРователь 15 напРЯжениЯ пита- зистор переключателя 2 с помощью которого ния, фоРмиРователь 16 упРавляющих сигна- происходит коммутация входа 5 внешнего лов, стабилизатор 17, выполненный напри- источника питания. мер, на стабилитроне КС 167А, и выход 18 питания устройства.

30 Формула изобретения

Устройство работает следующим образом.

Если уровень напряжения питания, посту- Устройство для защиты информации в пающего от внешнего источника питания на блоках памяти при отключении питания вход 5, становится ниже определенного уров- по авт. св. № 999115, отличающееся ня, формирователь 3 вырабатывает сигнал, тем, что, с целью повышения надежности который поступает на вход элемента хранения записанной в блоках памяти йнИЛИ вЂ” HE 9. Если в это время на вхо- формации,, в него введены интегрирующий де 4 устройства присутствует сигнал элемент, формирователь напряжения пита«Выбор схемы», то блокировка первого триг- ния, стабилизатор и формирователь управгера 7 происходит только после заверше- ляюших сигналов, вход которого подключен ния действия данного сигнала. Одновре- к выходу второго триггера, выход формименно через элемент ИЛИ вЂ” НЕ 10 проис- 40 рователя управляющих сигналов соединен с ходит блокировка триггера 8.и запрещает- управляющим входом переключателя, вход ся выработка сигнала «Выбор схемы» фор- интегрируюшего элемента соединен с входом мирователем 12, При блокировке триггера 8 внешнего источника питания, выход интегричерез формирователь 16 выключается сило- рующего элемента соединен с выходом вой транзистор (не показан) переключате- переключателя, первый вывод стабилизатора ля 2 и блок памяти (не показан) пере- подключен к выходу переключателя, второй ходит на питание от резервного источни- вывод переключателя соединен с шиной нука 1 через формирователь 11, который левого потенциала, управляющий вход форуправляет входом питания блока памяти. мирователя напряжения питания подключен

Для устранения тиристорногб эффекта в к инверсному выходу первого триггера, вход момент отключения внешнего источника пи- 0 питания формирователя напряжения питатания служит нелинейный элемент 13, кото- ния соединен с входом внешнего источрый при возникновении такого эффекта ника питания, выход формирователя напрявследствие большого внутреннего сопротив- жения питания является одним из выхоления ограничивает прямой ток через па- дов питания устройства.