Систолический процессор дискретного преобразования фурье

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в специализированных системах обработки сигналов и изображений высокой производительности. Цель изобретения - расширение функциональных возможностей путем вычисления двумерного дискретного преобразования Фурье. Поставленная цель достигается за счет того, что в состав процессора входят информационные входы 1, 2, регистр 3, первая матрица 4, операционный блок 5, выход 6 первой матрицы , сумматор 7, вторая матрица 8 из операционных блоков 9, второй вход 10 матрицы, блок сдвиговых регистров 11, каналы 12 блока 11, информационные вьпсоды 13 процессора и блок синхронизации . 4 нп. (Л САЭ О СО 00

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

Ч °

ОПИСАНИЕ ИЗОБРЕТЕНИЯ;.3

H А ВТОРСНОМ,Ф СВИДЕТЕЛЬСТВУ

4О

2 (21) 4096707/24-24 (22) 28.07.86 (46) 30.12.87. Бюл. 9 48 (71) Ленинградский институт точной механики и оптики (72) Г.А. Кухарев, А.10. Тропченко и В.С. Скорняков (53) 681.32(088.8) (56) Аллен Дж. Архитектура вычислительных устройств.-ТИИЭР, т. 73, 1985, У 5.

Система параллельной обработки.

Под ред. Д. Ивенсена. М.: Мир, с. 416. (54) СИСТОЛИЧЕСКИЙ ПРОЦЕССОР ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ (57) Изобретение относится к вычислительной технике и может быть испольÄÄSUÄÄ 1363243 А1 (51)4 G 06 F 15/332 зовано в специализированных системах обработки сигналов и изображений высокой производительности. Цель изоб-. ретения — расширение функциональных возможностей путем вычисления двумерного дискретного преобразования

Фурье. Поставленная цель достигается за счет того, что в состав процессора входят информационные входы 1, 2, . регистр 3, первая матрица 4, операционныи блок 5, выход 6 первой матрицы, сумматор 7, вторая матрица 8 из операционных блоков 9, второй вход

10 матрицы, блок сдвиговых регистров

11, каналы 12 блока ll, информационные выходы 13 процессора и блок синхронизации. 4 ил.

3243

1 136

Изобретение относится к вычислительной технике и может быть использовано в специализированных системах обработки сигналов и изображений высокой производительности.

Цель изобретения — расширение функциональных возможностей путем выполнения двумерного дискретного преобразования Фурье.

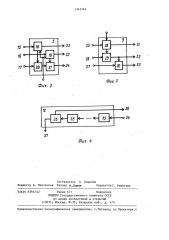

На фиг. 1 представлена функциональная схема систолического процессора дискретного преобразования Фурье (ДПФ); на фиг. 2 — функциональная схема операционного блока первой (систолической) матрицы; на фиг. 3— то же, второй (систолической) матрицы; на фиг. 4 — то же, блока сдвиговых регистров.

Устройство содержит информационные входы 1 и 2, входной регистр 3, первую (систолическую) матрицу 4, операционные блоки 5 первой (систолической)матрицы, выход 6 первой (систолической) матрицы, сумматор 7, вторую (систолическую) матрицу 8, операционные блоки 9 второй (систолической) матрицы, второй вход 10 систолической матрицы, блок 11 сдвиговых регистров, каналы 12, информационные выходы 13 процессора и блок

14 синхронизации.

Операционный блок 5 (фиг. 2) содержит входы 15-17, регистры 18 и 19, умножитель 20, сумматор 21, выходы

22-24.

Операционный блок 9 (фиг. 3) содержит входы 25-27, регистр 28, умножитель 29, сумматор 30, выходы 31-33.

Блок ll сдвиговых регистров (фиг. 4) содержит вход 34, регистр

35, выходы 36 и 37.

Процессор работает следующим образом..

При выполнении двумерного ДПФ

CN Eк(X>E N) Š— матрица действительных эксК поненциальных функций, все матрицы имеют порядок N.

Процессор реализует преобразования (1) по формулам:

К

10 С = ." 1 „, (E X )), WN-exP(-)2тУМ);

В-! и (i г т, (el где Х =(Х1, . Х1,,...,Х1, ); С

15 =(СР,, Се, СВ„),МК, ГЕ М.

В выраженйи (2) преобразование в круглых скобках для каждого k выполняется систолической матрицей 4 лишь один раз с использованием этого результа20 та во всех параллельных ветвях вычисления С . Дополнительные операции (В) в выражении (2), соответствующие вычислению преобразования Фурье по второй координате, выполняются дополнительным сумматором 7, второй систолической матрицей 8 и блоком 11 сдвиговых регистров, осуществляющим накопление текущих результатов двумерного ДПФ. При этом исходные данные

30 Х загружаются по входу 2 систоли(х1 ческого процессора, на вход 1 которого поступают весовые множители

Р 1

W к (p g 1, Н), с выхода 6 первой систолической матрицы 4 считывается результат, соответствующий вычислению одномерного ДПФ, который поступает на первый вход дополнительного сумматора 7 и первый вход второй систолической матрицы 8, на второй

40 вход 10 которой поступают весовые множители W "."(К е 1, М). Результат двумерного ДГФ снимается g общего выхода 13 блока 11 сдвиговых регистров. При этом каждая ячейка блока 5 первой систолической матрицы 4 реализует следующие функции (фиг. 2):

8 õ Вх В iх Вх

Х =

Уи

W (м-» н

Е =

55 1 )Вых Вх

„(К- i) (И- i)

К (4) X 8õ Вх

W исходных данных; результатов; где

"Вих 3= "sx " Вх

Х, Х, ...Х, 1

Х, Х,,...Х, Х Х, ...Х, 2 ,о о о

" К 1 К 1 К °

„ О „1 Ч „1К

К н

Х вЂ” матрица

Ск. — матрица

С, С, ...С, Ск — С С ...Ce„3 1 Nhl ц) Вьп вх 48х + "Вх

Каждая ячейка блока 9 второй систолической матрицы 8 реализует функции (фиг. 3):

1363243

Работой процессора управляет станpàðòHûê блок 14 синхронизации.

Формула изобретения

Систолический процессор дискретного преобразования Фурье, содержащий первую матрицу из (М-1) операци.онных блоков, где М вЂ” размер преобразования, причем первый и второй выходы 1-ro (i=1, N-2) операционного блока. подключены соответственно к первому и второму входам (1+1)-ro операционного блока, первый и второй входы первого операционного блока матрицы являются соответственно первым и вторым входами первой матрицы, первым и вторым выходами которой являются соответственно первый и второй выходы (М-1)-го операционного блока первой матрицы, о т л и ч а ю щ и йс я тем, что, с целью расширения функциональных возможностей путем выполнения двумерного преобразования

Фурье, в него введены вторая матрица из (N-1) операционных блоков, блок сдвиговых регистров, сумматор и регистр, информационный вход которого является информационным входом процессора, причем третьи выходы i-го операционного блока первой матрицы подключены к третьему входу (i+1)-ro операционного блока первой матрицы, третьим входом и третьим выходом-которой являются соответственно третий вход первого и третий выход (М"1)-го операционных блоков первой матрицы, первый и второй входы регистра подключены соответственно к третьему и второму входам первой матрицы, второй выход которой подключен к первбму входу сумматора и первому входу второй матрицы, выход сумматора подклю- . чен к первому информационному входу блока сдвиговых регистров, первый выход которого подключен к второму входу сумматора, третий выход i-ro операционного блока второй матрицы подключен к (i+1)"му информационно45 рационного блока, третьим выходом и тактовым входом которого являются соответственно выход сумматора и тактовый вход регистра. му входу блока сдвиговых регистров, тактовый вход которого соединен с тактовыми входами операционных блоков первой и второй матриц и является тактовым входом процессора, а (i+1)-й выход блока сдвиговых регистрдв подключен к третьим входам 1-х операционных блоков, первой и второй матриц и является (i+1)-м информационным выходом процессора, причем операционный блок первой матрицы содержит два . регистра, умножитель и сумматор, первым входом операционного блока является информационный вход первого ре15 гистра, первый выход которого является первым выходом операционного блока, вторым входом которого является первый вход-умножителя, второй вход ко-- торого подключен к второму выходу первого регистра, выход умножителя подключен к первому входу сумматора, выход которого является вторым выходом операционного блока, третьим входом

25 которого является информационный вход второго регистра, первый выход которого является третьим выходом операционного блока, тактовым входом которого являются соединенные между собой тактовые входы первого и второго регистров, второй выход второго регистра подключен к второму входу сумматора, при этом операционный блок второй матрицы содержит умножитель, сумматор и регистр, информационный вход которого

З5 является вторым входом операционного ! блока, вторым выходом которого явля- ется первый выход регистра, второй выход которого подключен к первому входу умножителя, второй вход которого является первым входом операционного блока, первым выходом которого является выход умножителя, соединенный с первым входом сумматора, второй вход которого является третьим входом опе1363243

27

Составитель А Баранов

Редактор А. Маковская Техред М.яндык Корректор Г. Решетник

Заказ 6364/42

Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб;, д. 4/5

Производственно-полиграфическое предприятие, r.Óæãîðîä, ул.Проектная 4