Устройство для цифровой фильтрации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и информационноизмерительным системам и может быть использовано в системах для цифровой обработки сигналов, в частности изображений . Цель изобретения - повышение точности работы устройства. Поставленная цель достигается за счет того, что в состав устройства входят сумматоры 1-4, входной элемент задеряжи 5, элементы задержки 6,7, группа цифровых фильтров 8 второго порядка, группа умножителей 9, группы сумматоров 10,11, блок элементов И 12, вход 13, входы задания коэффициентов 14,15,16, выход 17. 6 Ш1. с S (П П со О5 СО N5 00 Udj& йл./

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

„„SU„„1363248

А1 (5ц 4 G 06 F 15/353

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

AO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ --g(+pл, У

М А BTOPCHOMV СВИДЕТЕЛЬСТВУ . @йг...,... ( . ъ

x( (21) 3977065/24-24 (22) 20.11.85 (46) 30.12.87. Бюл. Р 48 (71) Физико-механический институт им.Г.В.Карпенко (72) Л.В.Вариченко, P.Á.Ïîïîâè÷ и М.А.Раков (53) 681 .32 (088 .8) (56) Авторское свидетельство СССР

Ф 758166, кл. G 06 F 15/353, 1980.

Rabiner L.R. Schafer R.W.Recursive and попгесцтзюе realization

of digital filters designed by

frequåncó sampling techniqucs—

IEEE Trans, audio, and electro-aco

ustics, 1971, ч.AU-19, 9 3, р.200

207.. (54) УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ФИЛЬТРА

ЦИИ (57) Изобретение относится к вычислительной технике и информационноизмерительным системам и может быть использовано в систе: ах для цифровой обработки сигналов, в частности иэображений. Цель изобретения — повышение точности работы устройства. Поставленная цель достигается за счет того, что в состав устройства входят сумма" торы 1-4, входной элемент задержки 5, элементы задержки 6,7, группа цифровых фильтров 8 второго порядка, группа умножителей 9, группы сумматоров

10,11, блок элементов И 12, вход 13, ф входы задания коэффициентов 14,15,16, выход 17. 6 ил.

1363248

Изобретение относится к вычислительной технике и информационно-измерительным системам и может быть использовано в системах для цифровой обработки сигналов, в частности изображений.

Цель изобретения — повышение точности работы устройства.

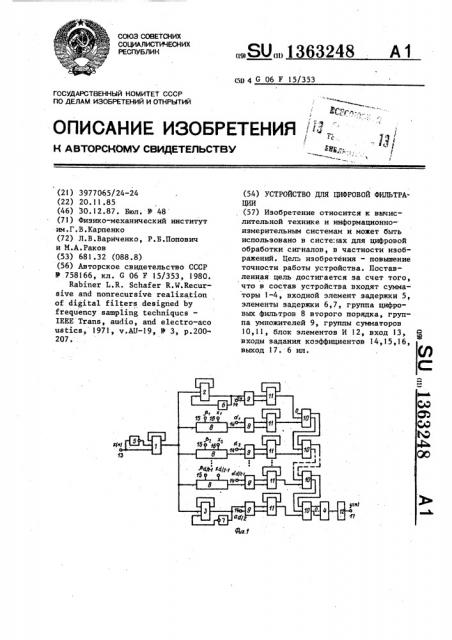

На фиг.1 представлена структур- 10 ная схема устройства; на фиг.2— схема цифрового фильтра второго порядка;на фиг.3 — схема блока элементов И; на фиг.4 — входной элемент задержки; на фиг.5 — элементы эа- 15 держки; на фиг.б — временные диаграммы, поясняющие работу устройства.

Устройство содержит (фиг.1) первый !, второй 2, третий 3 и четвертый 4 сумматоры, входной элемент 5 20 задержки, первый 6 и второй 7 элементы задержки, группу цифровых фильтров 8 второго порядка, первую группу умножителей 9, четвертую 1О и пятую 11 группы сумматоров, блок 12 элементов И, вход 13, который является входом устройства, входы 14 — 16 задания коэффициентов устройства первой, второй и третьей групп соответственно, выход 17.

Цифровой .фильтр 8 второго порядка содержит (фиг,2) элементы 18, 19 и 20 задержки соответственно первой, второй и третьей групп элементов задержки, умножители 21 и 22 сосьтветст- 35 венно второй и третьей групп умножителей, сумматоры 23, 24, 25, 26 и

27 первой, второй третьей, шестой и седьмой групп сумматоров соответственно, вход 28 и выход 29.

Блок 12 элементов И (фиг.3) содержит элемент И 30 и группу элементов

И 31. ходной элемент 5 задержки (фиг.4) 45 содержит группу сдвиговых регистров

32, группу элементов НЕ 33, тактовый вход 34 и вход 35 сброса. DR— вход регистра 32 при сдвиге вправо,.

Q g Й-й информационный выход. 50

Первый б или второй 7 элемент задержки либо элементы 18-20 задержки первой, второй или третьей группы соответственно элементов задержки (фиг.5 1 содержит регистр 36, группу элементов HE 37, тактовый вход 38 и вход 39 сброса. Буквы D u Q обозначают информационные входы и выходы соответственно регистра 36 °

Тактовые входы 38 первого и второго элементов задержки и всех элементов задержки первой, второй и третьей групп элементов задержки объединены. Объединены также входы 39 сброса первого и второго элементов задержки первой, второй и третьей групп элементов задержки.

Все сумматоры на фиг.1, 2 являются р-разрядными, множимое и множитель во всех умножителях - также р-разрядные слова. Связь, перечеркнутая косой чертой, обозначает связь р-разрядов, т.е.первый выход соединен с первым входом, второй выход— с вторым входом,..., р-й вход — с р-м входом.

Структурная схема устройства для цифровой фильтрации описывается выражением

cf/2- f

H(Z) (1-Z ) ((1-Z) а,+ .С (1- Е+

Ьз= 1

+ Z ) - (1+р Z) а(+(1+Z) а, 11,(1) коэффициенты для которого находят следующим образом:

gf-1 а„, = d С h(n)f =о

a 2Re (a 1; (2) у = 2Re t Å

Все вычисления в выражениях (2) и (1) при подстановке вместо переменной Z некоторого числа проводятся в кольце целых комплексных чисел по модулю числа 2 — 1. Через f обозначен первообразный корень степени d из единицы в указанном кольце, т.е. такой элемент, для которого число

d является наименьшим положительным числом с условием = 1. Через Х обозначен элемент, обратный элементу

Х в кольце многочленов от переменной.

Z над кольцом целых комплексных чисел по модулю 2 — 1, Re ) — действительP ная часть числа; h(n) — промасштацированные и округленные до целых (действительных) чисел отсчеты импульсной характеристики устройства; d— длина импульсной характеристики, причем d — длина импульсной характеристики, причем Й должно делить нацело

2 Е+ з 13

Для того, чтобы на выходе устройства

d s

Y(n) = . h(k)X(n-k)

k-o получалась правильная арифметическая свертка, необходимо, исходя из возможных значений X(n) и h(n) выбрать соответствующий модуль М 2 — 1, который выбирается согласно выражению:

63248

10

Часть устройства, состоящего из первого сумматора 1 и входного элемента 5 задержки,.реализует передаточную функцию 1-2, что является

d первым сомножителем в (1). Это равносильно реализации следующего соотношения между входной Х(1) и выходной U(1) последовательностями для данной части устройства: с! (M-1) /2 > /X (n) /шах 2 /h (k) /. (3) =о

При выборе модуля согласно (3) 15 результат может находиться в пределах от 0 до М-1. Число 0

Устройство для цифровой фильтрации работает следующим образом.

Перед началом работы производится сброс в нуль входного элемента 5 30 задержки, первого 2 и второго 3 эле ментов задержки, элементов 18;19 и 20 .задержки соответственно первой, второй и третьей групп элементов задержки (фиг.б), т.е. принимается, что

Х(-d)=X(-d+1)=X(-d+2) =

=...=(-1)=0.1-й(1=0,1,2,...) такт работы устройства начинается с 4О приходом на его вход 13 отсчета

X(1) . Далее происходит последовательное срабатывание комбинационных схем от входа 13 к выходу 17 устройства. В процессе срабатывания комбинационных схем никакой записи информации в элементы 2,3,5,18,19,20 задержки не происходит. На входы соответствующих комбинационных схем поступают значения с выходов элементов 5р

2,3,5,18,19,20 задержки, записанные в них в (1-1)-м такте (1=1,2,...)..

В случае нулевого такта на выходах укаэанных элементов задержки — нулевые значения после начального сброса. 55

Запись информации в элементы задержки осуществляется с помощью тактовых импульсов, подаваемых на входы

34 и 38 (фиг.б).

U (1) =Х (1) -Х (1-d)

На вход 13 устройства поступает отсчет Х(1). На выходе входного элемента 5 задержки перед началом 1-ro такта имеется задержанный отсчет—

X(1-d). Знак минус реализуется введением группы элементов НЕ 16.

Сумматор 1 производит сложение

Х(1) и -Х(1-d) по модулю 2Р- 1.

Сложение. происходит эа время, равное последовательному суммированию двух пар слов. Сначала суммируются поступающие числа, причем на выходе переноса сумматора 1 может появиться сигнал логической единицы. Так как вес единицы равен 2, что совпадает с единицей по модулю 2Р-1, то выход переноса сумматора 1 связан с его входом переноса. Появившийся перенос прибавляется к результату суммы сумматора 1. Таким образом, на выхо" дах суммы сумматора l имеем число

U(1) = X(1) — Х(1-d) по модулю 2Р- 1, которое поступает на входы второго

2 и третьего 3 сумматоров и цифровых фильтров 8 второго порядка.

Далее i=A (з =2,d/2) цифровой фильтр 8 второго порядка реализует передаточную функцию (l-у,,Z +

-1

+ Z ) (1+ р. Z), что является со" множителем одного из слагаемых вто— рого сомножителя в выражений (! ).

Это равносильно реализации следующего соотношения между входной U(1) и выходной V(1) последовательностями для цифрового фильтра второго порядка:

V(1)= у, V(1-1)-V(1-2)+U(1) +

+ y „U(1-1) .

На вход 28 цифрового фильтра второго порядка поступает отсчет U(1)

= Х(1)-Х(1-d).На выходе элемента 18 задержки перед началом 1-го такта

5 !3632

I имеется отсчет U(1-1), на выходе элемента 19 задержки — отсчет Ч(1-1), на выходе элемента 20 задержки — отсчет -V(1-2) (так как используются инверсные выходы элемента 20 задержки).

Умножитель 22 формирует 2р-разрядное произведениеp;, U(1-1) . Так как

2 Г совпадает с единицей по модулю 10

2 -1, то 2 (1сО,р-1) совпадает

P Р -1с с 2", .Поэтому для приведения полученного произведения по модулю 2 — 1 необходимо к младшим р разрядам прибавить старшие р разрядов. Это вы- 15 полняет сумматор 27. Таким образом, умножитель 22 и сумматор 27 вместе образуют умножитель по модулю 2 - 1.

Сумматор 23 складывает величины

U(1) и р;, U(1-1) по модулю 2 — р 20 а сумматор 25 - величины V(1) +

+P;, U(1-1) и -V(1-2) . Умножитель 21

Перенос d/2-го сумматора 10 четвертой группы прибавляе!1ся к числу, полученному на его выходах суммы, с помощью четвертого сумматора 4, Блок 12 элементов И служит для устранения неоднозначности представления нуля по модулю 2 — 1. Эта неP однозначность возникает из-эа равенства числа .11...1 с нулем по мор раа

P дулю 2 — l.

Блок 12 заменяет это число на нуль, а остальные числа пропускает без изменений. Действительно при, укаэанном числе на выходе элемента

И 30 и на выходах элементов И 31 логические нули. В остальных случаях на выходе элемента И 30 — логическая единица и разряды числа пропускаются на выходы элементов И 31 без изменений. и сумматор 26 формируют произведение ;, V(1-1) по модулю 2 — 1. Сумматор

24 складывает величины U(1) +

+Д U(l-1)-V(1-2) и ъ V(1-1) .

1- 1 0 i-1

Второй сумматор 2 и первый элемент 6 задержки реализует передаточ- 30 ную функцию (1-Е) ", являющуюся соМНо жителем первого слагаемого второго сомножителя в выражении (1!.

Третий сумматор 3 и второй элемент

7 задержки реализуют передаточную

-1 о функцию (1+Е), являющуюся сомножителем последнего слагаемого второго сомножителя в выражении (1).

Умножители 9 и соответствующие им сумматоры ll формируют проиэведе- 40 ния величин на выходе второго сумматора 2, выходах цифровых фильтров 8 второго порядка и выходе третьего сумматора 3 на соответствующие коэффициенты первой группы а, а,, с!,..., 45

,у(, а g(2 °

Сумматоры 10 четвертой группы сум. маторов складывают полученные произведения. Первый из сумматоров четвертой группы складывает первые два произведения, затем второй из сумматоров четвертой группы к полученной сумме прибавляет третье произведение и т.д. Перенос k-ro (k=1,d/2-1) сумматора 10 четвертой группы,. имеющий вес единицы по модулю 2 - 1, передается на вход переноса (k+1)-ro сумматора этой же группы.

На выходе 17 получаем отсчет

7(1) выходной последовательности .устройства для цифровой фильтрации.

После этого производится запись в элементы 5,6,7,18,19,20 задержки значений отсчетов, сформировавшихся в 1-м такте на их входах, для использования этих значений в (1+1)"м такте. На этом 1-й такт работы устрой-, ства заканчивается.

Формула изобретения

Устройство для цифровой фильтрации, содержащее первый, второй и третий сумматоры, входной элемент задержки, первый и второй элементы задержки, первую, вторую и третью группы умножителей, первую, вторую, третью и четвертую группы сумматоров, первую, вторую и третью группы элементов задержки, причем выход входного элемента задержки подключен к первому входу первого сумматора, выход суммы которого подключен к первому входу i-ro (i=2,d/2, d— длина импульсной характеристики) сумматора первой группы, входу i-го элемента задержки первой группы, первым входам второго и третьего сумматоров, выходы суммы которых подключены к входам соответственно первого и . второго элементов задержки и к первым входам соответственно первого и (d/2 + 1)-го умножителей первой группы, вторые входы которых явля1363248 ются входами задания соответственно первого и d/2+1)-ro коэффициентов первой группы устройства, входом, задания i-ro коэффициента первой группы которого является первый вход

i-ro умножителя первой группы, второй вход которого подключен к выходу

i-ro сумматора второй группы,и соединен с входом i-го элемента задерж- 1р ки второй группы, вход которого подключен к первому входу i-ro умножителя второй группы и входу i-ro элемента задержки третьей группы, выход которого подключен к первому 1 Г-, входу i-ro сумматора третьей группы, выход которого подключен к первому входу i-ro сумматора второй группы, выход переноса которого подключен к входу переноса i-ro сумматора вто- 2р. рой группы, выход переноса.i-го сумматора третьей группы подключен к входу переноса i-ro сумматора треть; ей группы, вторрй вход которого подключен к выходу i-ro сумматора первой 25 группы, выход переноса которого подключен к входу переноса i-ro сумматора первой группы, выход i-ro элемента задержки первой группы подключен . к первому входу i-ro .умножителя тре- Зр тьей группы, второй вход которого является входом задания i-ro коэффициента второй группы устройства, входом задания i-го коэффициента третьей группы которого является вто- З5 рой вход i-ro умножителя второй группы, выход переноса первого сумматора подключен к входу переноса первого сумматора, второй вход которого соединен с входом входного элемента sa- 4p держки и является информационным входом устройства, выходы первого и второго элементов задержки подключены к вторым входам соответственно второго и третьего сумматоров, выхо- 45 ды переноса которых подключены к .входам переноса соответственно второI

ro и третьего сумматоров, выход переноса и выход суммы i-го сумматора четвертой группы пОдключены соответственно к входу переноса и первому входу (i+1)-го сумматора четвертой группы, о т л и ч а ю щ е е с я тем, что, с целью повышения точности, в него введены пятая, шестая и седьмая группы сумматоров, четвертый сумматор и блок элементов И, выходы старших и младших разрядов j-ro (i=

=2,d/2+2) умножителя первой группы под ключены соответственно к первому и второму входам j-ro сумматора цятой группы, выход переноса которого подключен к входу переноса j-ro сумматора пятой группы, выход суммы первого сумматора пятой группы под-, ключен к первому входу первого сумматора четвертой группы, вход переноса которого соединен с первым входом четвертого сумматора и является входом задания логического нуля устройства, информационным выходом которого является выход блока элементов И, входы которого подключены к выходам соответствующих разрядов четвертого сумматора, второй вход и вход переноса которого подключены соответственно к выходу суммы и выходу переноса d/2-ro сумматора четвертой группы, второй вход 1-го(1=2,d/2+1) сумматора которой подключен к выходу (1+1)-ro сумматора пятой группы, выходы старших и младших разрядов

i-x умножителей второй и третьей групп подключены соответственно к первому и второму входам i-х сумматоров соответственно шестой и седьмой групп, выходы которых подключены к вторым входам i-x сумматоров соот ветственно второй и первой rрупп а выходы переносов i-x сумматоров шес" той и седьмой групп подключены к входам переноса i-х сумматоров со" ответственно шестой и седьмой групп.

1363248

1363248

Рагря3ы 5т0нсго 0I77c4Pma к о, йи6ерсные разря0ы 3аберяаннсм сесчета ц, 39

)363248

17

Составитель А.Баранов

Редактор А.Маковская Техред М.Дидык Корректор В.Гирняк

Заказ 6364/42 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий !

13035- Москв,а Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.ужгород, ул. Проектная, 4