Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕаЪБЛИК (19) (11) (11 4. 6 11 С 19/00

fr>:

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4066009/24-24 (22) 11.03.86 (46) 30.12.87. Бюл. У 48 (72) Ю.М. Сазонов и В.Н. Макеев (53) 681.327.6(088.8) (56) Авторское свидетельство СССР

У 515154, кл. G 11 С 19/00, 1975.

Авторское свидетельство СССР

N 932566, кл. 6 11 С 19/00, 1982. (54) БУФЕРНОЕ ЗАПОМИНА10ЩЕЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике, а именно к устройствам для обработки и хранения цифровой информации и может быть использовано для согласования информационных потоков устройств, работающих с pasной скоростью обработки информации.

Цель изобретения — повышение быстродействия устройства. Устройство содержит входной регистр 1, накопитель

2,выходной регистр 3, блок управления

4, мультиплексор 5, счетчик 6 адреса записи, счетчик 7 адреса считывания, регистр 8 внешнего адреса. Устройство позволяет за счет применения его для согласования выходного информационного потока многоканальной информационно-измерительной системы с вычислительным комплексом ускорить обработку информации и упростить алгоритм работы вычислительного ком& лекса. 2 ил.

1363309

1Г

1

Изобретение относится к вычислительной технике, а именно к устройствам для обработки и хранения цифровой информации, и может быть использовано для согласования информационных потоков устройств, работающих с разной скоростью обработки информапии.

Целью изобретения является повышение быстродействия устройства.

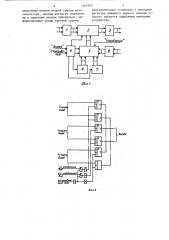

На фиг. 1 приведена структурная схема устройства; на фиг. 2 — схема мультиплексора, вариант исполнения.

В состав буферного запоминающего устройства входит входной регистр 1, накопитель 2, выходной регистр 3, блок 4 управления, мультиплексор 5, счетчик 6 адреса записи, счетчик 7 адреса считывания, регистр 8 внешнего адреса.

Устройство работает следующим образом.

При поступлении сигнала "Запись" блок 4 управления формирует импульсы обращения к накопителю 2, через мультиплексор 5 подключает выходы счетчи. ка адреса записи 6 к адресным входам накопителя 2, и информация из входного регистра 1 записывается в накопитель 2 по адресу, определяемому состоянием счетчика 6 адреса записи.

При поступлении сигнала "Считывание" блок 4 управления формирует импульсы обращения к накопителю 2; если усто ройство-приемник информации устанавливает на входе "Управление" низкий потенциал, то блок 4 управления через мультиплексор 5 подключает выходы счетчика 7 адреса считывания к адресным шинам накопителя 2 и в выходной регистр 3 считывается информация, хранившаяся в накопителе 2 по адресу, определяемому состоянием счетчика 7 адреса считывания; если же устройство — приемник информации устанавливает на входе "Управление" высокий потенциал, то мультиплексор 5 подключает выходы регистра 8 внешнего адреса к адресным входам накопителя 2 и в выходной регистр 3 считывается информация, хранившаяся в накопителе 2 по адресу, определяемому состоянием триггеров регистра 8 внешнего адреса.

Таким образом, использование изобретения позволяет существенно повысить быстродействие устройства. Применение устройства для согласования выходного информационного потока многоканальной информационно-измерительной системы с вычислительным комплексом, испольэуемьп1 для обработки получаемой информации, позволяет ускорить обработку информации и упростить алгоритм работы вычислительного комплекса. Например, в одном иэ возможных вариантов осуществление выборки из буферного запоминающего устройства сначала только одного или нескольких каналов, информация которых имеет первостепенкое значение для прово" димых измерений, позволяет быстро отыскивать наиболее важные или критические изменения получаемой по этому каналу или каналам информации и выборку остальных каналов производить в соответствии с получаемой конкретной информацией. В противном случае пришлось бы сначала считать весь массив информации из буферного запо" минающего устройства и только после этого производить ее анализ.

Формула изобретения

Буферное .закомикающее устройство, содержащее накопитель, информационные входы которого подключены к выходам входного регистра, входы которого яв- ляются информационными входами устройства, информационные выходы накопителя соединены с входами выходного регистра, выходы которого являются информационными выходами устройства, блок управления, входы управления записью и считыванием которого являются соответственно входами разрешения записи и считывания устройства, первый, второй и третий выходы блока управления подключены соответственно к управляющему входу накопителя, входам счетчиков адреса записи и адреса считывания, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены мультиплексор, регистр внешнего адреса, причем четвертый и пятый выходы блока управления подключены соответственно к первому и второму управляющим входам мультиплексора, третий управляющий вход которого является управляющим входом устройства, выходы счетчика адреса записи подключены

K информационным входам первой группы мультиплексора, выходы счетчика адреса считывания подключены к инфор з

1363309 мационным входам второй группы мультиплексора, выходы которого подключены к адресным входам накопителя, информационные входы третьей группы мультиплексора соединены с выходами регистра внешнего адреса, выходы которого являются адресными выходами устройства.