Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть ис3 If 5 пользовано для построения запоминающих устройство (ЗУ) повышенной надежности . Целью изобретения является повьппение надежности устройства. Устройство содержит накопитель 1, первый и второй шифраторы 7,15, первый, второй и третий регистры 11,12,28, первый и второй блоки 18,24 сумматоров по модулю два, блок 16 инвертирования , первый и второй коммутаторы 6,22, дешифратор 25, блок 14 коррекции , группу 29 элементов И, элемент И 31. Повьшгение надежности устройства осуществляется путем контроля . всех цепей коррекции ошибок и цепей формирования контрольных разрядов кодового слова. 1 ил. i W С

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU,,1363312 (51)4 С 11 С 29/00

ОПИСАНИЕ И306РЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

М АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ (21) 4020019/24-24 (22) 06.02 ° 86 (46) 30.12.87. Бюл. Ф 48 (71) Минский радиотехнический институт (72) Н.И.Урбанович (53) 681.327.6 (088.8) (56) Авторское свидетельство СССР

N - 769641, кл. G 11 С 29/00, 1980.

Авторское свидетельство СССР

N - 1059630, кл. G 11 С 29/00, 1983. (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ (57) Изобретение относится к вычислительной технике и может быть использовано для построения запоминающих устройство (ЗУ) повышенной надежности. Целью изобретения является повышение надежности устройства. Устройство содержит накопитель 1, первый и второй шифраторы 7,15, первый, второй и третий регистры 11, 12,28, первый и второй блоки 18,24 сумматоров по модулю два, блок 16 инвертирования, первый и второй коммутаторы

6,22, дешифратор 25, блок 14 коррекции, группу 29 элементов И, элемент

И 31. Повышение надежности устройства осуществляется путем контроля всех цепей коррекции ошибок и цепей формирования контрольных разрядов кодового слова. 1 ил.

1 13633

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств (ЗУ) повышенной надежности..

Целью изобретения является повышение надежности устройства..

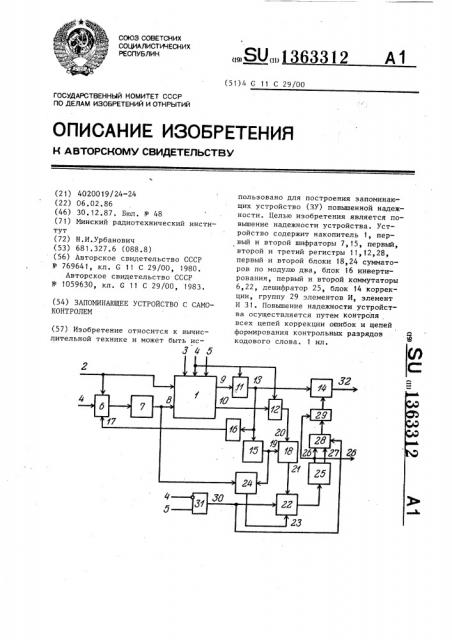

На чертеже изображена схема запоминающего устройства с самоконтролем.

Устройство содержит накопитель 1, информационные входы 2, адресные входы 3, вход 4 записи-считывания, вход 5 выборки, первый коммутатор 6,. первый шифратор 7, входы контрольных разрядов 8, выходы 9. информационных и 10 контрольньгх разрядов накопителя

1, первый 11 и второй 12 регистры, входы 13 блока-коррекции 14, второй шифратор 15, блок 16 инвертирования с выходами 17, первый блок 18 сумма- 20 торов по модулю два с входами 19, 20 и выходами 21, второй коммутатор

22 с выходами 23, второй блок 24 сумматоров по модулю два, дешифратор 25 с выходами 26,27, третий регистр 28, 25 группа элементов И 29, выход 30 элемента И 31, информационные выходы 32. ,Принцип функционирования цепей самоконтроля основан на использовании свойства кода Хемминга, состоящего в том, что при правильной работе этих цепей синдромы считанного из накопителя и инверсного ему кодовых слов отличаются во всех позициях, ч т,е. также являются прямым-и инверсньпг. При неправильной работе цепей коррекции такое условие не выполняется.

Устройство работает следующим образом. 40

В режиме записи информации на входы 3-5 устройства подаются адрес опрашиваемой ячейки накопителя 1, сигнал, задающий режим, и сигнал выборки кристалла соответственна..Комму45 татор 6 пропускает на выход информационные символы,, в соответствии с которыми шифратор 7 вырабатывает контрольные символы кодового слова,.последние по входам 8 вместе с информационными символами записываются в накопитель по .поступлении сигнала разрешения записи (t ), после окончания чего (e ) цикл записи заканчивается. .В режиме считывания информации опрашиваемая ячейка выбирается как и в режиме записи. На входе 4 .присутствует противоположный логический уровень сигнала, на выходе элемента

12 2

И 31 — сигнал логической единицы. В регистры 11 и 12 с выходов накопителя 9 и 10 происходит запись считанных из накопителя соответственно информационных и контрольных символов кодового слова. Считанные информационные символы поступают в шифратор

15, а инверсные информационные символы через коммутатор 6 — в шифратор

7, где происходит формирование новьгх наборов контрольных символов.. Сформированные шифратором 15 контрольные символы в блоке 18 сумматоров поразрядно сравниваются со считанными из накопителя контрольными разрядами.

На вьгходах 21 таким образом формируется признак ошибки (синдром). Если в считанных.из накопителя символах нет ошибок, то синдром равен нулю, и отличен от нуля — в противном случае. Синдром происходит через коммутатор 22 и дешифрируется дешифратором

25, результат чего записывается в регистр 28. В момент времени t< изменяется сигнал на входе 5, на выходе элемента И 31 — нулевой сигнал, разрешающий прохождение через коммутатор 22 двоичных символов, установленных на выходах блока 24, где к этому времени уже сформирована сумма по модулю два контрольных символов, выработанных шифраторами 7 и 15. Если шифраторы и предшествующие им цепи прохождения соответствующих сигналов функционируют нормально, то на вы.ходах блока 24 присутствуют единичные символы..

Если все цепи контроля не содержат неисправностей (включая дешифратор), то на выходе 26 дешифратора 25 (выход 26 — обычный выход дешифратора, формирующий единичный сигнал, если на всех его входных шинах — еди- ничные сигналы) присутствует единичный сигнал, который при наличии ошибки в слове данных позволяет исправить эту ошибку в блоке 14 единичным сигналом с выхода регистра 28 через элементы И 29. При отсутствии ошибок в слове данных на выходах всех элементов И 29 — нулевые сигналы и изменений информационных символов не происходит.

Если же к моменту времени сз с выхода дешифратора 25 на управляющий выход 26 устройства не поступит единичный .сигнал, то это соответствует наличию ошибки в цепях контроля. По

1363312

Гоставитель О.Исаев

Техред. А.Кравчук

Корректор Л,Патай

Редактор Л. Веселовская

Заказ 6370/46

Тираж 588

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Подписное

Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная,4 такому управляющему сигналу процессор (не показан) останавливает выполнение программы. Производится локализация места неисправности. При от5 сутствии ошибки данные в период времени сэ-г. поступают на выходы 32 устройства.

Формула и з обретения

Запоминающее устройство с самоконтролем, содержащее первый коммутатор, информационные входы первой группы которого соединены с выходами блока инвертирования, а информационные входы второй группы являются информационными входами устройства и подключены к входам информационных разрядов накопителя, входы контрольных разрядов которого соединены с выходами первого шифратора, входы которого подключены к выходам первого коммутатора, управляющий вход которого является входом записи считывания устройства и соединен с 26 одноименным входом накопителя и с синхровходами первого и второго регистров, информационные входы которых подключены соответственно к выходам информационных и контрольных разрядов накопителя, адресные входы и вход выборки которого являются одноименными входами устройства, выходы первого регистра соединены с входами первой группы блока коррекции и с входами второго шифратора, выходы которого подключены к входам первой группы первого блока сумматоров по модулю два, входы второй группы которого соединены с выходами второго регистра, а выходы подключены к информационным входам первой группы второго коммутатора, выходы которого соединены с входами дешифратора, выходы блока коррекции являют1 ся информационными выходами устройства, о т л и ч а ю щ е е с я . тем, что, с целью повышения надежности, в устройство введены второй блок сумматоров по модулю два, элемент И, группа элементов И.и третий регистр, причем информационные входы и синхровход третьего регистра соединены соответственно с выходами дешифратора и элемента И, входы которого подключены к входам записи-считывания и:-" выборки устройства, один из выходов дешифратора является выходом признака ошибки устройства и соединен с одними входами элементов И группы, другие входы которых подключены к выходам третьего регистра, а выходы соединены с входами второй группы блока коррекции, входы первой и второй групп и выходы второго блока сумматоров по модулю два подключены соответственно к выходам первого и второго шифраторов и к информационным входам второй группы второго ком. мутатора, управляющий вход которого соединен с выходом элемента И, входы блока инвертирования подключены к выходам первого регистра.