Умножитель частоты

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике . По отношению к авт. св. № 1148088 достигается цель изобретения - повьшение точности умножения частоты. Умножитель частоты содержит делители 1 и 5 частоты, счетчик 2, реверсивный счетчик 3, блок сравнения 4, триггеры 6 и 7, эл-ты ИЛИ 8 и 10, зл-ты И 9 и 11 и эл-ты запрета 12 и 13. Цель достигается путем обеспечения уменьшения сбоев в работе умножителя частоты с помощью введенных зл-тов запрета 12 и 13. 1 ил. со 05 СО 4 ГС 4 ГЧ

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (11) 3424 А 2 (11 4 Н 03 В 19/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 1148088 (21) 4100542/24-09 (22) 04.08.86 (46) 30.12.87. Бюл. N 48 (72) В.В.Орловский, В.И.Тепляков и И.Ф.Тепляков (53) 621.373 ° 42(088.8) (56) Авторское свидетельство СССР

У 1148088, кл. Н 03 В 19/00, 1982. (54) УИНОЖИТЕЛЬ ЧАСТОТЫ (57) Изобретение относится к радиотехнике. По отношению к авт. св.

9 1148088 достигается цель изобретения — повышение точности умножения частоты. Умножитель частоты содержит делители 1 и 5 частоты, счетчик 2, реверсивный счетчик 3, блок сравнения 4, триггеры 6 и 7, эл-ты ИЛИ 8 и 10, эл-ты И 9 и 11 и эл-ты запре" та 12 и 13. Цель достигается путем обеспечения уменьшения сбоев в работе умножителя частоты с помощью введенных эл-тов запрета 12 и 13. 1 ил.

1363424

Изобретение относится к радиотехнике и может использоваться для умножения частоты в аппаратуре приемапередачи информации и в системах син5 хронизации устройств вычислительной техники и является усовершенствованием изобретения по авт. св.

М 1148088.

Цель изобретения — повышение точности умножения частоты путем уменьшения сбоев в работе.

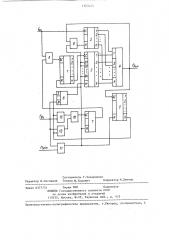

На чертеже представлена структурная электрическая схема предложенного умножителя частоты.

Умножитель частоты содержит первый делитель 1 частоты, счетчик 2, реверсивный счетчик 3„ .блок 4 сравнения, второй делитель 5 частоты, первый триггер 6, второй триггер 7, первый элемент ИЛИ 8, первый элемент

И 9, второй элемент ИЛИ 10, второй элемент И 11, первый элемент запрета 12, второй элемент запрета 13.

Умножитель работает следующим об-. 25 разом.

При подаче сигнала "Пуск." на один из входов второго элемента И 11 сигнал входной частоты f „ через второй элемент И 11 устанавливает в началь- 3д ное состояние счетчик 2, первый и второй делители 1 и 5, реверсивный счетчик 3 и второй триггер 7. Сигнал опорной частоты f „ поступает на вход о«« счетчика 2. Прн совпадении выходных

35 кодов счетчика 2 и реверсивного счетчика 3 на выходе блока 4 сравнения появляется сигнал выходной частоты

f, который поступает на счетный ьь««« вход второго делителя 5 и через пер- 40 вый элемент ИЛИ 8 устанавливает в в состояние "0" счетчик 2.

При переполнении второго делителя 5 импульс переполнения с его выхода поступает через второй элемент, за- 45 прета «3 и второй элемент ИЛИ 10 на вход второго триггера 7 и устанавливает его в единичное состояние, его выходной сигнал через первый элемент

H 9 разрешает поступление на вход первого делителя 1 сигналов опорной частоты f „ . Сигналь« переполнения с выхода первого делителя 1 поступают на счетный вход реверсивного счетчика 3, Изменение кода на выходах ре1 версивного счетчика 3 вызывает соответствующее изменение выходной частоты. Процесс изменения кода продолжается до момента прихода на счетный вход второго триггера 7 через первый элемент запрета 12 и второй элемент

ИЛИ 10 импульса входной частоты f „, равного по длительности импульсу переполнения второго делителя 5 частоты.

При поступлении импульса входной частоты и импульса переполнения второго делителя 5 частоты на вход второго триггера 7 с другой последовательности процесс изменения кода реверсивного счетчика 3 происходит аналогично, при этом реверсивный счетчик 3 переходит из режима сложения в режим вычитания, который задает первый триггер б. Если эти импульсы приходят одновременно, то оба элемента запрета 12 и 13 оказываются закрыты и на второй элемент ИЛИ 10 импульсы не поступают.

Если же импульсы совпадают частично, то общая их часть окажется запрещенной и на вход второго триггера 7 поступят один за другим два импульса, первый из которых переведет его в единичное состояние, а второй сразу же возвратит его в исходное состояние, т.е. код реверсивного счетчика 3 не изменится, сбоя в работе умножителя не чроизойдет, и выходная частота

f „„ останется неизменной.

Формула изобретения

Умножитель частоты по авт.св.

N - 1148088, отличающийся тем, что,. с целью повышения точности умножения частоты, первый вход второго элемента И и другой установочный вход первого триггера объединены с первым входом второго элемента ИЛИ через введенный первый элемент запрета, выход второго делителя частоты подключен к второму входу второго элемента ИЛИ через введенный второй элемент запрета, при этом входы первого и второго элементов запрета также соединены соответственно с входами запрета второго и первого элементов запрета.

1363424

Составитель Г,Захарченко

Редактор И.Сегляник Техред М.Ходанич Корректор M.Äåì÷èê

Заказ 6377/51 Тираж 900 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35,. Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная, 4