Умножитель частоты

Иллюстрации

Показать всеРеферат

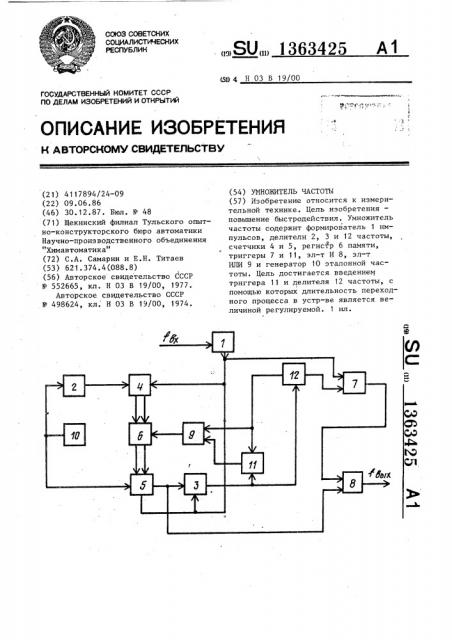

Изобретение относится к измерительной технике. Цель изобретения - повышение быстродействия. Умножитель частоты содержит формирователь 1 импульсов , делители 2, 3 и 12 частоты, счетчики 4 и 5, регис р 6 памяти, триггеры 7 и 11, эл-т И 8, эл-т ИЛИ 9 и генератор 10 эталонной частоты . Цель достигается введением триггера 11 и делителя 12 частоты, с помощью которых длительность переходного процесса в устр-ве является величиной регулируемой. 1 ил. (Л со о оо 4 ГО СП

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (58 4 Н 03 В 19/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ 1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ (21) 4117894/24-09 (22) 09.06.86 (46) 30.12.87. Бюл. ¹ 48 (71) Щекинский филиал Тульского опытно-конструкторского бюро автоматики

Научно-производственного объединения

"Химавтоматика" (72) С.А. Самарин и Е.Н. Титаев (53) 621.374.4(088.8) (56) Авторское свидетельство СССР № 552665, кл. Н 03 В 19/00, 1977.

Авторское свидетельство СССР

¹ 498624, кл. Н 03 В 19/00, 1974.

„„SU„„1363425 А1 (54) УМНОЖИТЕЛЬ ЧАСТОТЫ (57) Изобретение относится к измерительной технике. Цель изобретения— повышение быстродействия. Умножитель частоты содержит формирователь 1 импульсов, делители 2, 3 и 12 частоты, счетчики 4 и 5, регистр 6 памяти, триггеры 7 и 11, эл-т И 8, эл-т

ИЛИ 9 и генератор 10 эталонной частоты . Цель достигается введением триггера 11 и делителя 12 частоты, с помощью которых длительность переходного процесса в устр-ве является величиной регулируемой. 1 ил.

63425 2 первый триггер 7, второй триггер 11 и третий делитель 12 частоты устанавливаются в исходное состояние, а на выходах элемента ИЛИ 9 и элемента, И 8 формируются по одному импульсу.

Импульсы на выходе элемента И 8 являются выходными импульсами умножителя частоты, а импульс с выхода элемента

ИЛИ 9 поступает на установочный вход регистра 6 памяти и записывает в него код числа N;,, который подается на информационные входы регистра 6 памяти с информационных выходов перво15 ro счетчика 4 импульсов. Первый счетчик 4 импульсов возвращается в исходное состояние по заднему фронту импульса, поступающего с выхода формирователя 1 импульсов. В последующих периодах умножаемой частоты описанные операции протекают аналогично.

Код числа И,, импульсов, накопленных первым счетчиком 4 импульсов в предыдущем (i-1)-ом периоде Т;, 25 умножаемой частоты с информационных выходов регистра 6 памяти, поступает на информационные входы второго счетчика 5 и устанавливает в последнем коэффициент пересчета К„, равный

30 (4) И 1Ч где n — коэффициент деления первого делителя 2 частоты.

Импульсы второй эталонной частоты

Е поступают на счетный вход перво35 го счетчика 4 импульсов, в котором эа i-ый период Т, умножаемой частоты накапливается И число импульсов второй эталонной частоты f оz

Очевидно, что

f,=n f, (5) 40

1 13

Изобретение относится к измерительной технике и может быть использовано в цифровых измерительных прибораХ и в автоматизированных системах управления производством и технологическими процессами.

Цель изобретения — повышение быстродействия.

На чертеже приведена структурная схема умножителя частоты. .Умножитель частоты содержит формирователь 1 импульсов, первый делитель 2 частоты, второй делитель 3 частоты, первый счетчик 4, второй счетчик 5, регистр 6 памяти, первый триггер 7, элемент И 8, элемент ИЛИ 9, генератор 10 эталонной частоты, второй триггер 11, третий делитель 12 частоты.

Умножитель частоты работает следующим образом.

Импульсы с выхода генератора 10 эталонной частоты f, поступают на счетный вход второго счетчика 5 и на вход первого делителя 2 частоты, на выходе которого формируются импульсы второй эталонной частоты f, равной:

fO1

О2 (1) Следовательно, частота f; следования импульсов на выходе второго счетчика 5 с учетом (1} — (4) равна, (2) N.=f Т = —" — ° Т

02

О1

n ° f; (3) 45

По окончании:ь-го периода Т. умножаемой частоты f на выходе формирователя 1 импульсов появляется короткий импульс, который поступает на 50 уста«<овочный< вход первого счетчика 4 импульсов, установочный вход второго делителя 3 частоты, установочный вход

ròoðoãî счетчика 5, первый вход первого триггера 7, первый вход элемента . ИЛИ 9, первый вход второго триггера 11 и установочный вход третьего делителя 12 частоты. При этом, второй счет чик 5, второй делитель 3 частоты, Импульсы с выхода второго счетчика 5 поступают на счетныи вход второго делителя 3 частоты, на счетный вход третьего делителя 12 частоты, на второй вход триггера 11 и через первый вход элемента И 8 поступают на выход умножителя.частоты, формируя выходную частоту f b<„, равную

f<, до появления сигнала на выходе

<1 третьего делителя 12 частоты или до появления сигнала на выходе формирователя 1 импульсов. Из выражения (5) следует, что при указанных условиях выходная частота f ы„ в п раэ больше умножаемой частоты f;, В случае, если до окончания текущего периода Т, умножаемой частоты с выхода второго счетчика 5 успевает пройти и импульсов частоты f„ на з 13634 счетный вход второго делителя 3 частоты, то на выходе последнего появляется импульс, опрокидывающий второй триггер 11 и параллельно поступаю5 щий на счетный вход третьего делителя частоты 12. Появляющийся при этом на выходе второго триггера 11 сигнал через второй вход элемента ИЛИ 9 поступает на установочный вход регистра б памяти. В результате чего изменяющийся код с информационных входов счетчика 4 импульсов через регистр 6 памяти без задержки поступает на информационные входы второго счетчика

5, изменяя коэффициент пересчета

K„(t) последнего по мере поступления импульсов с выхода первого делителя

2 частоты на счетный вход счетчика 4 импульсов. При этом, коэффициент пе- 2р ресчета равен

25 происходит блокировка выхода умножителя частоты на время, равное разности (Т; -t, ), задаваемое коэффициентом и,. Таким образом, длительность переходного процесса в предлагаемом устройстве является величиной регулиг 1 руемой (=Т; =и 1 Т... что позволяет улучшить характеристики устройства подбором оптимального значения коэф-, фициента и,, в то время как в известном устройстве длительность с переходного процесса не регулируется (=Т;).

В момент окончания текущего i-ro

I периода Т; умножаемой частоты импульс с выхода формирователя 1 импульсов переводит умножитель частоты в исходное состояние, после чего цикл умножения частоты повторяется.

Формула и з о б р е т е н и я (б) ((02 при условии

Т 6t; CÒ у

\ где t < — интервал времени от момента начала текущего i-го периода дп

Т умножаемой частоты до те-! кущего момента времени.

Аналогично выражению (5) имеем

fo< fo( вы K (t) Е ипри t =Т, и

f (i)= — = n,h вых Т

1 (9) 40

Сформированная таким образом выходная частота f,„ поступает на выход умножителя частоты до появления сигнала на выходе третьего делителя 12 45 частоты или до появления сигнала на выходе формирователя 1 импульсов. Импульс на выходе третьего делителя 12 частоты, коэффициент деления которого равен п,, появляет- 50. ся, когда число импульсов, поступающих на счетный вход третьего делителя 12 частоты с выхода второго делителя 3 частоты, станет равным и т.е. через время t;, равное

=и ° 1 Т, . (10)

Если текущий период Т умножаемой

1 ( частоты превышает величину t, то

Умножитель частоты, содержащий последовательно соединенные генератор эталонной частоты, первый делитель частоты, первый счетчик и регистр памяти, последовательно соединенные первый триггер и элемент И, второй вход которого соединен с входом второго делителя частоты, а также второй счетчик, счетный вход которого соединен с выходом генератора эталонной частоты, и элемент ИЛИ, при этом установочный вход первого счетчика соединен с установочными входами второго счетчика и второго делителя частоты, первыми входами триггера и элемента ИЛИ и является входом умножаемого сигнала умножителя частоты, отличающийся тем, что, с целью повышения быстродействия, введены второй триггер, и третий делитель частоты, установочный вход которого соединен с первым входом второго триггера и с первым входом элемента ИЛИ, информационные выходы регистра памяти соединены с информационными входами второго счетчика, выход которого соединен с входом второго делителя частоты, выход второго делителя частоты соединен с входом третьего делителя частоты и вторым входом второго триггера, выход которого соединен с вторым входом элемента ИЛИ, выход. третьего делителя частоты соединен с вторым входом первого триггера, выход элемента ИЛИ вЂ” с установочйым входом регистра памяти, а выход элемента И является выходом умножаемого сигнала умножителя частоты.