Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (51) 4 Н 03 М 1/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

"on авиа. 1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3837396/24-09 (22) 04.01.85 (46) 30.12.87. Бюл. У 48 (72) Г,Б.Гофман, С.А.Джелаухов, Ю.Н.Залевский и В.В.Славянинов (53) 621.396.96 (088.8) (56) Кузьмин С.З. Цифровая обработка радиолокационной информации. M,.:

Сов.радио, 1967, с. 149, рис.2.18.

Титце У.,111енк К. Полупроводниковая схемотехника/ Пер. с англ. М.:

Мир, 1982. с. 360. рис.20.25, (54) (57) 1 ° АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий последовательно соединенные компаратор и блок дискретизации, причем вход компаратора и тактовый вход блока дискретизации являются входом и тактовым входом аналого-цифрового преобразователя, отличающийся тем, что, с целью улучшения разрешающей способности по времени в него введены последовательно соединенные блок .задержки и блок бланкирования, выход которого является выходом аналого-цифрового преобразователя, и блок формирования импульса паузы, выход которого соединен с вторым входом блока бланкирования, причем выход компаратора соединен с первым входом блока формирования импульса паузы, выход блока дискретизации соединен с входом блока задержки и вторым входом блока формирования. импульса паузы, при этом тактовые входы блока задержки с ф и блока формирования импульса паузы соединены с тактовым входом аналогоцифрового преобразователя.

13634

?. Преобразователь по п.1 отличающийся тем, что блок формирования импульса паузы содержит элемент HF. элемент И-НЕ и два D-триггера, причем входы элементов HE u

И-НЕ являются соответственно первым и вторым входами блока Аормирования импульса паузы, выход элемента HF. соединен с другим входом элемента

И-НЕ, выход которого соединен с

S-входом первого D-триггера, D-вход которого соединен с общей шиной, выход первого D-триггера соединен с

R-входом второго D-триггера, D-вход и Q-выход которого соединены между собой и являются выходом блока формирования импульса паузы, а соединенные С-входы первого и второго D-триггеров являются тактовым входом блока формирования импульса паузы.

3.Преобразователь поп.1,о т л и— ч а ю шийся тем,чтокомпаратор выполнен М-уровневыми имеетМ выходов .

4 ° Преобразователь по пп. 1 и 3, отличающийся тем, что блок дискретизации имеющий M входов и выходов содержит M дискретизаторов, соединенные тактовые входы которых являются тактовым входом блока дискретизации, который соединен через шифратор с входом блока задержки.

53

5. Преобразователь по пп. 1 и 3, отличающийся тем, что блок формирования импульса паузы содержит M Аормирователей, первые и вторые входы которых являются соответственно первым и вторым входами блока формирования импульса паузы, и элемент ИЛИ, М входов которого соединены с выходами М формирователей, а выход элемента ИЛИ является выходом блока формирования импульса паузы, соединенные тактовые входы M формирователей являются тактовым входом блока Аормирования импульса паузы, при этом каждый формирователь содержит элемент НЕ, элемент И-НЕ и два D -триггера, причем входы элементов НЕ и И-НЕ являются соответственно первым и вторым входами Аормирователя, выход элемента НЕ соединен с другим входом элемента И-HE выход которого соединен с S-входом первого D-триггера, D-вход которого соединен с общей шиной, выход первого D-триггера соединен с R-входом второго Р-триггера, П-вход и Ц-выход которого соединены между собой и являются выходом формирователя, а соединенные С-входы первого и второго

D-триггеров являются тактовым входом формирователя.

Изобретение относится к цифровым системам обработки информации и может быть использовано в системах отображения и обработки циАровой инфор мации. 5

Цель изобретения — улучшение разрешающей способности по времени.

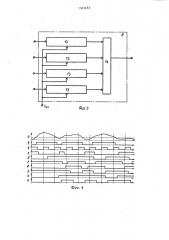

На Аиг,1 представлена структурная. электрическая схема предлагаемого аналоro-цифрового преобразователя (АЦП); на фиг.2 — схема АЦП при многоуровневом квантовании сигнала; на фиг.3 — схема блока формирования импульса паузы при многоуровневом квантовании сигнала; на фиг.4 и 5 — временные диаграммы, поясняющие его работу.

Преобразователь (фиг.1) содержит компаратор 1, блок 2 дискретизации, блок 3 задержки, блок 4 бланкирования 20 и блок 5 формирования импульса паузы, 2 включающий элемент НЕ 6, элемент

И-НЕ 7 и два D-триггера 8 и 9.

При многоуровневом квантовании сигнала преобразователь (фиг.2) содержит многоуровневый компаратор 1, блок 2 дискретизации включающий M дискретизаторов 10, шифратор 11, блок 3 задержки и блок 12 бланкирования.

Блок .5 формирования импульса паузы (фиг.3) при многоуровневом квантовании сигнала содержит M формирователей 13 паузы и элемент ИЛИ 14.

Преобразователь работает следующим образом.

Входной сигнал (фиг.4а) на выходе компаратора 1 превращается при превышении порога кван. ования, отмеченного на фиг.4а пунктирной линией, в бинарно-квантованный сигнал (фиг.4б) . В блоке 2 дискретизации, 3 13634 выполненном на D-триггере, по положительным перепадам тактовой последовательности (фиг.4в) происходит переключение.D-триггера при наличии на D-входе высокого потенциала "1".

В выходном сигнале D-триггера (фиг.4д) не все входные сигналы разрешаются, так первый и второй сигналы слились вместе.

На выходе элемента И-НЕ 7 блока 5 выделяются сигналы о паузах во входной последовательности, которые сформированы объединением проинвертирован ного элементом HE 6 сигнала с выхода компаратора 1 (фиг,4г) и сигнала с выхода блока 2 дискретизации (фиг,46).

Сигналы индикации пауз (фиг.4е) вызывают срабатывание D-триггера 8 .блока 5 (фиг.4ж). Возвращение Э-триггера 8 в исходное состояние (фиг,4ж) происходит по положительному перепаду тактовой последовательности, следующему после окончания входного сигнала (фиг.4е). Переключение D- 25 триггера 8 по положительным перепадам тактовой последовательности повторяются 0-триггером 9 (фиг,4з).

На выходе блока 5 формирования

Ф импульса паузы формируются импульсы длительностью в один дискрет. Этим сигналом производится управление блоком 4, на который подан задержанный на один дискрет (фиг.4и) в блоке

3 задержки, выполненном на триггере, сигнал с выхода блока 2. Я выходном сигнале (фиг.4к) преобразователя

- Fon

53 восстановлено разрешение всех трех сигналов, действующих на его входе.

При многоуровневом квантовании (фиг.2) преобразователь работает следующим образом.

В многоуровневом компараторе 1 происходит одновременное сравнение входного сигнала (фиг.5а) в М компараторах а разными пороговыми напряжениями (на фиг.5а отмечены пунктир,ньва линиями три уровня сравнения). .Выходные сигналы компаратора (фиг.56, s, r) попадают на М-канальный блок 2 дискретизации. Выходные сигналы блока дискретизации показаны на фиг.5д, е,ж,з,). В блоке 5 происходит выделение сигнала признака начала паузы на каждом уровне квантования (фиг.5и к, л). В блоке 5 также производится формирование пауз для каждого уровня квантования М формирователями 13 паузы (фиг.5м, н, о). Выходные сигналы формирователей 13 объединяются элементом ИЛИ 14. (фиг.5п).

В шифраторе 11, выполненном на элементах И-НЕ, формируется двухразрядный двоичный код, в свернутом виде показанный на фиг.5р.

Сигналы с выхода шифратора 11, задержанные в блоке 3 задержки (фиг.5c) на один интервал дискретизации, подаются на блок 12 бланкирования, где по сигналам с блока 5 происходит восстановление пауз (фиг.5т).

1363453

1363453

Составитель В. Калмыков

Корректор О. Кравцова

Редактор А.Огар Техред М.Диднк

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4 б д

2 д

Заказ 6379/53 Тираж 900 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва Ж-35, Раушская наб., д.4/5

t

f