Преобразователь кодов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для преобразования информации в системах передачи и обработки дискретной информации. Изобретение позволяет формировать коды регистров и коды символов в блоке памяти , чем достигается упрощение преобразователя кодов.-Преобразователь кодов содержит три регистра 1,6 и 9, умножитель 2, два дешифратора 3 и 4, блок памяти 5, блок 7 сравнения и блок 8 управления. Блок управления 8 состоит из двух триггеров, двух элементов И, счетчика-делителя и инвертора . 1 з.п.ф-лы, 2 ил. ю (Л со 05 00 4 00 ./

СОЮЗ COBETCHÈÕ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

А1 (19) (11) (5)) 4 Н 03 М 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4054952/24-24 (22) 11.04.86 (46) 30.12.87.Бюл. У 48 (72) Б.М.Шилин, А.А.Мовчан и А.И.Тихонов (53) 681.375.65 (088.8) (56) Авторское свидетельство СССР

Р 792605, кл. Н 04 1 3/04, 1980.

Авторское свидетельство СССР

9 995358, кл. Н 04 L 3/04, 1983. (54) ПРЕОБРАЗОВАТЕЛЬ КОДОВ (57) Изобретение относится к вычислительной технике и может быть использовано для преобразования информации в системах передачи и обработки дискретной информации. Изобретение позволяет формировать коды регистров и коды символов в блоке памяти, чем достигается упрощение преобразователя кодов.-Преобразователь кодов содержйт три регистра 1,6 и 9, умножитель 2, два дешифратора 3 и 4, блок памяти 5, блок 7 сравнения и блок 8 управления. Блок управления 8 состоит из двух триггеров, двух влементов И, счетчика-делителя и инвертора. 1 з.п.ф-лы, 2 ил.

"0 — — Ъ

1363478 ?

Изобретение относится к вычислительной технике и может быть использовано для преобразования информации в системах передачи и обработки дискретной информации.

Цель изобретения — упрощение преобразователя.

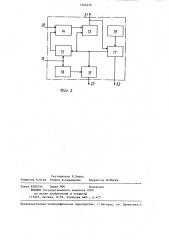

На фиг.1 представлена структурная схема преобразователя; на фиг.2 структурная схема блока управления.

Преобразователь кодов содержит первый регистр 1, умножитель 2, первый 3 и второй 4 дешифраторы„ блок 5 памяти, второй регистр 6, блок 7 сравнения, блок 8 управления и третий регистр 9. На фиг.1 обозначены управляющие 10 и информационные 11 входы преобразователя, а также выход 12 преобразователя.

Блок 8 управления содержит первый 13 и второй 14 триггеры, первый

15 и второй 16 элементы И, счетчикделитель 17 и инвертор 18. На фиг.2 обозначены первый 19 и второй 20 входы блока управления, а также первый 21, второй 22, третий 23 выходы блока управления.

Устройство работает следующим образом.

На вход 11 поступает кодовая комбинация, которая заносится в регистр

1 символов. Параллельно на входы дешифраторов 3 и 4 поступает (по входу 10) индекс типа кода. Дешифратор 3 формирует кодовое слово, соответствующее эначности поступИвшей кодовой комбинации, которое поступает на умножитель 2 и служит в качестве маски для выделения действительной кодовой комбинации из регистра 1 символов. Дешифратор 4 формирует кодовое слово, определяющее зону блока 5 памяти, в которой хранится требуемый кодовый алфавит.

По накоплении кодовой комбинации в регистре 1 символов осуществляется умножение в умножителе 2 пришедшей кодовой комбинации на константу, характеризующую размерность элементов в кодовых алфавитах, размещенных в блоке 5 памяти.

Полученный результат, а также кодовое слово, сформированное дешифратором 4, поступают на адресные входы блока 5 памяти и служат адресом кодовой комбинации в искомом алфавите, соответствующей поступив5

1 Г., 20

55 шей на вход 11 преобразователя кодовой комбинации.

По сигналу с выхода умножителя 2, поступающему на второй вход блока 8 управления, на первом выходе блока 8 управления формируется сигнал, разрешающий выборку кодовой комбинации иэ блока 5 памяти.

В выбранной кодовой комбинации несколько разрядов отведены под служебную часть, характеризующую принадлежность символа к тому или иному регистру.

Информационная часть считанной иэ блока 5 памяти кодовой комбинации поступает на вход выходного регистра

9, а служебная часть — на входы блока 7 сравнения и регистра б признака. На другой вход блока 7 сравнения поступает с выхода регистра 6 признака служебная часть предыдущего перекодированного символа.

Если служебная часть считанной из блока 5 памяти кодовой комбинации не совпадает со служебной частью, хранящейся в регистре 6 признака, на выходе блока 7 сравнения формируется сигнал, который поступает на первый вход блока 8 управления и на адресный вход блока 5 памяти. При этом иэ блока 5 памяти считывается кодовая комбинация, соответствующая коду регистра перекодируемого символа, которая под управлением импульсов сдвига, формируемых на втором выходе блока 8 управления, записывается в выходной регистр 9 и выдается в линию связи через выход 12. По окончании выдачи кода регистра импульсом, формируемым на третьем выходе блока 8 управления, служебная часть кодовой комбинации переписывается в регистр б признака. При этом сигнал, сформированный блоком 7 сравнения и указывающий на несовпадение служебных частей предыдущей и перекодируемой кодовых комбинаций, снимается и иэ блока 5 памяти выбира ется кодовая комбинация в искомом алфавите, соответстьующая поступивrueA на вход 11 преобразователя кодовой комбинации. Отсчитав временной интервал„ соответствующий по длительности времени выдачи регистрового симьола, блок 8 управления формирует на втором выходе импульсы сдвига, под управлением которых информационная кодовая комбинация эаписыз 1 вается в выходной регистр 9 и выдается в линию связи с выхода 12. Если служебная часть считанной из блока

5 памяти кодовой комбинации совпадает со служебной частью предыдущего перекодированного символа, хранящейся в регистре 6 признака, то сигнал на выходе блока 7 сравнения не формируется и информационная часть выбранной кодовой комбинации под управлением импульсов сдвига, формируемых на втором выходе блока 8 управления, записывается в выходной регистр 9 и выдается в линию связи.

При преобразовании поступающей на вход кодовой комбинации в безрегистровый код кодовая комбинация в искомом алфавите, выбираем я из блока 5 памяти, не содержит служебной части, сигнал на выходе блока 7 сравнения не формируется и из блока 5 памяти выбираются только информационные коды. формула изобретения

1.Преобразователь кодов, содержащий первый регистр, выходы которого соединены с первыми входами умножителя, первый дешифрaòîð, выходы которого соединены с вторыми входами умножителя, второй дешифратор, входы которого объединены с входами первого дешифратора и являются управляющими входами преобразователя, блок памяти, первый выход которого соединен с первым входом второго регистра, выход которого соединен с первым входом блока сравнения, выход которого соединен с первым входом блока управления, вторые выходы блока памяти соединены с первыми входами третьего регистра, первый выход блока управления соединен с

363478 4 первым входом блока памяти, второй выход — с вторым входом третьего регистра, вход первого регистра является информационным входом преобра5 зователя, о т л и ч а ю щ и й, с я тем, что, с целью упрощения, первый выход умножителя соединен с вторым входом блока управления, третий выход которого соединен с вторым входом второго регистра, выход второго дешифратора соединен с вторым входом блока памяти, вторые выходы умножителя соединены с третьими входами блока памяти,-четвертый вход которого подключен к выходу блока сравнеиия, второй вход которого подключен к первому выходу блока памяти, выход третьего регистра является выходом преобразователя.

2. Преобразователь кодов по п.1, о т л и ч.а ю шийся тем, что блок управления содержит триггеры, элементы И, счетчик-делитель, инвер25 тор и генератор импульсов, выход которого соединен с первым входом .счетчика-делителя, первый выход которого соединен с первыми входами первого и второго элементов И и

30 первого триггера, выход которого соецинен с вторым входом счетчикаделителя, выход первого элемента И соединен с первым входом второго триггера, выход которого соединен с вторым входом первого триггера, выход инвертора соединен с вторым входом второго элемента И, второй вход первого элемента И объединен с входом инвертора и является первым

411 входом блока управления, второй вход второго триггера является вторым входом блока управления, выходы первого триггера, счетчика-делителя и второго элемента И являются соответственно первым, вторым и третьим выходами блока управления.

1363478

Составитель Б.Ходов

Редактор А.Огар Техред Л.Сердюкова Корректор И.Муска

Заказ 6380/54 Тираж 900 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, r.Óærîðoä, ул. Проектная,4