Устройство для синхронного радиоприема частотно- манипулированных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к радиосвязи и обеспе1«1вает прием многоуровневых сигналов. Для достижения цели введены последовательно соединенные эл-т .ИСКЛЮЧАЮЩЕЕ или 19 и односторонний частотный модулятор 20. В п.2 ф-лы дано устр-во модулятора 20. 1 3.п. ф-лы. 2 ил. 22. ро С5 СдЭ СП ГО Фиг,1

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51)4 Н 04 Ь 27/14

ОПИСЛНИК ИЗ0БРКтКНия

Н А ВТОРСИОМЪ(СВИДЕТЕЛЬСТВУ

1 ъ :

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (61) 1244804 (21) 4092644/24-09 (22) 07.05.86 (46). 30.12.87. Бюл. М - 48 (72) В.В.Дегтярев, С.M.Êàðòóøèí, Д.А.Судник, В.Ю.Лоскутов, А.С.Любимов, Б.Е.Сергеев и А.Е.Лисин (53) 621.394.62(088.8) (56) Авторское свидетельство СССР

Р 1244804, кл. Н 04 L 27/14, 1984.

„.80„„1363517 A 2 (54) УСТРОЙСТВО ДЛЯ СИНХРОННОГО РАДИОПРИЕМА ЧАСТОТНО-МАНИПУЛИРОВАННЬХ

СИГНАЛОВ (57) Изобретение относится к радиосвязи и обеспечивает прием многоуровневых сигналов. Для достижения цели введены последовательно соединенные эл-т ИСКЛЮЧАЮЩЕЕ ИЛИ 19 и односторонний частотный модулятор 20. В п.2 ф-лы дано устр-во модулятора 20.

1 13635

Изобретение относится к радиосвязи и может использоваться в станциях цифровой радиорелейной связи с частотной манипуляцией.

Цель изобретения — обеспечение

5 приема многоуровневых сигналов.

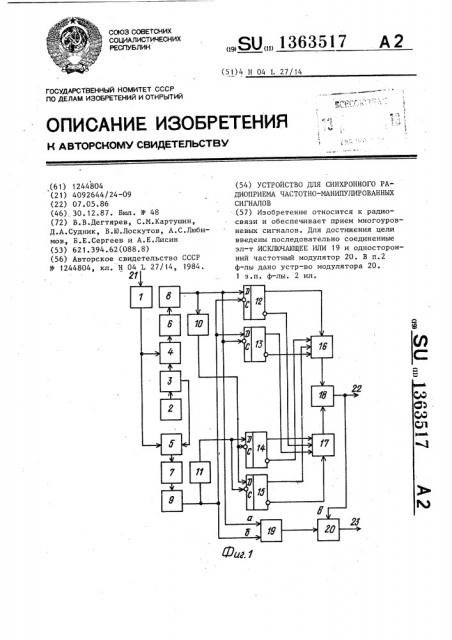

На фиг. 1 изображена структурная электрическая схема предложенного устройства; на фиг. 2 — структурная схема одностороннего частотного демодулятора.

Устройство содержит входной усилитель 1, синхронный гетеродин 2, квадратурный направленный ответвитель 3, первый 4 и второй 5 смесители, первый 6 и второй 7 фильтры нижних частот, первый 8 и второй 9 усилителиограничители, первый 10, второй 11 элементы НЕ, первый 12, второй 13, третий 14 и четвертый 15 триггеры, первый 16 и второй 17 сумматоры, компаратор 18, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ

19, односторонний частотный демодулятор 20, состоящий из генератора 21, элемента И 22, вычитающего счетчика 23, блока 24 дифференцирования по переднему фронту, блока 25 дифференцирования по заднему фронту, преобразователя 26 кода, буферного регист- ЗО ра 27, цифроаналогового преобразователя 28 и фильтра 29 нижних частот.

Устройство работает следующим образом.

Частотно-манипулированный сигнал поступает через входной усилйтель i одновременно на входы смесителей 4 и 5, на вторые входы которых через квадратурный направленный ответвитель

3 сигналы в квадратуре (со сдвигом о на 90 ) подаются от синхронного гетеродина 2. Частота синхронного гетеродина 2 устанавливается равной средней частоте спектра принимаемого сигнала (сигнала на входе устройства).

В результате преобразования на выхо45 дах. смесителей 4 и 5 образуются сигналы, поднесущие которых равны текущему значению частотного сдвига радиочастотной несущей от своего среднего значения, а взаимный сдвиг фаз

50 о равен 90 . При изменении знака модулирующего сигнала происходит взаимное инвертирование сигналов в квадратурных каналах при сохранении их квадратуры, т.е. взаимный фазовый

55 о сдвиг становится равным 270 . При изменении уровня сигнала на передаче изменяются значения частотного сдви17 2 га поднесущих. Фильтры 6 и 7 нижних частот обеспечивают частотную избирательность и формирование огибающих по квадратурным каналам. Аналоговые сигналы с фильтров 6 и 7 нижних частот усилителями-ограничителями 8 и 9 усиливаются и ограничиваются и таким образом преобразуются в цифровую (импульсную форму). Сигнал с выхода усилителя-ограничителя 8 поступает на информационный D-вход триггера 12, С вход синхронизации триггера 13, на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 19 и на вход элемента HE 10, который инвертирует сигнал по полярности. Сигнал с выхода элемента НЕ 10 подается на информационный D-вход триггера 15 и С-вход синхронизации триггера 14.

Сигнал с выхода -усилителя-ограничителя 9 поступает на информационный

D-вход триггера 13, С-вход синхронизации триггера 12, вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 19 и на элемент НЕ 11, который инвертирует сигнал по полярности. Сигнал с выхода элемента НЕ 11 подается на информационный D-вход триггера 14 и С-вход синхронизации триггера 15. На прямых выходах триггеров устанавливается сигнал, соответствующий по полярности сигналу на информационном D-входе в момент появления переднего фронта (или заднего в зависимости от типа микросхем) на

его С-входе синхронизации. Сигналы с прямых выходов триггеров 12, 15 и с инверсных выходов триггеров 13, 14 подаются на входы сумматора 16, который суммирует эти сигналы по напряжению. Сигналы с инверсных выходов триггеров 12, 15 и с прямых выходов триггеров 13, 14 подаются на входы сумматора 17. Сигналы с выходов сумматоров 16, 17 в противофазе подаются на входы компаратора 18, который преобразует ступенчатый сигнал с сумматоров в двоичный сигнал 41.

При поступлении на входы элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ 19 сигналов одинаковой полярности на выходе появляется сигнал "0", а при поступлении сигналов разной полярности — сигнал 1".

Длительность импульсов сигнала на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 19 обратно пропорциональна частотному сдвигу принима мого радиосигнала, а частота их следования в два раза выше частоты следования сигналов с усилителей-ограничителей 8 и 9. Сигнал з 13 с элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 19 подается на информационный вход односторон него частотного демодулятора 20, на управляющий вход которого подается сигнал с компаратора 18. Так как синхронный гетеродин 2 настраивается на среднюю частоту принимаемого сигнала, положительному и отрицательному значениям частотных сдвигов радиочастотной несущей соответствует одно значение частоты поднесущих в квадратурных каналах (этим объясняется смысл термина "односторонний", введенного в название частотного демодулятора).

Односторонний частотный демодулятор 20, используя удвоенное значение частотного сдвига по информационному входу и информацию о знаке, поступающую с выхода компаратора 18 на управляющий вход, формирует сигнал, который идентичен информационному сигналу.

Односторонний частотный демодулятор работает следующим образом. Сигнал с выхода элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ 19 подается параллельно на третий вход элемента И 22 и входы блоков 24, и 25 дифференцирования. На второй вход элемента И 22 с выхода переноса вычитающего счетчика 23 подается сигнал "1" ("0" подается только в случаях переполнения счетчика для блокировки), На первый вход элемента И 22 подается сигнал с генератора 21. Частота следования импульсов сигнала должна быть не менее удвоенного значения максимального частотного сдвига. В результате взаимодействия этих сигналов на выходе элемента И 22 появляется сигнал, в котором число импульсов в каждой пачке прямо пропорционально длительности импульсов сигнала с выхода элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ 19 и обратно пропорционально частотному сдвигу радиочастотной несущей. Блок 24 дифференцирования по переднему фронту выделяет передние фронты сигнала и образует на своем выходе сигнал, который подается на вход установки вычитающего счетчика 23 и устанавливает его в состояние, соответствующее "1" во всех разрядах, в начале каждой пачки импульсов сигнала с выхода элемента И 22.

Сигнал (каждая пачка) с выхода элемента И 22 подается на вычитающий вход вычитающего счетчика 23 и производит вычитание. Двоичное число, ко63517 торое устанавливается в вычитающем счетчике 23 по окончании вычитания, обратно пропорционально количеству

5 импульсов, поступивших на вычитающий вход вычитающего счетчика 23, т.е. прямо пропорционально частотному сдвигу. В случае достижения вычитающим счетчиком 23 состояния "0" по всем разрядам (переполнения) происходит блокировка его в этом состоянии до начала следующего информационного импульса. Блокировка осуществляс ется за счет поступления уровня "0 с выхода переноса вычитающего счетчика 23 на второй вход элемента И 22.

Двоичное число с вычитающего счетчика 23 поразрядно через преобразователь 26 кода подается на информационные входы буферного регистра 27. При наличии "1" на управляющем входе преобразователя 26 кода сигналы каждого разряда передаются без изменений, а при наличии "0" сигналы каждого разряда передаются с инверсией по символам, т.е. вместо "1" передается "0" и наоборот. Эти сигналы поразрядно .записываются в буферный регистр 27 каждым импульсом сигнала, который

Зп поступает с блока 25 дифференцирования по заднему фронту на вход записи буферного регистра 27. Эта информация хранится в памяти буферного регистра 27 в период времени между

35 импульсами сигнала с блока 25 дифференцирования и одновременно поразрядно подаются на входы цифроаналогового преобразователя 28. При этом на вход старшего разряда цифроаналогово4 го преобразователя 28 подается сигнал, который совместно с преобразователем кода 26 обеспечивает на своем выходе формирование двухполярного сигнала, т.е. формирование двухполярного сигнала обеспечивается за счет кодирования в преобразователе 26 кода и в цифроаналоговом преобразователе 28 и смещения подаваемого на опорный вход операционного усилителя циф50 роаналогового преобразователя 28.

Абсолютное значение сигнала на выход де цифроаналогового преобразователя

28 соответствует сигналам двоичного числа, которые поразрядно подаются на его входы, а полярность его опре55 деляется сигналом с преобразователя 26 кода. Фильтр 29 нижних частот уменьшает уровень шумов квантования на выходе устройства при приеме часСоставитель Н.Лазарева

Техред Й.Попович Корректор И.Муска

Редактор Т.Лазоренко

Заказ 6384/56 Тираж 636 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

5 136 тотио-модулированного сигнала. Точность восстановления принимаемого сигнала определяется разрядностью вычитающего счетчика 23, буферного регистра 27 и цифроаналогового преобразователя 28. Количество разрядов цифроаналогового преобразователя 28 .должно быть на один больше числа разрядов вычитающего счетчика 23. формула и з о б р е т е н и я

1. Устройство для синхронного радиоприема частотно-манипулированных сигналов по авт. св. N 1244804, о тл и ч а ю щ е е с я тем, что, с целью обеспечения приема многоуровневых сигналов, введены последовательно соединенные элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и односторонний частотный демодулятор, причем входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с выходами соответствующих усилителей-ограничителей, выход компаратора соединен с вторым входом одностороннего частотного демодулятора, выход которого является вторым выходом устройства.

2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что односто1

3517 6 ронний частотный демодулятор состоит из генератора, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом

5 переноса вычитающего счетчика, вход установки которого соединен с выхо- . дом блока дифференцирования по переднему фронту, вход которого соединен с входом блока дифференцирования по заднему фронту и третьим входом элемента И, выход вычитающего счетчика, выходы разрядов которого через последовательно соединейные преобразователь кода и буферный регистр соединены с входами цифроаналогового преобразователя, вход старшего разряда которого подключен к управляющему входу преобразователя кода, вход записи буферного регистра подключен к выходу блока дифференцирования по заднему фронту, выход цифроаналогового преобразователя соединен с входом фильтра нижних частот, выход которого

2б является выходом одностороннего частотного демодулятора, управляющий вход преобразователя кода является вторым входом одностороннего частотного демодулятора, а его первым вхо о дом является третий вход элемента И.