Устройство частотной демодуляции сигнала цветности секам

Иллюстрации

Показать всеРеферат

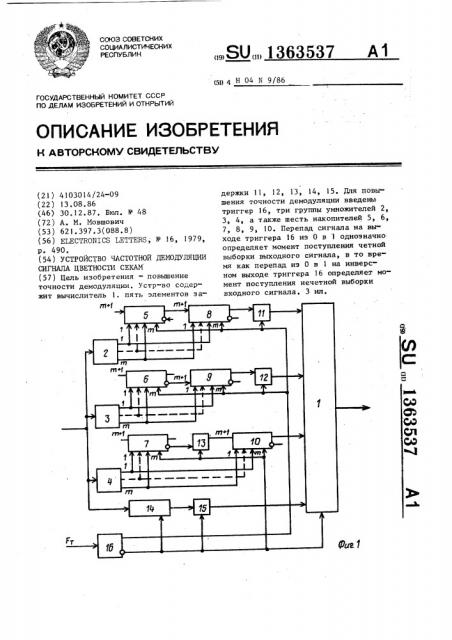

Цель изобретения - повьшение точности демодуляции. Устр-во содержит вычислитель 1. пять элементов задержки 11, 12, 13, 14, 15. Для повышения точности демодуляции введень триггер 16, три группы умножителей 2, 3, 4, а также тесть накопителей 5, 6, 7, 8, 9, 10. Перепад сигнала на выходе триггера 16 из О в 1 однозначно определяет момент поступления четной выборки выходного сигнала, в то время как перепад из О в 1 на инверсном выходе триггера 16 определяет момент поступления нечетной выборки входного сигнала. 3 ил. со О) со сд со

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ÄÄSUÄÄ 136353? А1

15И 4 Н 04 И 9/86

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АBTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4103014/24-09 (22) 13.08.86 (46) 30.12.87. Бюл. Р 48 (72) А. M. Мовшович (53) 621.397.3(088.8) (56) ELECTRONICS LETTERS, У 16, 1979, р. 490. (54) УСТРОЙСТВО ЧАСТОТНОЙ ДЕМОДУЛЯЦИИ

СИГНАЛА ЦВЕТНОСТИ CEKAM (57) Цель изобретения — повышение точности демодуляции. Устр-во содержит вычислитель 1. пять элементов задержки 11, 12, 13, 14, 15. Для повышения точности демодуляции введены триггер )6, три группы умножителей 2, 3, 4, а также шесть накопителей 5, 6, 7, 8, 9, 10. Перепад сигнала на выходе триггера 16 из 0 в 1 однозначно определяет момент поступления четной выборки выходного сигнала, в то время как перепад из О в 1 на инверсном выходе триггера 16 определяет момент поступления нечетной выборки входного сигнала. 3 ил.

1363537

Изобретение относится к технике телевидения и может быть использовано для демодуляции сигналов цветности в системах СЕКАМ.

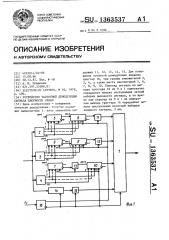

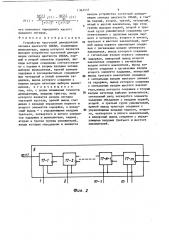

Цель изобретения - повышение точности демодуляции, На фиг. 1 представлена электрическая схема устройства частотной демодуляции сигнала цветности СЕКАМ; на фиг. 2 - схема накопителя; на фиг. 3 - схема группы умножителей.

Устройство частотной демодуляции сигнала цветности СЕКАМ (фиг. 1) содержит вычислитель 1, первую 2, вто.рую 3 и третью 4 группы умножителей, первый 5, второй 6, третий 7, четвертый 8, пятый 9 и шестой 1О накопители, первый 11, второй 12 третий 13, четвертый 14 и пятый 15 элементы задержки, триггер 16.

Накопитель (фиг. 2) содержит сумматоры (17-1)-(17-т) с памятью.

Группа умножителей (фиг. 3) содержит умножнтели (18-1)-(18-ш).

Устройство частотной демодуляции сигнала цветности СЕКАМ работает следующим образом.

На вход устройства частотной демодуляции сигнала цветности СЕКАМ поступают выборки частотно-модулированного сигнала цветности. Момент поступления очередной выборки жестко связан с моментом поступления сигнала тактовой частоты на вход триггера

16. Таким образом, перепад сигнала на выходе триггера 16 из 0 в 1 однозначно определяет момент поступления четной выборки выходного сигнала, в то время как перепад из 0 в на инверсном выходе триггера определяет момент поступления нечетной выборки входного сигнала.

В моменты положительного перепада (иэ 0 в 1) на управляющих входах соответствующих первого 11, второго 12, третьего 13, четвертого 14 и пятого

15 элементов задержки и первого 5, второго 6, третьего 7, четвертого 8, пятого 9 и шестого 10 накопителей формируются сигналы, которые преобразуются во входные сигналы вычислителя 1 и которые на момент С = nT где

n — - номер отсчета входного сигнала;

Т - период сигнала тактовой частоты, могут быть представлены в виде Е) Р Ы(Т)

Т d

x(nT), где y(t), x(t) — комплексно-сопряженные составляющие входного сигнала.

Эти сигналы реализуются в соответствии с выражениями, задающими связь выборок входного сигнала x(t) с ком10 плексно-сопряженным с ним сигналом у(t) и производными обоих сигналов и

dt dt

1р dy(t) x((n-(2K-1) )Т3

Тя-о () x ((n-(2K-l ) )>l

20 - 2K-1 ?кi /

K c ffl t Т

dx(t ) — х t,(n-2К) Т) dt /t=n T — 2К кфО

Требуемые коэффициенты для вычисяення рядов ы-,, RK- —, 2К-1) 2К-1 2К

30 задаются умножителями (18-1)-(18-тп) в первой 2, второй 3 и третьей 4 группах умножителей соответственно, а значения рядов вычисляются на выходах первого 11 и второго 12 элементов задержки, шестого накопителя IO и пятого элемента задержки 15. Второй, третий, четвертый и пятый элементы задержки служат для согласования временных задержек обработки

40 сигналов при вычислении сигналов

y(t), и, на выходах а (t) dx(t) первого 11 и второго 12 элементов формируются сигналы, соответствую45 щие четным выборкам входного сигнала, а на выходах шестого накопителя 10 и пятого элемента задержки 15 - соответствующие нечетным выборкам входного сигнала. Дпя осуществления их

50 временного согласования производят временное тактирование вычислителя

1 сигналом, поступающим на его управляющий вход, разрешая прохождение

55 на его выход сигналов лишь синхронI ных с нечетными выборками входного сигнала. Выходной сигнал в вычислителе 1 формируется в соответствии с выражением

1 363537 что позволяет определить частоту входного сигнала.

Формула и з обретения

Устройство частотной демодуляции 30 сигнала цветности СЕКЛИ, содержащее вычислитель, выход которого является выходом устройства частотной демодуляции сигнала цветности СЕКЛИ, первый и второй элементы задержки, вы- 15 ходы которых соединены соответственно с первым и вторым входами четных выборок вычислителя, третий элемент задержки и последовательно соединенные четвертый и пятый элементы за- 20 держки, выход которого соединен с первым входом нечетных выборок вычислителя, о т л и ч а ю щ е е с я тем, что, с целью повышения точности демодуляции, введены триггер, вход которого является входом сигнала тактовой частоты, прямой выход соединен с входами управления первого и второго элементов задержки, а инверсный выход - с управляющими входами 30 третьего, четвертого и пятого элементов задержки и вычислителя, первая, вторая и третья группы умножителей, входы которых объединены и являются входом устройства частотной демодуляции сигнала цветности СЕКЛИ, а так- же первый, второй, третий, четвертый,, пятый и шестой накопители, при этом группы .выходов первой, второй и третьей групп умножителей соединены соответственно с группами входов первого и четвертого, второго и пятого третьего и шестого накопителей, прямой выход первого накопителя соединен с сигнальным входом четвертого накопителя, выход которого соединен с сигнальньи входом первого элемента задержки, инверсный выход второго накопителя соединен с сигнальным входом пятого накопителя, выход которого соединен с сигнальным входом второго элемента задержки, инверсный выход третьего накопителя соединен с сигнальным входом третьего элемента задержки, выход которого соединен с сигнальным входом шестого накопителя,выход которого соединен с вторьи входом нечетных выборок вычислителя, сигнальный вход четвертого элемента задержки объединен с входами первой, второй, и третьей групп умножителей, прямой выход триггера соединен с управлякщими входами первого, второ-го четвертого и пятого накопителей, а инверсный выход соединен с управляющими входами третьего и шестого накопителей.

1363537

5U9 3

Составитель Э. Борисов редактор И. Киштулинец Техред М.ходанич Корректор С. Шекмар

Заказ 6383/57

Тираж 636 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

)13035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4