Устройство для контроля блоков управления

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и позволяет расширить область применения устройств для контроля блоков управления (БУ) за счет обеспечения возможности контроля параллельных БУ и увеличения контролирующей способности. Устройство для контроля БУ содержит регистры 1 и 2, группы элементов И 4,8 и 10, ИЛИ 7 и НЕ 9, элемент ИСКЛЮ- ЧАКМЦЕЕ ИЛИ 13, блок коммутации 14, триггеры результата контроля 6 и 11, группу триггеров 3, элементы ИЛИ 5 и 12. Устройство осуществляет контроль соответствия сигналов, параллельно поступающих от БУ, допустимому множеству сигналов, набору логических условий и требуемому порядку следования . Каждая ячейка устройства,включающая триггер группы триггеров, элементы И, ИЛИ, НЕ, при поступлении соответствующего контролируемого сигнала вырабатывает в зависимости от состояния подмножества триггеров и текущих значений логических условий сигнал подтверждения либо сигнал ошибки. Наличие таких сигналов в ячейках устройства фиксируется триггерами рес сл зультата контроля. 1 з.п. ф-лы, 8 ил. 5

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1365086 А1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4085607/24-24 (22) 09.07.86 (46) 07.01.88. Бюл. 11 1 (71) Ленинградский электротехнический институт им. В.И. Ульянова (Ленина) (72) В.H. Балакин, В.В. Барашенков, А.Ф. Казак и С.А. Никищенков (53) 681.3(088.8) (5e) Авторское свидетельство СССР

1187167, кл. С 06 Е 11/00, 1984.

Авторское свидетельство СССР

М 1128258, кл. Г 06 F 11/00, 1983. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ

УПРАВЛЕНИЯ (57) Изобретение относится к автоматике и вычислительной технике и позволяет расширить область применения устройств для контроля блоков управления (БУ) за счет обеспечения возможности контроля параллельных БУ и увеличения контролирующей способности.

_#_

Устройство для контроля БУ содержит регистры 1 и 2, группы элементов И

4,8 и 10, ИЛИ 7 и НЕ 9, элемент ИСКЛЮЧАЮ111ЕЕ ИЛИ 13, блок коммутации 14, триггеры результата контроля 6 и 11, группу триггеров 3, элементы ИЛИ 5 и

12. Устройство осуществляет контроль соответствия сигналов, параллельно поступающих от БУ, допустимому множеству сигналов, набору логических условий и требуемому порядку следования. Каждая ячейка устройства,включающая триггер группы триггеров, элементы И, ИЛИ, НЕ, при поступлении соответствующего контролируемого сигнала вырабатывает в зависимости от состояния подмножества триггеров и текущих значений логических условий сигнал подтверждения либо сигнал ошибки.

Наличие таких сигналов в ячейках устройства фиксируется триггерами результата контроля. 1 з.п. ф-лы, 8 ил.

1365086

Изобретение относится к вычислительной технике и предназначено для использования в системах контроля правильности функционирования блоков управления Параллельных 3ВМ.

Целью изобретения является расширение области применения за счет обеспечения возможности контроля блоков управления, реализующих алгоритмы с различной степенью параллелизма, и расширение класса обнаруживаемых дефектов °

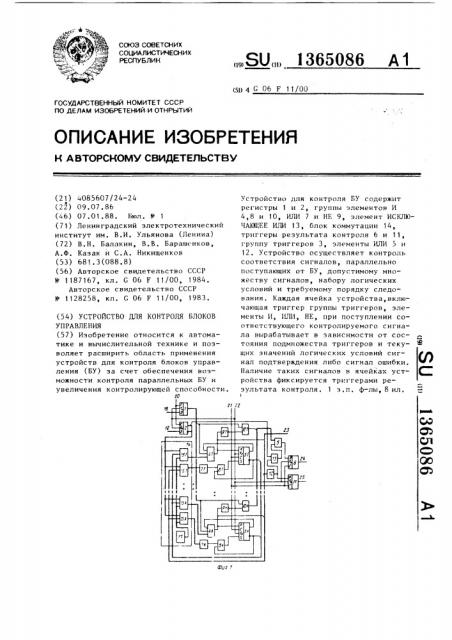

На фиг. 1 представлена схема устройства; на .фиг. 2 — микропрограмма 15 работы ячейки; на фиг. 3 — пример контроля параллельного алгоритма управления по заданной операторной схеме; на фиг. 4 — вариант выполнения блока коммутации; на фиг, 5 — пример 20 контроля блока управления по заданной информационно-логической схеме алгоритма; на фиг, 6 — пример контроля

1 конвейерного управления; на фиг. 7 схемы управляемых коммутаторов; на фиг. 8 — пример настройки управляемых коммутаторов.

Предлагаемое устройство содержит первый регистр 1, второй регистр 2, группу триггеров 3.1-3.k, первую 30 группу элементов И 4. 1-4.k, первый элемент ИЛИ 5, первый триггер результата контроля 6, группу элементов ИЛИ

7. 1-7.k вторую группу элементов

И 8.1-8.k, группу элементов НЕ 9. 19.k третью группу элементов И 10.110.k второй триггер результата контроля 11, второй элемент ИЛИ 12, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 13, блок 14 коммутации, содержащий первую группу уп- 40 равляемых коммутаторов 15 ° 1 — 15.k втовторую группу управляемых коммутаторов 16.1-16.k и регистр 17 настройки, вход 18 контролируемых сигналов, вход

19 логических условий, первый вход 20 45 синхронизации, второй вход 21 синхронизации, вход 22 сброса устройства, выходы информации о результате контроля, ошибки и подтверждения соответственно 23, 24 и 25 устройства.

Схема варианта выполнения блока коммутации (фиг. 4) содержит шину 26 единичного потенциала, шину 27 управления, первую и вторую информационные входные шины 28 и 29, выходные информационные шины 30-51, элементы

И 52-55.

Управляемый коммутатор первой группы 15,i (фиг. 7а) содержит первую группу элементов ИЛИ 56.1-56.1, вторую группу элементов ИЛИ 57.1-57.п, последнюю группу элементов ИЛИ 58,158.п группу элементов И-НЕ 59.1-59.1 входную информационную шину 60, выходную шину 61 и входные шины управления 62 и настройки 63.

Управляемый коммутатор второй группы 16.i (фиг. 7б) содержит вторую группу элементов И 64.1-64.m первую группу элементов ИЛИ 65. 1-65.п последнюю группу элементов ИЛИ 66.166.п, первую группу элементов И 67.167.m входную информационную шину 68, выходную шину 69 и входные шины управления 70 и настройки 71.

Назначение основных узлов устройства следующее.

Регистр 1 служит для приема и хранения поступающих от контролируемого блока управления значений признаков инициации команд — контролируемых ь и д и сигналов — вектора а = а ... а"...а

4 где а . = 1 (i-я команда инициироваt на) или О, причем выход i-ro разряда регистра 1 подключен к первому входу элемента И 4.i. Ðåãèñòð 2 предназначен для приема и хранения поступающих от объекта управления (например, процессоров 3BM) значений условий протекания процесса вычисления — векФ тора P = P,...P ...Р, rpe Р = 1 или О. а также для управления блоком коммутации 14 и элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 13.

Триггеры 3.1-3,k служат для отображения процесса поступления контролируемых сигналов от блока управления (хранения "истории" управления), являясь внутренней памятью устройства вектором состояния С = С,... С,...С, 1 где С вЂ” состояние триггера З.i.

Элементы И 4.1-4.k предназначенные для проверки условия возможности инициирования команд: формирования сигналов подтверждения правильности инициирования команд — вектора а " = а",, и и л ...а ...а „на выходе 23, где а, = 1 или О соответственно при подтверждении и неподтверждении, и перевода при этом триггеров 3.1-3.k в новые состояния.

Элемент ИЛИ 5, триггер 6, элементы

ИЛИ 12 и ИСКЛЮЧАЮЩЕЕ ИЛИ 13 служат для формирования на выходе 24 сигнала ошибки при наличии дефекта в управлении процессом вычисления.

1365086 а". = 1, С = О, (1) а;Cf,=1 условие формирования сигнала ошибки: а. (C;v f )=a.(C f,) = 1 => d; = 1,(2) условие перевода в состояние "1" ячейки:

55 (3) е С; сфорС;Е,=1=)С;=1 причем анализируемое значени мировано в предыдущем такте.

Триггер 11 служит для формирования на выходе 25 сигнала наличия хотя бы одной подтвержденной команды.

Элементы ИЛИ 7.1-7.k и элементы

И 8.1-8.k предназначены для перевода триггеров 3.1-3.k иэ состояния "О" в состояние "1" в процессе работы устройства.

Элементы НЕ 9.1-9.k и элементы 1п

И 10.1-10.k служат для формирования вектора сигналов ошибки о = с1, °,,с1 ... ...д при инициации соответствующих команд и невыполнении условий возможности инициации, т.е. при дефекте в 15 потоке управления.

Блок 14 коммутации предназначен для условно зависимой (от вектора Р) коммутации инверсных выходов триггеров 3,1-3.k (элементов множества 2р

«С; ) и выходов элементов И 4.1-4.1 (элементов множества (а; ) соответстл ° венно на входы элементов И 4.1-4.k и элементов ИЛИ 7.1-7.k обеспечивая взаимодействие ячеек устройства ° 25

Устройство функционирует следующим образом.

Блоки 3.1, 4.i, 7.i 8.i 9.i u

10.i образуют i-ю ячейку устройства, функционирующую согласно фиг. 2, где ЭО

С вЂ” состояние триггера З.i; а —

1 состояние i-ro разряда регистра 1; а ", — состояние выхода элемента И 4.i;

d — состояние выхода элемента И

10.i f — конъюнкция сигналов на группе входов элемента И 4.i подключенных к блоку 14, называемая функци Н ей возможности; f . .— дизъюнкция сигналов на входах элемента HJIH 7.i называемая функцией готовности, при- 4О чем f, = f, ((C; I,(P>.) и f ", =f ";(a"; }, (P<)), что задается реализацией и или настройкой блока 14 коммутации.

Таким образом, условие возможности инициации и подтверждения правильнос- 45 ти для i-й команды имеет вид:

После включения устройства в работу на вход 22 подается сигнал сброса в исходное, переводящий триггеры 3.1—

З.k-1, триггеры 6 и 11 и регистры 1 и 2 в нулевое, а триггер З.k, соответствующий команде "Начало" — в единичное состояние.

Очередной запуск устройства осуществляется при выработке блоком управления очередной группы команд и поступлении на вход 18 устройства их признаков, при этом в регистры 1 и 2 по импульсу на входе 20 (т.е. в первом микротакте) записываются текущие

B e K T о р bt B 4

Те ячейки, для которых выполняются условия (1) или (2), формируют сигналы подтверждения или ошибки. 3атем на входе 21 формируется импульс синхронизации (второй микротакт), при этом те ячейки, для которых выполняются условия (1) или (3), переходят в новые состояния, а триггеры

6 и 11 формируют соответственно на выходах 24 и 25 сигнал ошибки:

k

D = (Ud) 3 ((U а".)ООP )

ic1 1 (4) и сигнал подтверждения:

II=V а", (5) единичные значения которых говорят соответственно о наличии дефекта в блоке управления и наличии хотя бы одной подтвержденной команды, причем

P, — условие нахождения блока управления в состоянии прерывания/останова (P, = О) или работы (P, = 1), значение которого поступает на второй вход элемента ИСКЛЮЧАЮЦЕЕ ИЛИ 13.

В основе функционирования устройства лежит принцип алгоритмического контроля — отслеживания соответствия потока команд на выходе контролируемого блока управления заданной структуре алгоритма вычислений. Алгоритм характеризуется множеством участвующих команд и отношениями порядка между ними и описывается схемой, определенной на множестве операторов 1а-1 (преобразователей, т.е. команд обработки данных, и распознавателей,т.е. команд передачи управления), среди которых выделен начальный и конечный операторы. В операторных схемах алгоритмов (схемах с заданным управлением, например, изображенных на

1365086 фиг. За) оператору а предписывает1 ся выполнение после выполнения неко40 такта от сигналов подтверждения других торого множества предшественников и при соответствующем значении логи5 ческих условий. В информационно — логических схемах алгоритмов (схемах вычислений или схемах без заданного управления, например, изображенных на фиг. 5б) указывается, что а. мо- 10 жет потенциально выполняться после выполнения соответствующих предшественников (информационных и логических) и условий. В общем случае команда с меткой.а; (оператор а;) может быть инициирована, если выполнены все команды, являющиеся ее предшественниками в информационном, логическом и конкуренционном смысле, и имеют соответствующие значения условия протека- 20 ния процесса вычислений.

При выработке блоком управления потока команд возможны следующие типы дефектов:

1) инициированная команда не входит 25 в множество команд, использующихся в данном алгоритме вычислений;

2) инициированная команда нарушает требуемый порядок следования команд при данном вычислении; 30

3) в отсутствие прерывания/останова не вырабатывается ни одна команда ("зависание управления);

4) при прерывании/останове продолжается инициация команд;

5) многократное ложное инициирование команды (залипание ).

Устройство обладает возможностью выявления дефектов всех перечисленных типов, Дефекты типа 1 выявляются путем \ задания f = 0 (реализацией или настройкой блока 14 коммутации для ячеек, соответствующих командам, не участвующим в данном алгоритме. Тем самым обеспечивается невозможность их перевода в состояние готовности при контроле алгоритма.

Дефекты типа 3 и 4 выявляются в соответствии с выражениями (4) и (5) блоками 5, 12 и 13.

Дефекты типа 5 обнаруживаются вследствие такой органиэации функционирования ячеек, что после подтверждения команды она обязательно переходит из состояния "1" в состояние "0" и может перейти в состояние "1" только во втором микротакте следующего команд. При этом для кратного выполнения команд осуществляют присвоение им отличающихся меток в соответствии со схемой алгоритма либо, по возможности, организуют цикл со счетом повI торений.

Для выявления дефектов типа 2 по заданной схеме алгоритма для каждого оператора схемы определяют функции

М 1 и f; указывающие, при каких условиях д-я ячейка устанавливается в "1" и после каких условий она может подтвердить правильность инициации команды и перейти в "0".

Устройство реализует проверку спусковых функций для каждой команды,причем в отличие от известного применения спусковых функций и асин онных схем программ, осуществляется их использование в целях контроля. В устройстве проверка спусковых функций реализуется (интерпретируется) элементами 4.1-4.k состояние управляющих переменных — триггерами 3.1-3.k, установка управляющих переменных в соответствующие состояния — сигналаП ми а; в зависимости от предыдущих состояний триггеров, сигналов а. и заданных коммутатором связей между ячейками.

Длительность первого микротакта выбирается из условия окончания переходных процессов в логических схемах устройства и составляет величину, соизмеримую с задержкой в регистре памяти. Следующий запуск устройства импульсом на входе 20 может осуществиться практически сразу после подачи импульса на входе 21, т.е. перекрывать второй микротакт, При использовании устройства для контроля программных блоков управления, выполнение команд которых в процессорах ЭВМ требует времени, значительно превышающего задержку в элементах памяти, можно считать, что проверка правильности управления осуществляется практически мгновенно, а команды могут быть инициированы в произвольный момент времени. т.е. асинхронно, но с интервалом, не меньшим времени такта устройства.

На фиг. За,б,в,г показаны соответственно контролируемая схема алгоритма (а, — а „ — метки команд), таблица настройки (функций блока 14 коммутации): иллюстрация настройки (номера вершин графа соответствуют меткам, 1365086

8 толстые сплошные линии показывают, что для подтверждения команды,соответствующей ячейке, в которую входит дуга, необходимо, чтобы С; = 1 цля -й ячейки, откуда дуга исходит,тонкие сплошные (штриховые) линии от вершины 1 вершине показывают, что 1-я ячейка устанавливается безусловно (условно) от сигнала а ), и таблица !ð функционирования (t — номер такта; х — произвольное значение логического условия; t = 4, 5, 6 — другое продолжение процесса после такта 3).

Последняя иллюстрирует работу устрой- 1r ства при контроле блока управления, реализующего данный алгоритм и форми— ! рующе го поток а, сопровождаемый сбоями, причем элементы векторов получаются в соответствии с микропро- 2р граммой на фиг. 2. Например, оператор а может выполниться после а, и после а (при Р, = 1), оператор а — после а"„ (при P> = 1), и т.п. оператор а может выполниться, если 25 ячейка 8 переведена в "1" сигналом а (при P, = О), переведены в О" ячейки 5 и 10, установленные в "1" сигналом а „, переведена в О" та из ячеек 6 и 7, которая была уста- 30 новлена в "1" сигналом а" при соот1О ветствующем Р .

При настройке по параллельной схеме алгоритма (а также по информационно-логической) в некоторый момент времени условие (1) может быть выполнено не для всех команд, у которых единичны функции возможности и единичны состояния ячеек. Иначе говоря, управление будет беэдефектным (в смыс-4О ле дефектов типа 2), если иэ множества команд, которые могут быть инициированы (выполнены все соответствующие условия), блоком управления вырабатываются лишь некоторые, например 4> после подтверждения команды а (фиг.3) .

Сказанное справедливо для любого момента времени, причем порядок инициации команд из указанного множества может быть произвольным. Отсюда следует, что для заданной настройки существует множество функционально-эквивалентных (дающих одинаковый результат для одинаковых данных) алгоритмов управления, различающихся (в соответ- ствующих пределах) степенью параллелизма и порядком следования операторов, но контролируемых предлагаемым устройством с той же эффективностью (охватом типов дефектов) беэ перенастройки его. Например, для фиг. 3 это следующие (по номерам команд, в скобках — параллельно выполняемые):

k, (2,3,4), (9,5,10), (2,6), 9,8..; дого из алгоритмов данного множества инициация ложной команды по условию (2) приведет к сигналу ошибки на выходе 24. Настроенное на контроль параллельной схемы алгоритма предлагаемое устройство обладает расширенными функциональными воэможностями, Вариант выполнения блока 14 коммутации для контроля согласно фиг. 3 представлен на фиг. 4.

Наибольший эффект от использования устройства достигается при настройке по информационно-логической схеме алгоритма (ИЛСА), отличающейся от операторных схем тем, что в ней указываются только отношения информационного и логического следования между операторами. В этом случае настройка коммутатора, т.е. получение функций возможности и готовности, осуществляется по ИЛСА.

Стандартной схеме программы на фиг.5а соответствует ИЛСА на фиг.5б, где тонкие сплошные дуги означают отношения безусловного информационного следования, штриховые — условного информационного следования, толстые отношения логического cs:åäîâàíèÿ.Ïo

ИЛСА оператор аз может выполниться после а, (вход в цикл) и после выполнения а и а в цикле, и т.п, Иллюстрация настройки (аналогично фиг.3в) и таблица настройки показаны на фиг.5в,г, таблица функционирования на фиг. 5е причем из ИЛСА исключены избыточные связи (например, так как а следует за а, à а — эа а, то связь а, а, не учитывается). Устройство контролирует множество эквивалентных алгоритмов, имеющих данную

ИЛСА ("вычисляющих" ИЛСА): k, 1,2,3, (4,5),. ° .,6; k, (1,2),3,4,5,3, (4,5),...

6; 1с, 2,1,3,5, 4,3 (4,5), 3,6 и т.д.

Поскольку ИЛСА служит основой для распараллеливания алгоритмов и позволяет получить максимально распараллеленные алгоритмы, то устройство обладает способностью контролирования класса эквивалентных алгоритмов — от последовательных до максимально па1365086

10 раллельных, что существенно расширяет область применения.

Устройство обладает расширенными функциональными возможностями при та5 кой же эффективности и может быть использовано для контроля алгоритмов управления с произвольной степенью параллелизма, в том числе с динамическим распараллеливанием, когда опе- Ip раторы назначаются на исполнение асинхронно в произвольном порядке.

При контроле конвейерного управления (например, по схеме программы на фиг. 6а) устройство может иметь два варианта настройки в зависимости от того, контролируется асинхронный конвейер с переменным конвейеризмом (перекрытием следующих выполнений алгоритма), как показано на фиг. Ьб,. в,г ° или синхронный конвейер с постоянным конвейеризмом, фиг. 6в,е,ж.

При контроле синхронного конвейера устройство прекращает подтверждение правильности инициации команд незави- 25 симо от контролируемого потока управления (останавливает конвейер),если в потоке команд возник дефект типа пропадание" — инициированы не все команды в группе синхронных команд (такты 5,6 и 6,7) т.е. обладает повышенной контролирующей способностью.

При настройке по ИЛСА (параллельной схеме алгоритма) устройство хранит" информационно-логическую струк35 туру вычисления, а не структуру ал,горитма управления, но вместе с тем выявляет дефекты типов 1-5 для целого класса алгоритмов управления с разной степенью параллелизма, а при

40 дублировании для каждого из указанных алгоритмов следует задавать соот1 ветствующий дублирующий автомат.

Устройство позволяет контролировать блоки, управляющие вычислениями с ап- „ риори неизвестным (динамическим) распараллеливанием программ и алгоритмов, при этом самопроверяемое дублирование не применимо.

Устройство позволяет контролировать практически любой параллельный блок управления при едином способе настройки.

Если устройство осуществляет контроль многопрограммных блоков управления с фиксированным набором программ, то аналогично методике объединения операторных схем алгоритмов осуществляется объединение схем алгоритмов (параллельных, ИЛСА) с помощью введения в множество IP I дополнительных логических условий выполнения того или иного алгоритма, составления матричных схем и исключения избыточных членов, при этом может учитываться синтаксическое. и семантическое совпадение операторов. Блок 14 коммутации выполняется по объединенной схеме. В частности, при объединении двух

HJICA с непересекающимися множествами операторов все связи между ячейками будут зависеть от значения дополнительного условия.

При контроле многопрограммных блоков управления устройство выявляет дефекты системного уровня — ошибочные переходы к выполнению другого алгоритма, поскольку такие дефекты адекватны дефектам типа 1 и 2.

Для контроля блоков управления с изменяемым набором алгоритмов блок

14 коммутации выполняется в виде управляемого коммутатора.

Коммутатор 15.i формирует на 1 -м выходе шины 61 (= 1,2,...,1,1 < 1с) функцию

С v (h ((Р y r; ) I (Р v г, ) ) ), где С вЂ” состояние 1 -ro входа данных

1 шины 60; q — число условий (разрядов

I регистра 2); г; „, и г; „— элементы

I вектора настройки R, задающего код

,11 на вторых входах элементов ИЛИ группы элементов ИЛИ коммутатора 15.i,âûõîäû которых подключены ко входам элемента

И-НЕ 59. 1, причем для Ы-го разряда регистра 2 определена одна и только одна пара элементов в указанной группе элементов ИЛИ, такая, что первые входы элементов пары соединены соответственно с прямым и инверсным выходом Ы -го разряда регистра 2, а на вторые входы поступают соответственно маски r;<

Л

1 и в зависимости от настройки R; у 1 t ...,г,„„,функция Г может не зависеть, ( завИсеть беэусловно или условно (от набора условий) от значений выбранного множества 1С >I. Если С входит в

I беэусловно, то R; z содержит все 1.

Если С не входит в f то достаточно

1365086

12 для любой пары масок задать r, 1,I! г,,„= О (считается, что Г.; = 0) .

ti

I !

Если С входит в f при заданном значении условий из )Pz), то в векторе

Б

R. задаются нулевыми маски соответст1 1 нующие заданным значениям условий. На фиг. 8 дан пример настройки коммутаторов для контроля заданного алгоритма по таблице настройки на фиг. 5д) при выполнении коммутаторов 15.i u

16.i полными, т.е. 1 = k, m = k u

n = 2q. В таблице векторов настройки для каждого вектора R,. указываются составляющие его вектора R;, не рав- 15 ные О, а в скобках — составляющие элементы вектора R;qj равные 0.3am!Cb

R < = R; R <,(г ) означает, что для

I обеспечения в шестой ячейке ь

С (С P ) необходимо задать равным 20

1 вектор R, маскирующий группу элементов ИЛИ, подключенных выходами к элементу И-НЕ, коммутирующему С, в векторе R задать все единицы, кроме маски r (индексы i, опущены), пос- 2Б тупающей на второй вход элемента ИЛИ, первый вход которого соединен с прямым выходом разряда регистра 2, соответствующего (хранящего) значению P остальные векторы нулевые.

Коммутатор 16.i формирует íà d -м выходе шины 69 (d = 11,,22,...,m; ш c k) функцию

f, ð=à л(ч ((Р UU, ð,() л(Р чU.,!))), а где а — состояние d -го входа шины ь

68; U è U;g - элементы вектора настройки U;, задающего код на вторых 40 входах элементов ИЛИ группы элементов

ИЛИ коммутатора 16 ° i, выходы которых подключены Ко входам элемента И 67. d

Настройка коммутатора 16.i осуществляется аналогично настройке коммута- 45 тора 15.i (фиг. 8), при этом

fI„,. 1

При выполнении блока 14 коммутации в виде управляемого коммутатора во время функционирования устройства векторы R u U хранятся в регистре

17. При смене набора программ, выполняемых блоком управления, в регистр .

17 заносятся новые значения векторов настройки, настраивая блок 14 коммутации и устройство на контроль нового набора программ.

Использование полного коммутатора (1 = т = 1с, п = 2q) целесообразно при контроле набора сильносвязанных алгоритмов, когда выполнение каждого оператора может зависеть от множества предшественников и условий, которые на практике задаются, как правило, управлением неполной коммутацией (например, 1 = m = n = 4), что существенно снижает избыточность.

Следует отметить, что переход от схемйой коммутации в устройстве к настройке от регистра 17 аналогичен переходу от схем с жесткой логикой к микропрограммному управлению.Предлагаемое устройство выгодно отличается технологичностью выполнения, так как оно обладает регулярностью структуры (отнотипные ячейки и коммутаторы), что позволяет его реализовать в виде

БИС однородного специализированного процессора. Управляемые коммутаторы могут быть выполнены на ПЛМ, а устройство в целом — на основе базовых кристаллов. Другим вариантом является выполнение на матрицах нескоммутируемых элементов, при этом реализация блока 14 коммутации осуществляется по заданному набору контролируемых алгоритмов.

Наиболее оптимальным применением и реализацией предлагаемого изобретения является использование устройства для контроля ° параллельных блоков управления специализированных ЭВМ с фиксированным набором алгоритмов вычислений и переменной (динамической) степенью распараллеливания программ, причем устройство выполняется в виде

БИС, программируемой (настраиваемой в условия производства по заказу.

Устройство обладает повьппенной контролирующей способностью, так как позволяет контролировать поток выходных сигналов блока управления по условию его соответствия свободным ресурсам объекта управления ° Для этого в множество (P ) условий протекания процесса вычислений вводятся условия свободности (занятости) ресурсов, например, процессоров, которые входят в функции возможности соответствующих ячеек устройства.

Пусть для ИЛСА на фиг. 5б задано следующее распределение ресурсов по операторам: операторы а, и à z — ресурс 1 (например, устройство вводавывода), а; и а — ресурс 2, аз и а

14

1365086

13 ресурс 3. Состоянию свабодности (занятости) ресурсов 1, 2 и 3 соответствуют единичные значения (нулевые) условий P» P> и P, . Таблицы настрой5 ки коммутатора, функционирования устройства и векторов настройки комму-! та1 ора даны соотнетственно на фиг.5д и фиг. 8, причем ячейка 7 используется н качестве служебной (при функциа- lp нировании С, = 1) для получения коньюнкции, не реализуемой непосредственно коммутаторами 15.1 — 15.i. Например, в такте 2 фиг.5ж инициация а при1 г знается неправильной, поскольку 15

Р = О, и т и.

При функционировании н составе системы, включающей блок управления, объект управления и предлагаемое уст- 2р ройство, оно подключается входом 18 к выходу признаков инициации команд блока управления, входом 19 — к выходу логических условий объекта управления (т.е. соединяется со входом ло- 25 гических условий блока управления), входами 10, 21 и 22 — соответственно к выходам узла синхронизации и сброса системы, выходами 24 и 25 — соответственно к входу устройства прерывания системы и входу устройства индикации режима работы системы, а выход 23 мажет использоваться либо для фиксации правильных команд в потоке управления, либо (при полном контроле по схеме алгоритма) непосредственно для управления объектом управления, который при этом должен включать регистр для приема вектора а", синхронизируемый импульсами на входе 21. Поток векторов а " на выходе 23 устройства (фиг. 3,5-7 — таблицы функционирования) получается в результате декомпозиции потока контролируемых сигналов на правильные (подтвержденные) и ошибочные. Иначе говоря, предлагаемое устройство корректирует входной поток сигналов, сопровождаемый обоями. При этом вероятность ньдачи ложных сигналов на выходе 23 мала, поскольку надежность функционирования устройства при выполнении в виде БИС существенно выше надежности программных блоков управления, включающих

ОЗУ, дешифраторы, регистры и т.п; кроме тога, для ньдачи ложных сигналов на выходе 23 необходимо, чтобы сбой (отказ) произошел и в блоке управления, и в предлагаемом устройстве, иначе не выполняется предыдущее условие.

При контролиронании блоков управления и обнаружении дефектов в потоке команд устройство формирует сигнал ошибки на ныходе 24, что может использоваться системой для рестарта программы (например, с контрольной точки, соответствующей команде Начало в контролируемом алгоритме, составляющем часть всей программы), При этом устройство сбрасывается в исходное, а в регистр 17 записываются вектора настройки, соответствующие следующему контролируемому алгоритму управления. Правильное окончание алгоритма управления может определяться по сигналу подтверждения, вырабаI тЫваемому ячейкой, соответствующей последнему оператору алгоритма (в частности для всего набора контролируемых алгоритмов может быть выделена н устройстве специальная ячейка,соответствующая команде Конец" ), причем этим сигналом устанавливается в "1" ячейка, соответствующая команде Начало формула изобретения

1. Устройство для контроля блоков управления, содержащее первый и нторой регистры, группу триггеров, первую и вторую группы элементов И, первый и второй элементы ИЛИ, группу элементов НЕ, первый и второй триггеры результата контроля, причем информационные входы первого и второго регистров подключены соответственно к входу контролируемых сигналов и входу логических условий устройства, входы синхронизации первого и второго регистров подключены к первому входу синхронизации устройства, выход первого элемента ИЛИ соединен с D-входом первого триггера результата контроля,выход которого является выходом ошибки устройства, вход сброса устройства подключен к R-входу первого триггера результата контроля, R-входам с первого по (k-1)-й триггеров группы и к

S-входу k-го триггера группы, где разрядность входа контролируемых сигналов устройства, вход сброса устройства подключен к входам сброса первого и второго регистров, выход

i-го разряда первого регистра (i=1 k) соединен с первым входом 1-го элемен136508 та И первой группы, второй вход i-го элемента И первой группы соединен с единичным выходом i-го триггера группы, выход i-го элемента И первой группы соединен с R-входом i-го триггера группы, второй вход синхронизации устройства подключен к входам синхронизации первого триггера результата контроля и с первого па

k-й триггеров группы, о т л и ч а ю— щ е е с я тем, что, с целью расшире— ния области применения за счет обеспечения воэможности контроля блоков управления, реализующих алгоритмы с различной степенью параллелизма и расширения класса обнаруживаемых дефектов, устройство содержит группу элементов ИЛИ, третью группу элементов

И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и блок ком-2О коммутации, причем выход второго триггера результата контроля является выходом подтверждения устройства,R-вход и вход синхронизации второго триггера результата контроля подключены соответственно к входу сброса и второму входу синхронизации устройства, выход второго элемента ИЛИ соединен с

D-входом второго триггера результата контроля.и с первым входом элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом первого элемента

ИЛИ, второй вход элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ соединен с выходом первого разряда второго регистра, прямые и инверс35 ные выходы разрядов второго регистра соединены с группой управляющих входов блока коммутации, группа входов

i-ro элемента И первой группы соединена с i-й выходной шиной первой группы информационных выходных шин блока коммутации, входы i-ro элемента

ИЛИ группы соединены с i-и выходной шиной второй группы информационных выходных шин блока коммутации, выход 4

i-го элемента ИЛИ группы соединен с первым входом i-го элемента И второй группы, выход i-го элемента И второй группы соединен с S-входом i-го триггера группы, второй вход i-ro элемента И второй группы соединен с нулевым выходом i-ro триггера группы, выход

i-го элемента И первой группы через

i-й элемент НЕ группы соединен с первым входом -го элемента И третьей

55 группы, выход i-го разряда первого регистра соединен с вторым входом

i-го элемента И третьей группы, выход

i-ro элемента И третьей группы соединен с (i+1) ì входом первогп алев мента ИЛИ, инверсные выходы с первого по k-й триггеров группы соединены с первой группой информационных входов блока коммутации, выходы с первого по k-й элементов И первой группы соединены с второй группой информационных входов блока коммутации, с группой входов второго элемента ИЛИ и образуют выход информации о результате контроля устройства.

2. Устройство по п.1, о т л и— ч а ю щ е е с я тем, что блок коммутации содержит регистр настройки, первую и вторую группы управляемых коммутаторов, причем группа управляющих входов блока коммутации подключена к входным шинам управления управляемых коммутаторов первой и второй групп, выходы разрядов регистра настройки соединены с входными шинами настройки управляемых коммутаторов первой и второй групп, входные информационные шины управляемых коммутаторов первой и второй групп подключены соответственно к первой и второй группам информационных входов блока коммутации, выходная шина i-го управляемого коммутатора первой группы подключена к i-й выходной шине первой группы информационных выходных шин блока коммутации, выходная шина

i-ro управляемого коммутатора второй группы подключена к i-й выходной шине второй группы информационных выходных шин блока коммутации, причем i-й управляемый коммутатор первой группы содержит первую группу из 1 элементов ИЛИ (1 e k), с второй по (1+1)-ю группы из п элементов ИЛИ (n < 2q, где

Ч читало разрядов входа логических условий устройства) и группу из 1 элементов И-НЕ, выходы которых соединены с первыми входами соответствующих элементов ИЛИ первой группы, вторые входы которых образуют входную информационную шину i-го управляемого коммутатора первой группы, выходы элементов ИЛИ первой группы образуют выходную шину i-ro управляемого коммутатора первой группы, входы q-го элемента И-НЕ группы (, = 1,1) соединены с выходами элементов ИЛИ (1 +1)-й группы, первые входы элементов ИЛИ с второй по (1+1)-ю групп образуют входную шину управления i-го управляемого коммутатора первой груп1365086

18

Риг.2 пы, вторые входы элементов ИЛИ с второй по (1+1) -ю групп образуют входную шину настройки х-го управляемого коммутатора первой группы, причем i-й управляемый коммутатор второй группы содержит первую и вторую группы из m элементов И (m c k) группу из п элементов ИЛИ, выходы элементов И первой группы соединены с первыми входами 10 соответствующих элементов И второй группы, вторые входы которых образуют входную информационную шину i-го управляемого коммутатора второй группы, выходы элементов И второй группы образуют выходную шину i-го управляемого коммутатора второй группы, входы

/-го элемента И первой группы (/=1,m) соединены с выходами элементов ИЛИ

l-й группы, первые входы элементов

ИЛИ с первой по m-ю групп образуют входную шину управления i-го управляемого коммутатора второй группы, вторые входы элементов ИЛИ с первой по

m-ю групп образуют входную шину настройки i-го управляемого коммутатора второи группы.

1365086

1 хк

0(исх.f, хх

3 кх хх

2 хх а" а"

12245б 7631

OD0000000

1ОООООООООО

ОООООООООО

00ff000f0f0 01000000000

0000000иа ИОО0000000

Ит00001 Отf00001

0ff00010f0 000ОО00000

10000ООООО

ОООООИООО

fff000Df

О000000

000О00000

Саат00010

0f 00000001

0000000000

1365086

1365086

Фиа б

1365086 ж

Риг. б

1365086

Составитель Д. Ванюхин

Техред Л. Сердюкова Корректор С.Черни

Редактор Н. Егорова

Заказ 6611/42 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4