Устройство для управления стабилизированным преобразователем постоянного напряжения в постоянное

Иллюстрации

Показать всеРеферат

Изобретение относится к преобразовательной технике и может быть использовано при разработке устройств электропитания постоянного напряжения . Цель изобретения - повышение быстродействия. За счет введения .D- триггера 21 и двухвходового элемента И-НЕ 22 обеспечивается режим работы , при котором отработка воздействия на выходе преобразователя осуществляется непрерьшно в течение каждого такта работы усилителя мощности . 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) ц1) 4 Н 02 М 3/337

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР пО делАм изОБРетений и ОткРытий

Н АBTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 4051565/24-07 .(22) 22.04.86 (46) 07.01.88. Бюл. Ф 1 (71) Киевский завод электронных вычислительных и управляющих машин— головное предприятие Киевского производственного объединения "Электронмаш" им, В.И. Ленина (72) М.Ф.Черноус, А.А.Линник, Л.И.Ильфирович и П.Е.Кожемяченко (53) 621 316.727(088.8) (56) Авторское свидетельство СССР

У 736291, кл. Н 02 М 3/335, 1977.

Авторское свидетельство СССР

У 1171925, кл. H 02 М 3/337, 1965. (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ

СТАБИЛИЗИРОВАННЫМ ПРЕОБРАЗОВАТЕЛЕМ

ПОСТОЯННОГО НАПРЯЖЕНИЯ В ПОСТОЯННОЕ (57) Изобретение относится к преобразовательной технике и может быть использовано при разработке устройств электропитания постоянного напряжения. Цель изобретения — повышение быстродействия. За счет введения .Dтриггера 21 и двухвходового элемента И-НЕ 22 обеспечивается режим работы, при котором отработка воздействия на выходе преобразователя осуществляется непрерывно в течение каждого такта работы усилителя мощности. 2 ил.

1365291

Изобретение относится к электротехнике, а именно к преобразователям постоянного напряжения в постоянное, и может быть использовано в качест5 ве вторичных источников питания.

Цель изобретения — повьппение быстродействия стабилизированного преобразователя постоянного напряжения в постоянное. 10

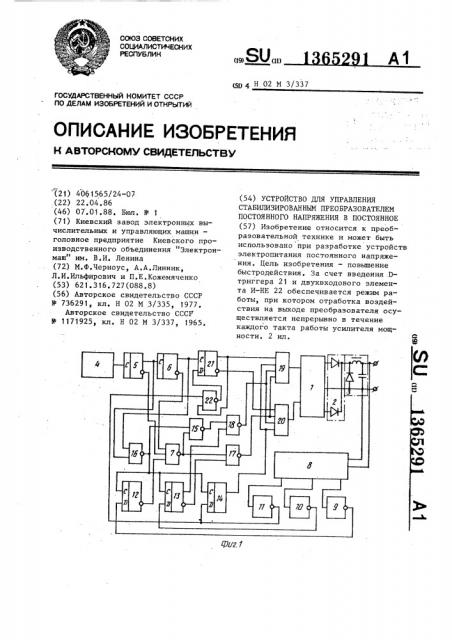

На фиг. 1 представлена функциональная схема предлагаемого устройства, на фиг. 2 — временные диаграммы, поясняющие работу устройства.

Устройство для управления стаби- 16 лизированным преобразователем постоянного напряжения в постоянное, выполненным на двухтактном усилителе

1 мощности, выходы которого через выпрямитель 2 подключены к фильтру 3, содержит генератор 4 тактовых импуль.сов, выход которого подключен к входу первого счетного триггера 5, прямой выход которого подключен к входу второго счетного триггера 6, а инвер- 25 сный выход — к второму входу трехвходового элемента И-НЕ 7, первый вход которого подключен к инверсному выходу второго счетного триггера 6, усилитель 8 постоянного тока, входы 30 которого предназначены для подключения к выходным зажимам фильтра 3, а три выхода подключены соответственно к входам первого 9, второго 10 и третьего 11 пороговых элементов, выходы которых подключены соответственно к D-входам первого 12, второго 13 и третьего 14 D-триггеров, тактовые входы которых объединены между собой и первым входом третьего двухвходово- 40

ro элемента И-НЕ 15 и подключены к выходу четвертого двухвходового элемента И-НЕ 16, первый вход которого подключен к прямому выходу первого счетного триггера 5, а второй — к 45 прямому выходу второго счетного триггера 6, инверсный выход первого Dтриггера 12 подключен к третьему входу трехвходового элемента И-HE 7, выход которого подключен к второму входу третьего элемента И-НЕ 15 и к первому входу второго двухвходового элемента И-НЕ 17, второй вход которого подключен к инверсному выходу второго D-триггера 13, прямой выход которого подключен к второму входу первого элемента И-НЕ 18, первый вход которого подключен к выходу третьего элемента И-НЕ 15, а выход — к объединенным третьим входам первого

19 и второго 20 четырехвходовых элементов И, выходы которых предназначены для подключения к управляющим входам усилителя 1 мощности, выход второго двухвходового элемента И-НЕ

17 подключен к объединенным четвертому входу первого и второму входу второго элементов И 19 и 20, прямой выход третьего D-триггера 14 подключен к объединенным второму входу первого 19 и четвертому входу второго 20 элементов И.

Устройство дополнительно снабжено четвертым D-триггером 21 и пятым двухвходовым элементом И-HE 22, причем первый вход пятого двухвходового элемента И-НЕ 22 соединен с выходом третьего порогового элемента 11, второй вход соединен с прямым выходом четвертого D-триггера 21 и первым входом первого элемента И, тактовый вход четвертого D-триггера 21 подключен к прямому выходу второго счетного триггера, 6 D-вход — к выходу пятого двухвходового элемента И-НЕ

22, а инверсный выход — к первому входу второго элемента И.

Устройство работает следующим об- . разом.

Характерными для предлагаемого устройства являются три режима работы, а именно: режим максимальной нагрузки, режим минимальной нагрузки и режим холостого хода. В режиме мак- . симальной нагрузки компенсация низкочастотных пульсаций происходит эа счет дискретного изменения длительности управляющих импульсов от мак1 симального до среднего значений (фиг. 2, интервал t„ - с ). Во втором режиме стабилизация выходного напряжения происходит за счет дискретного изменения длительности управляющих импульсов от минимального до среднего значений (фиг. 2, интервал г. — r6), В режиме холостого хода стабилизация выходного напряжения обеспечивается за счет формирования пачек управляющих импульсов минимальной длительности, которыми осуществляется периодическая подпитка конденсатора фильтра 3 (фиг. 2, интервал с Ф с5) °

Отличительной особенностью режима работы предлагаемого образовате ля является то, что переключение

D-триггеров 12-14 происходит в каж1365291

10

35

50

55 дом такте работы двухтактного усилителя f.ìîùíîñòè, а прохождение последнего импульса в предыдущей и первого импульса в последующей пачке управляющих импульсов минимальной длительности через разные плечи усилителя 1 мощности обеспечивается режимом работы четвертого D-триггера

21 и пятого элемента И-НЕ 22.

Генератор 4 вырабатывает исходную последовательность прямоугольных импульсов, которая поступает на вход цепочки из двух последовательно сое- диненных счетных триггеров 5 и 6 и

D-триггера 21. С выхода D-триггера

21 прямоугольные импульсы, сдвинутые о один относительно другого на 180 поступают на первые входы элементов

И 19 и 20, чем достигается управление работой усилителя 1 мощности в двухтактном режиме.

Выпрямленное на выпрямителе 2 (диаграмма P) и отфильтрованное фильтром 3 напряжение поступает на выходные выводы преобразователя.

Сигнал с выходов усилителя 8 постоянного тока с тремя раздельными выходами, вход которого подключен к выходным выводам преобразователя, подается на входы пороговых элементов 9-11,, которые управляют очередностью переключения D-триггеров 1214 в процессе стабилизации выходного напряжения. При значении величины выходного напряжения (диаграмма Ж) ниже определенного уровня на выходе всех трех пороговых элементов появляются сигналы логической "1", которые поступают на информационные вхо ды D-триггеров 12-14. По переднему фронту импульса, приходящего на тактовые входы D-триггеров 12-14 с выхода логического элемента 2И-HE 16 (диаграмма Г), на их прямых выходах появляются сигналы логической "1".

При этом сигнал логического нуля с инверсного выхода первого D-триггера 12 поступает на первый вход эле.-. мента ЗИ-НЕ 7 и запирает его выходными сигналами второго D-триггера 13 открывается первый элемент 2И-НЕ 18 и закрывается второй элемент 2И-НЕ

17, выходной сигнал с третьего Dтриггера 14 открывает элементы 4И

19 и 20; на которые через элемент

2И-HE 15 и элемент 2И-НЕ 18 подается последовательность импульсов с короткими паузами (диаграмма Г), сформированная четвертым элементом 2И-HE

16 с помощью сигналов с прямых выходов первого 5 (диаграмма А) и второго 6 (диаграмма Б) счетных триггеров. При прохождении последовательности импульсов через элементы 4И они запираются в начале каждого такта работы усилителя 1 мощности, чем достигается формирование импульсов управления (диаграммы О и П) максимальной длительности (фиг.- 2, интервал t< — t ), а также исключается возможность прохождения сквозных токов в усилителе 1 мощности, так как включение и выключение транзисторов преобразователя разнесено во времени. При увеличении значения выходного напряжения преобразователя выходной сигнал на первом выходе усилителя 8 постоянного тока достигает значения верхнего порога срабатывания первого порогового элемента 9, оно перебрасывается в другое устойчивое состояние (диаграмма 3), при котором первый D-триггер 12 перебрасывается (диаграмма И) по переднему фронту первого после переключения порогового элемента импульса, пришедшего с второго счетного триггера

6, и выходным сигналом отпирает логический элемент И-НЕ 7. На этом элементе с помощью сигналов, поступающих с инверсных выходов первого 5 и второго 6 счетных триггеров, формируется последовательность импульсов с короткими паузами между ними (диаграмма Д), Сформированная последовательность импульсов складывается с выходными сигналами четвертого элемента 2И-НЕ

16 на третьем элементе 2И-НЕ -15 (диаграмма Е). Импульсы с выхода элемента И-НЕ 15 через первын элемент 2ИНЕ 18 поступают на элементы 4И 19 и

20, которые запираются на время их прохождения. Этим достигается формирование импульсов управления средней длительности (фиг. 2, интервал t< .— с.).

При дальнейшем увеличении значения выходного напряжения сигнал на втором выходе усилителя 8 постоянного тока увеличивается до значения верхнего порога срабатывания второго порогового элемента 10. Пороговый элемент перебрасывается в другое устойчивое состояние (диаграмма К), при котором второй D-триггер 13 пе1365291

10формула изобретения

В режиме холостого хода на конденсаторе фильтра 3 происходит увеличе-, ние значения напряжения, что приво- 15 дит к увеличению значения сигнала на третьем выходе усилителя 8 постоянного тока до верхнего порога срабатывания третьего порогового элемента 11, оно перебрасывается в дру- 20 гое устойчивое состояние (диаграм-, ма М). При этом третий D-триггер 14 переключается (диаграмма Н) передним фронтом импульса с четвертого элемента 2И-НЕ 16 и выходным сигналом логического "0" запирает элементы 4И

19 и 20, чем достигается прекращение подпитки конденсатора фильтра 3, и одновременно пороговый элемент 11 через пятый элемент 2И-НЕ 22 оста- 30 навливает четвертый D-триггер 21 в положении, обеспечивающем прохождение последнего импульса "пачка" через элемент 4И 19 и первое плечо усилителя 1 мощности. При уменьшении значения выходного напряжения третий пороговый элемент 11 перебрасывается в исходное состояние через третий D-триггер 14, открывает элементы 4И 19 и 20,и через элемент

2И-НЕ 22 запускает червертый D-триггер 21. На второй вход усилителя 1 мощности через элемент 4И 20 поступает первый короткий импульс новой пачки управляющих импульсов минималь- pg ной длительности (фиг. 2, интервал г- — с ), который обеспечивает pasмагничивание трансформатора усилителя 1 мощности и подзаряд конденсатора фильтра 3 последующими импульса- 50 ми пачки до значения напряжения, вы- зывающего срабатывание третьего порогового элемента, вследствие чего происходит запирание элементов 4И 19 и 20 (фиг. 2, интервал с4, — t<) и останов D-триггера 21, При понижении значения выходного напряжения срабатывание пороговых элементов происхо- дит в обратном порядке, реключается (диаграмма Л) передним фронтом импульса с второго счетного триггера 6 и выходными сигналами за.пирает первый элемент 2И-НЕ 18 и отпирает второй элемент 2И-НЕ 17, через который на элементы 4И 19 и 20 проходят импульсы с логического элемента И-НЕ 7, определяющие формирование импульсов управления минимальной длительности (фиг. 2, интервал t> — t+).

Таким образом, изобретение позволяет повысить быстродействие отработки возмущающего воздействия и обеспечить по сравнению с базовым объектом большую точность поддержания заданного напряжения на выходе преобразователя.

Устройство для управления стабилизированным преобразователем постоянного напряжения в постоянное, выполненным на двухтактном усилителе мощности, выходы которого через выпрямитель подключены к фильтру, содержащее генератор тактовых импульсов, выход которого подключен к входу первого счетного триггера, прямой выход которого подключен к входу второго счетного триггера, а инверсный выход — к второму входу трехвходового элемента И-НЕ, первый вход которого подключен к инверсному выходу второго счетного триггера, усилитель постоянного тока, входы которого предназначены для подключения к выходным зажимам фильтра, а три выхода подключены соответственно к входам первого, второго и третьего пороговых элементов, выходы которых подключены соответственно к D-входам первого, второго и третьего D-триггеров, тактовые входы которых объединены между собой и первым. входом. третьего двухвходового элемента И-НЕ и подключены к .выходу четвертого двухвходового элемента И-НЕ, первый вход которого подключен к прямому выходу первого счетного триггера, а второй — к прямому выходу второго счетного триггера, инверсный выход первого D-триггера подключен к третьему входу трехвхбдавого элемента

И-НЕ, выход которого подключен к второму входу третьего элемента И-НЕ и к первому входу второго двухвходо- вого элемента И-HE второй вход которого подключен к инверсному выходу второго D-триггера, прямой выход которого подключен к второму входу первого двухвходового элемента И-НЕ, первый вход которого подключен к выходу третьего элемента -HE а вы-, ход — к объединенным третьим входам первого и второго.четырехвходовых элементов И, выходы которых предназначены для подключения к управляющим

1365291

Составитель С.Станкевич

Техред Л.Сердюкова Корректор Л.Пилипенко

Редактор И.Горная

Заказ 6653/53 Тираж 665 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная, 4 входам усилителя мощности, выход второго двухвходового элемента И-HF. подключен к объединенным четвертому входу первого и второму входу второго элементов И, прямой выход третьего D-триггеров подключен к объединенным второму входу первого и четвертому входу второго элементов И, . о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, оно снабжено четвертым D-триггером и пятым двухвходовым элементом И-НЕ, причем первый вход пятого двухвходового элемента И-НЕ соединен с выходом третьего порогового элемента, второй вход соединен с прямым выходом четвертого D òðèããåðà и первым входом первого элемента И, тактовый вход четвертого D-триггера подключен к прямому выходу второго счетного триггера, D-вход - к выходу пятого двухвходового элемента И-НЕ, а инверсный выход — к первому входу второго элемента И.