Устройство сравнения на мдп-транзисторах

Иллюстрации

Показать всеРеферат

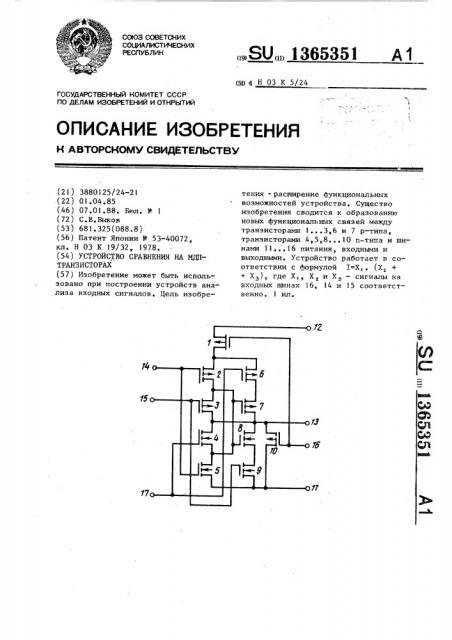

Изобретение может быть использовано при построении устройств анализа входных сигналов. Цель изобретения - расширение функциональных возможностей устройства. Существо изобретения сводится к образованию новых функциональных связей между транзисторами 1...3,6 и 7 р-типа, транзисторами 4,5,8...10 п-типа и шинами 11... 16 питания, входными и выходными. Устройство работает в соответствии с формулой ,. (Xj + + Хз), где X,, Xj и Хэ - сигналы на входных пшнах 16, 14 и 15 соответственно . 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5р 4 Н 03 К 5/24

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMV СВИДЕТЕЛЬСТВУ

15

1У

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

00 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3880125/24-21 (22) 01.04.85 (46) 07.01.88. Бюл. У 1 (72) С.В.Быков (53) 681.325(088.8) (56) Патент Японии N< 53-40072, кл. Н 03 К 19/32, 1978. (54) УСТРОЙСТВО СРАВНЕНИЯ НА МДПТРАНЗИСТОРАХ (57) Изобретение может быть использовано при построении устройств анализа входных сигналов. Цель изобре„„Я0„„1365351 А 1 тения - расширение функциональных воэможностей устройства, Существо изобретения сводится к образованию новых функциональных связей между транзисторами 1...3,6 и 7 р-типа, транзисторами 4,5,8...10 и-типа и шинами 11...16 питания, входными и выходными. Устройство работает в соответствии с формулой I=X<. (Х +

+ Хз), где Х<, Х и Х вЂ” сигналы на входных шинах 16, 14 и 15 соответственно. 1 ил.

365351

У =.Х, (Х ® Х ), щщИПИ. Заказ 6657/56 Тираж 928

Подписное

Произв.-полигр. пр — тие, r. Ужгород, ул. Проектная, 4

1 1

Изобретение относится к импульсной технике и может быть использовано при построении устройств анализа входных сигналов.

Целью изобретения является расширение функциональных возможностей за счет обеспечения реализации дополнительных логических функций.

На чертеже представлена принципиальная схема устройства сравнения на МДП-транзисторах.

Устройство сравнения на ИДП-транзисторах содержит транзисторы 1,2,3 р-типа, последовательно включенные с транзисторами 4 и 5 п-типа, транзисторы 6 и 7 р-типа включены последовательно с транзисторами 8 и 9 п-типа, истоки транзисторов 5,9 и

1Î и-типа подключены к первой шине

11 питания, исток транзистора 1 подключен к второй шине 12 питания, а истоки транзисторов 3,4, 7,8 и 10 подключены к выходной шине 13, истоки восьмого и шестого транзисторов

2 и 6 соединены, затворы транзисто.ров 7 и 8 подключены к истокам транзисторов 2 и 5, затвори транзисторов

2 и 5 подключены к первой входной шине 14, затворы транзисторов 3 и 9

-подключены к второй входной шине

15, затворы транзисторов 1 и 10 подключены к третьей входной шине 16, причем затворы транзисторов 4 и 6 подключены к четвертой входной шине

17 °

Устройство работает следующим образом.

На шину 12 подается питание, а шина 11 подключается к общей шине источника питания.

Если на шине 16 присутствует логическая 1, то открыт транзистор 10 и закрыт транзистор 1. Состояние остальных транзисторов безразлично.

На выходной шине присутствует сигнал логического О. Если на шине 16 логический О, то при наличии на входных шинах 14, 15 и 17 соответственно сигналов логических О и 1 открыты транзисторы 1,2,3,7 — на шине 13 логическая 1. Если на нинах 14,17 и 15 соответственно логические О и 1, то открыты транзисторы 1, 2,6,8 и 9— на шине 13 логический О. Если на шинах 14,17 и 15 соответственно логические 1 и О, то открыты транэисто5 ры 1,3,4,597 — на шине 13 логический О. Если на шинах 14,15 и 17 соответственно логические I и О, то открыты транзисторы 1,4,6,7,9 — на шине 13 логическая. 1.

Устройство работает в соответствии с формулой где Х, — сигнал на шине 16;

Х вЂ” сигнал на шине 14;

Х вЂ” сигнал на шине 15 (на шине 17 — Х ).

Формула изобретения

Устройство сравнения на МДП-транзисторах, содержащее транзисторы, входные, выходную шины и шину питания, о т л и ч а ю щ е е с я тем, 26 что, с целью расширения функциональ-. ных возможностей за счет обеспечения реализации дополнительных логических функций, первый, второй, третий транзисторы первого типа, четвертый, пя3р тый транзисторы второго типа включены последовательно, шестой, седьмой транзисторы первого типа, восьмой, девятый транзисторы второго типа включены последовательно, истоки пятого, девятого, десятого транзисторов второго типа подключены к первой шине питания, исток первого транзистора подключен к второй шине питания, истоки третьего, четвертого, седьмого, восьмого, десятого транзисторов подключены к выходной шине, истоки второго, шестого транзисторов соединены, затворы седьмого, восьмого транзисторов подключены к истокам

4> второго, пятого транзисторов, затворы второго, пятого транзисторов подключены к первой входной шине, затворы третьего, девятого транзисторов подключены к второй входной шине, затворы первого, десятого транзисторов подключены к третьей входной шине, затворы четвертого, шестого транзисторов подключены к четвертой входной шине.