Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

СООЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19) П1) А2 (504 G 11 С 29 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Q(P t (Ъ Г1 7 г, . >-

) l3

ЬФ.. (61) 1105944 (21) 3975474/24-10 (22) 14 ° 11 ° 85 (46) 23 01. 88 Вюл. У 3

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPbITPM (72) А.В.дрозд, E.Ë.Ïoëèí, В.A.Ñoêîлов, В.А.Минченко и В.П.Карпенко (53) 681.327.6(088.8) (56) Авторское свидетельство СССР

У 1-105944, кл. С 11 С 29/00, 1984. (54)(57) 3АПОМИНАКЩЕЕ УСТРОЙСТВО С

САМОКОНТРОЛЕМ по авт.св. к 1105944, о т л и ч а ю щ е е с я тем, что, с целью поВышения точности, в него введены последовательно соединенные информационные шины, третий коммутатор, регистр, четвертый коммутатор и первый триггер, шины общих сигналов контроля, подключенные к другим входам регистра, выходы которого соединены с информационными входами четвертого коммутатора, последователь. но соединенные шина пуска, блок запуска, первый счетчик и второй счетчик, подключенный выходом к управ" ляющему входу четвертого коммутатора, другой .вход второго счетчика подключен к первому выходу блока запуска, последовательно соединенные шина в контрольного кода, входной блок контроля, второй триггер, первый датчик .ошибок, подключенный выходом к одному из дополнительных информационных входов третьего коммутатора, и последовательно соединенные третий триггер и второй датчик ошибки, подключенный выходом к другому дополнительному информационному входу третьего коммутатора, третий счетчик, блок синхронизации с подключенной к его входу шиной синхронизации, шины первого и второго выходных кодов, подключенные соответственно к Второму выходу первого счетчика и к выходу второго счетчика, первая и вторая шины блокировки, соединенные соответственно с входами сброса первого и второго датC чиков ошибки, при этом блок синхро- @ низации подключен выходами к синхровходам соответствующих триггеров, регистра, первого и третьего счетчиков, выход третьего счетчика соединен с управляющим входом третьего коммутатора, другой вход третьего счетчика подключен к второму входу блока запуска, третий выход которого соединен через первый триггер с входом блокировки синхровхода регистра и входдм блокировки счета первого счетчика, информационные входы входного блока контроля соединены с соответствующими информационными входами блока памяти, а дополнительный выход — с соответствующими дополнительными входами блока памяти и первого коммутатора, выход блока контроля подключен к информационному входу третьего триг гера.

1368921

Изобретение относится к запоминающим устройствам, в частности к запоминающим устройствам с развитой системой аппаратного контроля, обеспечивающей Обнаруженне и локализацию неисравностей как при эксплуатации устройства, так и в процессе его отладки, и является усовершенствованием устройства по авт.св ° 10

В 1105944.

Целью изобретения является повышение точности контроля °

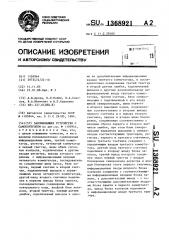

На фиг.1 представлена структурная схема устройства, на фиг.2 15 временные диаграммы сигналов для случая обнаружения ошибки при считывании слов из блока памяти.

Устройство содержит соединенные определенным образом входной блок 1 20 контроля, блок 2 управления, блок 3 запуска, первый триггер 4, первый .коммутатор 5,блок 6 синхронизации, первый датчик 7 ошибки, блок 8 памяти, дополнительный блок 9 памяти, 25 блок 10 контроля, второй коммутатор 11, второй триггер 12, блок 13 сравнения, второй датчик 14 ошибки, первый счетчик 15, третий коммутатор 16, регистр 17, второй счетчик 18, 30 третий счетчик 19, четвертый коммутатор 20, третий триггер 21, информационные шины 22, первая и вторая шины 23 и 24 блокировки, шина 25 контрольного кода, информационные входы 26 устройства, управляющий вход

27 устройства, шины 28 общих сигналов контроля, шина 29 пуска, шина 30 синхронизации, информационные выходы 31 устройства, первый контроль- 40 ный выход 32 устройства, второй контрольный выход 33 устройства, шины

34 и 35 первого и второго кодов устройства (локалиэующих кодов).

Устройство работает следующим образом.

В блок 8 памяти записывается последовательность слов, включающих как информационные, так и соответ- 50 ствующие им контрольные разряды.

Информационные разряды поступают на информационные входы блока 8 памяти через информационные входы 26 устройства. Контрольные разряды прохОДЯТ на контрольный вход блока 8 памяти с выхода контрольного кода входного блока 1 контроля. Контрольные разряды определяются входным блоком

Ю контроля путем свертки, например, по модулю три, информационных разрядов, поступающих на его информационные входы с входа устройства 26. Кроме того, входной блок контроля осуществляет проверку входных слов путем сравнения вычисленных им контрольных разрядов с контрольными разрядами, поступающими на его контрольный вход с шины 25 контрольного кода устройства. В результате проверки формируется сигнал контроля входных слов, поступающий с выхода сигнала контроля входного блока 1 контроля на информационный вход второго триггера 12 ° Запись этого сигнала в триггер 12 осуществляется после завершения переходных процессов свертки и сравнения входного блока 1 контроля по фронту (пЕреднему или заднему) синхросигнала, снимаемого с выхода блока 6 синхронизации. С выхода второго триггера 12 сигнал контроля поступает на вход установки первого датчика 7 ошибки. Датчик 7 ошибки реагирует на значение "Ошибка" сигнала контроля, запоминая его при записи в блок 8 памяти полезной информации.

При считывании слов с выходов блока 8 памяти разряды слов поступают на информационные выходы 31 устройства, а также на входы 10 контроля, осуществляющего свертку информационных разрядов слова и сравнения ре» зультата свертки с контрольными разрядами слова. При этом формируется сигнал контроля блока памяти, поступающий на первый контрольный выход 32 устройства, а также через третий триггер 21 — на вход второго датчика 14 ошибки. Второй триггер 21 и второй датчик 14 ошибки работают аналогично первому триггеру 12 и первому датчику 7 ошибки, обеспечивая запоминание значения "ошибка" сигнала контроля блока 8 памяти по завершению переходного процесса, при считывании полезной информации. Синхросигналы на сиихровход третьего триггера 21 поступают с выхода блока 6 синхронизации. Сигналы контроля с выходов первого 7 и второго 14 датчиков ошибки, а также внешние сигналы контроля, поступающие с информационных шин 22, подаются на информационные входы третьего коммутатора 16. Внешние сигналы контроля со1368921 общают данному устройству информацию о неисправности других устройств, решающих совместно единую задачу.

Работа устройства начинается с подачи на вход блока запуска 3 через шину 29 пуска сигнала "Начало".

При этом блок 3 запуска формирует импульс сброса, который устанавливает в нулевое состояние первый 15, второй 18 и третий 19 счетчики, а также первый триггер 4. По окончании действия импульса сброса первый 15 и третий 19 счетчики под действием синхросигналов, поступающих на их счетные входы с выходов 6 синхронизации, начинают синхронно изменять свои состояния. Коды состояния третьего счетчика 19 поступают с его выхода на управляющий вход третьего коммутатора 16. При этом сигналы контроля, каждый иэ которых однозначно соответствует определенному состоянию первого 15 и третьего 19 счетчйков, последовательно транслируются с информационных входов третьего коммутатора 16 на его выход, образуя общий сигнал контроля. Общий сигнал контроля с выхода третьего коммутатора 16 поступает на информационный вход регистра 17, на другие информационные входы которого подаются с шины 28 общих сигналов контроля устройства внешние общие сигналы контроля. Эти сигналы организованы аналогично сигналу на выходе третьего коммутатора 16,т.е. последовательно принимают значения отдельных сигналов контроля устройства, также участвующих в решении общей задачи. Прием общих сигналов контроля в регистр 17 осуществляется по синхросигналам, поступающим на его синхровход с выхода блока 6 синхронизации. С выхода регистра 17 общие сигналы контроля подаются на информационные входы четвертого коммутатора 20. На управляющий вход четвертого коммутатора 20 поступает . код с выхода второго счетчика 18> на счетный вход которого подается сигнал переноса или старшего разряда с первого выхода первого счетчика 15.

Следовательно, состояния второго счетчика 18 изменяются реже, чем состояния первого счетчика 15, и в течение действия одного кода состоя ния второго счетчика 18 на выход четвертого коммутатора 20 транслиру5

30 ется соответствующий общий сигнал контроля, который принимает за это время значения всех включенных в него сигналов контроля. Таким образом, выход четвертого коммутатора последовательно принимает значения сигналов контроля всех устройств, участвующих в решении общей задачи.

При фиксации неисправности в одном из этих устройств, включая данное, соответствующий сигнал контроля, а следовательно и выход четвертого коммутатора 20 изменяют свои эначения на противоположные, устанавливая первый триггер 4 в состояние обнаружения ошибки. Сигнал с выхода первого триггера 4 поступает на входы блокировки синхровхода регистра 17 и блокировки счета первого счетчика

15, препятствуя восприятию регистром 17 и счетчиком 15 синхросигналов. Таким образом, регистр 17 фиксирует значение общих сигналов контроля, содержащих информацию об ошибке. Первый счетчик 15, работающий синхронно с третьим счетчиком 19, фиксирует состояние, однозначно соответствующее сигналу контроля, который несет информациИ об ошибке.

Код этого состояния является номером неисправного устройства в составе группы устройств, объединенных в части контроля общим сигналом контроля.

Номер неисправного устройства поступает на шину .35 второго (локалиэующего) кода устройства, второй счетчик 18 фиксирует состояние, однозначно соответствующее общему сигналу контроля, который содержит информацию об ошибке. Код состояния является номером неисправной группы устройств.

Номер неисправной группы устройств поступает на шину 34 первого (лока45 лиэующего) кода устройства. Коды на шинах 34 и 35 выходных кодов однозначно указывают на неисправное устройство. Например, несоответствие информационных и контрольных разрядов входных слов приводит к установке сигнала контроля на выходе датчика 7 ошибки в состояние "ошибка". Это по» казано на фиг.2, изображающей временные диаграммы входов устройства и вы55 ходов его блоков .Ошибка фиксируется первым датчиком 7 ошибки после его разблокировки сигналом, поступающим на его вход сброса первой шины 23 блокировки. Далее значение ошибки

1368921 сигнала контроля проявляется на выходе третьего коммутатора 16. При этом первый счетчик 15 принимает нулевой код состояния. В последующие моменты времени на интервалах, ког да первый счетчик 15 переходит в состояние "1", информация об ошибке проявляется на выходе регистра 17. В момент времени tg информация об ошибке транслируется на выход четвертого коммутатора 20 и через полупериод синхросигналов принимается в первый триггер 4 (момент =), фиксирующий состояние регистра 17 и счетчиков 15 и 18. Выходы этих счетчиков принимают соответственно значения "0" и "1", составляющие номер неисправного устройства

"0" (в данном случае зто устройство предшествует рассматриваемому).

В момент времени t> информация об ошибке, первоначально зафиксированная датчиком 14 ошибки, транслируется на выход четвертого коммутатора 20 26 и в момент времени t записывается в триггер 5, фиксирующий состояние регистра. 17 и счетчиков 15 и 18.

Выходы счетчиков 18 и 15 принимают соответственно значения "0" и "2", составляющие номер данного устройства: "02". Появление кода номера

"02" на шинах 34 и 35 выходных кодов свидетельствует о неисправности блока 8 памяти.

Дальнейшая локализация неисправности осуществляется средствами отладки и диагностирования системы контроля (блоки 1,2,5,9, 10, 1! и 13) .

В блок 8 памяти записывается тестовая последовательность слов, контрольные разряды которых, как и в рабочем режиме формируется входным блоком 1 контроля. Считываемая иэ блока 8 памяти информация поступает на выходы устройства 31, а также на входы блока 10 контроля, вырабатывающего сигнал контроля. В блоке 2 управления, 1 реализованном, например, в ниде тумблерных переключателей, имеющих два положения "1" и "0", задается двоичный код i. Этот код подается на управляющие входы первого 5 и второго 1 1 коммутаторов, выбирающих при этом сигналы с входа и выхода i-го разряда блока 8 памяти. С выхода первого коммутатора 5 сигнал заносится в одноразрядный дополнительный блок 9 памяти, устроенный подобно части блока 8 памяти, хранящей один разряд. С выхода второго коммутатора 11 и выхода дополнительного блока 9 памяти сигналы поступают на входы блока 13 сравнения, вырабатывающего сигнал проверки i-ro разряда блока 8 памяти.

При обнаружении ошибки на выходе блока 10 контроля, являющимся выходом 32 устройства, тестовая входная последовательность слов подается на входы устройства 26 многократно и заданием различных кодов на управляющие входы первого 5 и второго 11 коммутаторов определяются значения сигнала.(для всех разрядов блока 1 памяти. Таким образом, локализуется неисправность данного устройства с точностью до разряда блока 8 памяти.

1 36892 f

29

35 2 Я 9 S Е 7 Ф Я 10 77781 Ю 1ХЮ77М)УЯУ81

Вх.Щ

"Начало"

Вх.29 бл 18

6л.lg

"дивдат

bJI.7

Бл.6

&)7

Q.2

Бл.21

Фиг.2

Редактор А. Ворович

307/53 Тираж 590 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ

Производственно-полиграфическое предприятие, r.Óæãîðîä,ул.Проектная, 4

22

23

29

Составитель Н.Вихрова

Техред Л.Олийнык КорректорМ.Максимишинец е