Резервированный делитель-формирователь

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (191 (И) (5Н 4 " 03 К 23/00

ОС

ПИСАНИЕ ИЭОБРЕТ

УДАРСТВЕННЫЙ КОМИТЕТ СССР

ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

А BTOPCHOMY СВИДЕТЕЛЬСТВУ

21) 4101492/24-21

22) 28.05 ° 86

46) 23.01.88, Бюл. У 3

72) M.H ° Пархоменко

53) 621.374(088.8)

56) Авторское свидетельство СССР

736382, кл ° Н 03 К 23/00, 06.12.73.

Авторское свидетельство СССР

477545, кл. Н 03 К 23/00, 14.12.73.

4) РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ-ФОРМИВАТЕЛЬ

7) Иэобретение относится к импульсй технике и может быть испольэовадля органиэации синхронной рабо каналов резервированного цифрового комплекса. Цель изобретения — расширение функциональных воэможностей— достигается путем обеспечения работы как при синхронных, так и при расфаэированных входных сигналах. Для этого в резервированный делитель-формирователь дополнительно введены элемент 5 сравнения, инвертор 8 и второй элемент И 9. Кроме того, устройство содержит шину 1 синхронизирующего сигнала, регистр 2, 0-триггер 3, мажоритарные элементы 4, выходные шины 6, первый элемент И 7 и элемент ИЛИ 10. На чертеже показан первый канал устройства. Второй и третий каналы выполнены аналогично первому. 1 ил.

68982 2 расфазированы и начинаются, соответственно, в I, II u III каналах) разряды регистра 2 и D-триггер 3 устанавливаются в 1 канале в состояния

5 (1,1,0,1), во II канале (1,0,0,1), в III канале (1,0,1,1). В III канале элемент 5 устанавливается в нуле10

1

13

Изобретение относится к импульсной технике и может быть использовано для органиэации синхронной работы каналов резервированного цифрового комплекса.

Цель изобретения расширение функциональных возможностей путем обеспечения работы как при синхронных, так и при асинхронных (расфазированных) входных сигналах.

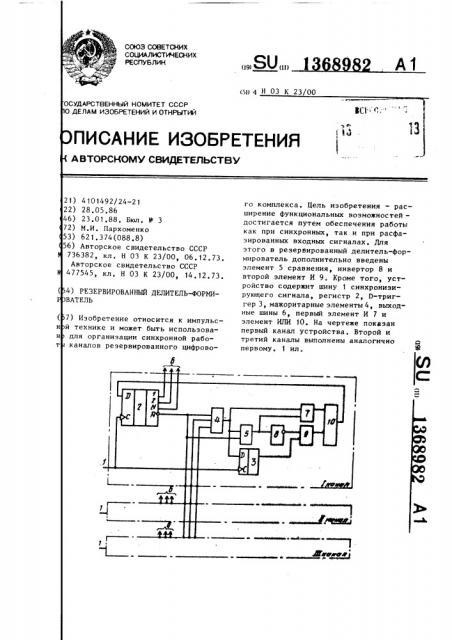

На чертеже приведена электрическая структурная схема делителя-формирователя.

Резервированный делитель-формирователь содержит шину 1 синхронизирующих сигналов, которая соединена с синхронизирующими входами регистра

2 и D-триггера 3, инверсные выходы старших разрядов регистра 2 всех каналов соединены с входами мажоритарных элементов 4 всех каналов, и кроме того, в своем канале с первым входом элемента 5 сравнения, выходы регистра 2 соединены с выходными шинами 6, второй вход элемента 5 сравнения соединен с выходом мажоритарного элемента 4, с первым входом первого элемента И 7 и с информациочным входом D-триггера 3, выход лемента 5 сравнения соединен с вторым входом элемента И 7 и через инвертор

8 с первым входом второго элемента

И, второй вход элемента И 9 соединен с выходом D-триггера 3, выходы элементов И 7 и 9 соединены с первым и вторым входами элемента ИЛИ 10, выход которого соединен с информационным входом регистра 2.

Делитель-формирователь работает следующим образом.

По включении питания триггеры устройства могут установиться в произвольное состояние, Предположим, что (в качестве примера рассмотрен 3-х разрядный регистр) в канале 1 первый, второй, третий разряды регистра 2 установились в состояния (1,0,0) в канале II (0,0,0) в канале III (0,1,0), D-триггера 3 всех каналов — в единичном состоянии. Тогда выходы элементов 4 и 5, всех каналов находятся в единичном состоянии, а выходы инверторов

8 всех каналов — в нулевом состоянии.

Элементы 7 всех каналов открыты, а элементы 9 закрыты.

По первому синхроимпульсу с шины

1 (пусть синхроимпульсы всех каналов

50 вое состояние, закрывая элемент 7 и открывая элемент 9. Так как в III канале D-триггер 3 остается в единичном состоянии, то на выходе элемента 10 имеется единичное состояние, как и на выходе элемента 4.

В 1 канале по второму синхроимпульсу разряды регистра 2 устанавливаются в единичное состояние, а элементы 4 всех каналов в нулевое состояние, Во II канале элемент 5 устанавливается в нулевое состояние, закрывая элемент 7 и открывая элемент 9, Так как Р-триггер 3 остается в единичном состоянии, то на выходе элемента 10 имеется также единичное состояние.

В III канале элемент 5 устанавливается в единичное состояние, открывая элемент 7 и закрывая элемент 9.

На выходе элемента 10 имеется нулевое состояние (как и на выходе элемента 4).

По второму синхроимпульсу с шины

1 во II канале разряды регистра 2 и D-триггер 3 устанавливаются в состояние (1,1,0,0), элемент 10 устанавливается в нулевое состояние.

По второму синхроимпульсу с шины 1 в III канале разряды регистра 2 и

D-триггер 3 устанавливаются в состояния (О, 1,0,0), мажоритарные элементы всех каналов устанавливаются в единичное состояние.

В I канале элемент 5 устанавливается в нулевое состояние, закрывая элемент 7 и открывая элемент 9. На выходе элемента 10 имеется единичное состояние (как и на выходе D-триггера 3).

Во II канале элемент 5 переходит в единичное состояние, открывая элемент 7 и закрывая элемент 9. На выходе элемента 10 — единичное состояние.

По третьему синхроимпульсу с шины 1 канала I состояние элементов в I канале не изменяется °

По третьему синхроимпульсу II канала разряды регистра 2 и D-триггер

Ф о P м у л а и з о б р е т е н и я

1368982 4

3 во II н ка але устанавливают в еди- Так как регистры 2 всех каналов ничное состояние элементы 4 всех ка- сфазированы, то первым свое состояналов и элемент 10 в нулевое состоя- ние изменяет регистр на синхронизиУ

HHP . рующии вход которого поступает перВ 1 канале элемент 5 устанавлива5 вый после фазирования каналов синется в единичное состояние, открывая хроимпульс ° Таким регистром является элемент 7 и закрывая элемент 9. На регистр 2 III канала ° Смена информавыходе элемента 10 — нулевое состоя- ции последовательно осуществляется в 1 и во II каналах.

В III канале элемент 5 устанавли- Иаксимальное время фазирования вается в нулевое состояние, закрывая сбившихся каналов равно (п Т ) вд элемент 7 и открывая элемент 9. На где п — число разрядов регистра, выходе элемента 10 имеется нулевое Т „ — период синхронизирующих сигсостояние (как и на выходе Р-тригге- !5 налов. ра 3).

По третьему синхроимпульсу III Рас"мотрен наиху асcìîòðåí наихудший случай: когканала в III канале аз я ы егис да расфазированы все каналы при расра 2 и D-триггер 3 пе ехо ят в сор одят в со- фаэированных входных сигналах. В стояние (0,0,1 О) элемент 5 пе ехорехо 2р этом случае сдвиг между одноименными разрядами каналов равен сдвигу элемент 7 и закрывая элемент р а элемент 9. между входными сигналами.

По четвер гому синхроимпульсу регистр 2 и D-триггер 3 1 и II каналов переходят в состояние (0,1,1,0), а в III канале регистр 2 и D-триг- Резервированный делитель-формигер 3 устанавливаются в состояния (0 0 0 О) рователь, содержащий три канала деле0,0,0,0), а элемент 5 — в нулевое ния, каждый из которых содержит шисостояние. ну синхронизирующих сигналов, соедиПо пятому синхроимпульсу состоя- 30 ненную с синхронизирующими входами ние регистров 2 и D-триггеров 3 в регистра и D-триггера, первый эле I и II каналах (0,0,1,0), в III канале (О О О О С ст мент И, выход которого соединен с

) . о ояние остальных первым входом входом элемента ИЛИ выход элементов прежнее, ° которого соединен с информационным

По шестому синхроимпульсу I кана- одом регистра. и мажоритарный элела состояние регистра 2 и D-тригге- мент, входы которого соединены с сор анала (0,0,0,0), элементы 4 а 3 I канала ответствующими входами мажоритарных всех каналов устанавливаются в еди- элементов других каналов деления, ничное состояние, элемент 5 III ка- отличающийся тем, что, нала устанавливается в единичное

40 с целью расширения функциональных состояние, открывая элемент 7 и за- возможностей, в него введены второй крывая элемент 9. На информационный элемент И, элемент сравнения и инвервход регистра 2 III канала через тор, причем инверсные выходы старших элементы 7 и 10 поступает информация разрядов регистров всех каналов соес элемента 4 — единичный уровень ° динены с соответствующими входами

Во II канале элемент 5 устанавлива45 мажоритарных элементов всех каналов, ется в нулевое состояние, открывая кроме того инверсный выход старшего элемент 9 и закрывая элемент 7. На разряда регистра своего канала соенформационный вход регистра 2 ка- динен с первым входом элемента сравала II поступает информация (ну- нения, второй вход которого соединен евон уровень) не с элемента 4, а с с выходом мажоритарного элемента, -триггера 3 через элементы 9 и 10. с первым входом первого элемента Й

По шестому синхроимпульсу II rca- и с информационным входом D-триггера

У ала во II канале элемент 5 устанав- выход - с вторым входом первого элеивается в единичное состояние, а мента И и через инвертор — с первым азряды регистра 2 в состояние

55 входом второго элемента И, второй

0,0,0) — такое же, как и в I u III вход которого соединен с выходом аналах, т ° е, регистры 2 всех кана- D-триггера, выход — с вторым входом ов сфазированы. элемента ИЛИ.