Аналого-цифровой преобразователь в код системы остаточных классов

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в составе устройств ввода аналоговой информации в вычислительные системы, функционирующие в кодах системы остаточных классов (сок). Цель изобретения (О Wff-f - I 12.п-г DO а эо ;о эо ;о

СОЮЗ СОВЕТСНИ1(СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (191 (1И (59 4 H 03 M 1 28

ГО

ПИСАНИЕ ИЗОБРЕТЕНИЯ

СУДАРСТВЕННЫЙ КОМИТЕТ СССР

О ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

А BTOPCHOMV СВИДЕТЕЛЬСТВУ

21) 4115050/24-24

22) 15.05.86

46) 23.01.88. Вне. У 3

72) О.Н.Фоменко, Н.И.Швецов, .А.Краснобаев, А.А.Журавлев, .А.Финько, С.В.Иванов и M.Â.Юмашев

53) 681.325 (088.8) (56) Авторское свидетельство СССР

379980, кл. Н 03 М 1/28, 1973.

Авторское свидетельство СССР

118114 1, кл. Н 03 М 1/28, 10.10.83. (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ В КОД СИСТЕМЫ ОСТАТОЧНЬИ КЛАССОВ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в составе устройств ввода аналоговой информации в вычислительные системы, функционирующие в кодах системы остаточных классов (СОК). Цель изобретения—

1368 расширение функциональных воэможностей за счет дополнительного формирования позиционного кода ядра числа.

Устройство содержит блок 1 определения остатка по наибельшему основанию

СОК, аналого-цифровые преобразователи (АЦП) 2.1-2.п-1, сумматоры 3.1-З.n-t, шифраторы 4.1-4.п, блоки

5.1-5.п-1 коррекции, коммутаторы 6.1-Ь.п- 1, одновибратор 7, регистр 8, аналоговую входную шину 9, шину 10 коррекции, шину 11 управления, выходную шину 13 "Ядро числа" и выходные шины 14.1 — 14.п остатков по соответст989 вующим основаниям СОК. Блок 1 выполнен на первом АЦП 15, цифроаналоговом преобразователе 16, вычитающем устройстве 17 и втором АЦП 18. Каждый блок 5.i коррекции выполнен на сумматоре 19, блоке 20 сравнения и регистре 21. Сущность изобретения заключается в использовании промежуточных результатов преобразователя для формирования позиционного кода ядра числа на выходной шине 13, что существенно расширяет функциональные воэможности устройства- 2 э.п. ф-лы, 1 ил.

Изобретение относится к автоматике и вычислительной технике и может быть использовано в составе устройств ввода аналоговой информации в вычислительные системы, функционирующие в кодах системы остаточных классов (СОК) .

Цель изобретения — расширение функциональных воэможностей за Счет дополнительного формирования позиционного кода ядра числа.

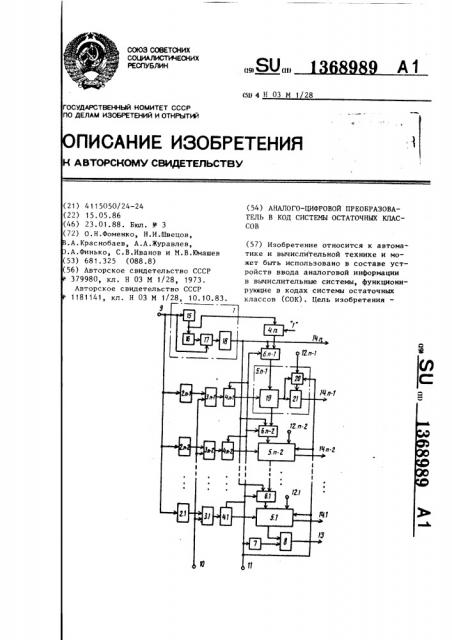

На чертеже приведена функциональная схема аналого-цифрового преобразователя.

Аналого-цифровой преобразователь . содержит блок 1 определения остатка по наибольшему основанию СОК, аналого-цифровые преобразователи 2.1

2.п-1, где п — число оснований СОК, сумматоры 3.1-3.п-1, шифраторы 4.1—

-4.п, блоки 5.1-5.п-1 коррекции, коммутаторы 6.1-6.п-1, одновибратор

7, регистр 8, аналоговую входную шину 9, шину 10 коррекции, шину 11 управления, выходную шину 13 "Ядро числа" и выходные шины 14.1-14.п остатков по соответствующим основаниям СОК» Блок 1 выполнен на первом аналого-цифровой преобразователе (АЦП) 15, цифроаналоговом преобразователе 16, вычитающем устройстве

17, втором ЛЦП 18, выход которого является первым выходом блока 1, вход

АЦП 15 является входом блока 1, а выл<од — вторым выходом блока 1.

Каждый блок 5. i коррекции содержит сумматор 19, блок 20 сравнения и регистр 21, выход которого является первым выходом соответствующего блока 5.i коррекции, первый вход сумматора 19 является первым входом блока 5.i коррекции, второй вход сумматора 19 является третим входом бло/

10 ка 5.i коррекции, выход суммы в позиционном представлении является вторым выходом блока 5.i коррекции, выход суммы по модулю подключен к информационному входу регистра 21 и пер16 вому информационному входу блока 20 сравнения, второй информационный вход которого является вторым входом блока 5.i коррекции, управляющий вход блока 20 сравнения является чет20 вертым входом блока 5.i коррекции, выход блока 20 сравнения подключен к управляющему входу регистра 21.

Работа устройства основана на сле— дук|цих соотношениях.

Аналоговая величина А связана с ее цифровым эквивалентом соотношением

A = N 6. 28, (1)

30 где d — шаг квантования по уровню;

8 — погрешность преобразования, удовлетворяющая 8 О, 5 6

В непозиционном коде СОК число N представляется совокупностью разрядЗБ ных цифр Ы,,

368989 4

В результате сумматоры 19. 1 — 19.п-1 выполняют выражение (3), т. е. на их первых выходах устанавливаются значения разрядных цифр $o!,) (i = 1,п-1) .

Блоки 20.1 — 20.п-1 сравнения контролируют верность получения разрядных цифр согласно условию (4). Если условия (4) не выполняются, т.е. если разрядные цифры получены правильно, то по сигналу с блока 20.i сравнения цифровой код с первого выхода сумматора 19.i считывается в регистр 21.i и выдается на шину 14 выхода устрой15

Если по каким-либо основаниям произошла ошибка, то при подаче сигналов коррекции по шине 10 коррекции на соответствующие сумматоры 3.1

-З.п-1 по сигналам соответствующих блоков 20.i сравнения в регистры 21 заносятся правильные значения разрядных цифр Р<;3 (д = 1,п-!), т е. в выходные шины 14.1 — 14.п поступает откорректированный цифровой код эквивалента.

Для получения значения Rö ядра числа по шине 11 управления подается единичный импульс, причем длительность импульса равна времени, необходимому для образования устойчивого значения кода Кя на входе регистра 8.

На выходах соответствующих шифрато35 ров 6.1 — 6.п образуются произведения (3) Pn — P — 1 (s) ,(N/p,j, с, (N/p,), .3 ! вычетами (о,) от N (i = 1,n) по выбранным вэаимопростым основаниям

$,, p» ..., pn, таким, что 1,а О, ... „ . При этом обеспечивается однозначное представление N в диапазоне P, где P = ) и н n . П ! к

Остаток М „ определяется, как (! /pп P где (И/p„j — целая часть N/ !ь.

Остальные остатки (,, eL

М „, определяются из выражения

<; = /, — (N/P,j P; /

При этом, если

"+i — p n-11 (4) о по основанию О; произошла ошибка. еличина обнаруживаемой ошибки о; полу ения (N/p J (i = 1,п-1) определяетя иэ условия

Наиболее приемлемой дополнительой характеристикой для процессоров, ункционирующих в непоэиционных коах СОК, является позиционная харакеристика R< — ядро числа N, которая пределяется, как и1 „и N

R = ь; --- + с — — +...+с и p ) p p (6) де f<,;t (i = 1,n) — постоянные зараее выбранные коэффициенты.

Устройство работает следующим о6азом.

В исходном состоянии по шине 11 правления поступает "0, тем самым ервый выход блока 1 через коммутато 6.1 — 6.п-1 подключен к третьим одам блоков 5.1 — 5.п-1 коррекции ответственно. Регистры 21.1-21.п-1

8 либо обнулены, либо в них эапины значения (g;) (i = 1,п-1) и R„ едыдущего отсчета.

В процессе преобразования на выдах АИП 2.! — 2.п-1 и на втором ходе блока 1 образуются значения

N/p,),(И/рД,...,(И/Pn) соответствена на первом выходе блока 1 обрается значение ь „, которое пос упа.— на вторые входы сумматора 19.1

19.п-1, на первые входы которых по- упают значения ((N/p;)% (i=1,п-1) . которые в сумматорах 19.1 — 19.п-1 суммируются с значениями кодов, поступающих на их третьи входы.

На втором выходе сумматора 19.n-! образуется сумма

„(!/p„J + с,, (N/p„,)

На втором входе сумматора 19. и-2 образуется сумма (N/pÄ) + „, (N/p„,) + „(N/ ) и т.д. Таким образом на вход регистра 8 поступает значение с>ммы (6) соответствующее RN.

Для того, чтобы в процессе суммирования в регистры 21.1 — 21.п-1 не записались случайные значения кода, на четвертые входы блоков 5.1-5.п-1 коррекции подается логическая 1", которая временно отключает блоки 20 сравнения.

5 136

По окончании действия импульса на шине 11 управления одновибратор 7 выбирает импульс записи значения RN в регистр 8.

Ф о р м у л а и з о б р е т е н и я

1. Аналого-цифровой преобразователь в код системы остаточных классов, содержащий блок вьделения остатка по наибольшему основанию, первый выход которого является выходной шиной остатка по наибольшему основанию, вход является аналоговой входной шиной и объединен с входами п-1 аналого-цифровых преобразователей, где п — число оснований кода системы остаточных классов, выходы которых подключены к первым входам соответствующих и-1 сумматоров, вторые входы которых объединены и являются шиной коррекции, а выходы подключены к информационным входам соответствующих и-1 шифраторов, выходы которых подключены к первым входам соответствующих п-1 блоков коррекции, вторые входы которых являются шинами кодов соответствующих оснований кода системы остаточных классов, выходы являются выходными шинами остатков по с ответствующим основаниям, о т л и ч аю шийся тем, что, с целью расширения функциональных возможностей за счет дополнительного формирования позиционного кода ядра числа, введены одновибратор, регистр, п-й шиф— ратор, и-1 коммутаторов, первые информационные входы которых объединены и подключены к первому выходу блока вьделения остатка по наибольшему основанию, выходы п-1 коммутаторов подключены к третьим входам соответствующих блоков коррекции, управляющие входы объединены с управляющими входами и-1 шифраторов, входом одновибратора, четвертыми входами блоков коррекции и являются шиной управления, вторые информационные входы и-2 коммутаторов подключены к вторым выходам блоков коррекции соответственно с второго по п-1, второй инфор8989 мационный вход и-1 коммутатора подключен к выходу п — шифратора, информационный вход которого подключен

5 к второму выходу блока вьделения остатка на наибольшему основанию, управляющий вход подключен к шине потенциала логической единицы, при этом второй выход первого блока кор10 рекции подключен к информационному входу регистра, управляющий вход которого подключен к выходу одновибратора, а выход является выходной шиной "Ядро числа".

2. Преобразователь по п.1, о тл и ч а ю шийся тем, что блок вьделения остатка по наибольшему основанию выполнен на первом и втором аналого-цифровых преобразователях, 20 цифровоаналоговом преобразователе и вычитающем устройстве, первый вход которого объединен с входом первого аналого-цифрового преобразователя и является входом блока, выход первого аналого-цифрового преобразователя является вторым выходом блока и подключен к входу цифроаналогового преобразователя, выход которого подключен к второму входу вычитающего устройства, выход которого подключен к входу второго аналого-цифрового преобразователя, выход которого является первым выходом блока.

3. Преобразователь по п.1, отличающийся тем, что блок коррекции выполнен на блоке сравнения, регистре, сумматоре, первый. вход которого является первым входом

40 блока, второй вход является третьим входом блока, выход суммы в позиционном коде является вторым выходом блока, выход суммы по моцулю подключен к информационному входу регистра

45 и первому информационному входу блока сравнения, второй информационны& вход которого является вторым входом блока, управляющий вход является четвертым входом блока, выход подклю50 чен к управляющему входу регистра, выход которого является первым выходом блока.

ВНИИПИ Заказ 315!56 Тираж 928 Подписное

Произв.-полигр. пр-тие, r. Ужгород, ул. Проектная, 4