Устройство для измерения изменения фазового сдвига

Иллюстрации

Показать всеРеферат

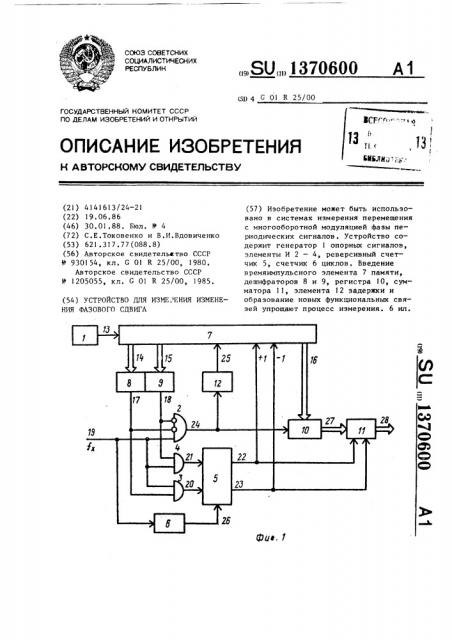

Изобретение может быть использовано в системах измерения перемещения с многооборотной модуляцией фазы периодических сигналов. Устройство содержит генератор 1 опорных сигналов, элементы И 2 - 4, реверсивный счетчик 5, счетчик 6 циклов. Введение времяимпульсного элемента 7 памяти, дешифраторов 8 и 9, регистра 10, сумматора 11, элемента 12 задержки и образование новых функциональных связей упрощают процесс измерения. 6 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51) 4 С 01 R 25/00

13,;", !3

RI%

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4141613/24-21 (22) 19 ° 06.86 (46) 30.01.88. Бюл. Р 4 (72) С.Е.Токовенко и В ° И.Вдовиченко (53) 621,317.77(088.8) (56) Авторское свидетельство СССР !! 930154, кл. G 01 R 25/00, 1980, Авторское свидетельство СССР

N9 1205055, кл. G 01 R 25/00, 1985. (54) УСТРОЙСТВО ДЛЯ ИЗМЕ. ЕНИЯ ИЗМЕНЕНИЯ ФАЗОВОГО СДВИГА

„„SU„„1370600 д1 (57) Изобретение может быть использовано в системах измерения перемещения с многооборотной модуляцией фазы периодических сигналов . Устройство содержит генератор 1 опорных сигналов, элементы И 2 — 4, реверсивный счетчик 5, счетчик 6 циклов, Введение времяимпульсного элемента 7 памяти, дешифраторов 8 и 9, регистра 10, сумматора 11, элемента 12 задержки и образование новых функциональных связей упрощают процесс измерения. 6 ил.

1370600

Изобретение относится к радиоэлектронике и может быть использовано в измерительной технике, в частности в системах измерения перемеще5 ния с многооборотной модуляцией фазы периодических сигналов.

Цель изобретения — упрощение процесса измерения.

На фиг.1 представлена схема устройства для измерения изменения фаэоного сдвига; на фиг.2 — схема, поясняющая работу нремяимпульсного элемента памяти; на фиг.3 и 4 — временные диаграммы его работы; фиг.5— временные диаграммы работы устройства с усреднением результата; на фиг.б диаграммы коррекции состояний времяимпульсного элемента памяти, Устройство (фиг.l) содержит гене- 20 ратор 1 опорных сигналов, элементы

И 2, 3 и 4, реверсивный счетчик 5, счетчик 6 циклов, нремяимпульсный элемент 7 памяти, первый 8 и второй

9 дешифраторы, регистр 10, сумматор 25

11, элемент 12 задержки. Выход 13 генератора 1 соединен с синхронизирующим входом нремяимпульсного элемента

7 памяти, информационные выходы 14, l5 и 16 элемента 7 памяти соединены 30 с входами соответственно первого дешифратора 8, второго дешифратора 9 и регистра 10. Выходы 17 и 18 дешифраторов 8 и 9 соединены с входами первого элемента И 2, третий вход которого соединен с шиной 19 входных сигналов и с первыми входами второго и третьего элементов И 3 и 4, второй вход второго элемента И 3 соединен с выходом 17 первого дешифратора 8, 40 второй вход третьего элемента И 4 соединен с выходом 18 второго дешифратора 9, выходы 20 и 21 второго и третьего элементов И 3 и 4 через ренерсивный счетчик 5 подключены к вхо- 45 дам 22 и 23 сумматора 11 и времяимпульсного элемента 7 памяти, выход первого элемента И 2 соединен с входом 24 регистра 10 и через элемент 12 задержки — с входом 25 сброса время50 импульсного элемента 7 памяти, шина

19 устройства через счетчик 6 циклов соединена с входом 26 сброса реверсивного счетчика, выход регистра 10 подключен к входу 27 сумматора 11 и через него — к выходу 28 устройства.

Принцип действия времяимпульсного элемента 7 памяти в составе предлагаемого устройства поясняется с помощью фиг.2, на которой показаны генератор 29 синхрониэирующих сигналов

Т, работа которого представлена временной диаграммой на фиг.3а, и два делителя 30 и 31 частоты с одинаковым коэффициентом деления К. Выходные сигналы делителей 30 и 31 показаны на фиг.36 в виде сигналов f. u на шинах 32 и 33.

11ри отсутствии воздействия на систему из двух делителей фазовый (временной) сдвиг ч. между выходными сигналами может храниться неограниченно долго, поэтому указанная пара делителей представляет собой многоустойчивую систему, состояния которой различаются временным сдвигом между выходными сигналами делителей часто— ты. Временный сдвиг . может прини1 мать К дискретных значений, отличающихся на Т.

Если делитель 30 частоты предстанляет собой циклический счетчик с последовательной сменой состояний N (см.фиг.Зв) с каждым входным сигналом, то каждому состоянию однозначно соответствует состояние М,. делителя 30 в момент поступления сигналов f„ . Нулевому состоянию системы соответствует синхронное формирование сигналов f; и Г „ и нулевое состояние N счетчика f; в момент формирования f „.

Для установки системы иэ двух делителей частоты в заданное состояние

q. (N.) может быть рекомендовано дна способа ° Первый способ состоит в сбросе счетчика 30 в нулевое состояние сигналом, опережающим сигнал f „ на время q. (фиг.Зв,г), а второй — в установке состояния N. в момент при1 хода сигнала

Запись нулевого состояния системы состоит в сбросе по входу 34 через ключ 35 счетчика-делителя н нулевое состояние сигналом f „ (o eHT t ), после чего сигналы f; и f формируются синхронно. В этом случае можно говорить о запоминании делителем 30 текущего временного положения сигналов f Даже при последующем отсутствии сигналов f „ на выходе делителя

30 формируются сигналы f несущие информацию о временном положении последнего из сигналов 1,, поступивших на вход 34. Сигналы f, в этом случае можно обозначить f „ „,.

1370600

Факт запоминания положения сигналов f„„, путем сброса делителя можно использовать для фиксации иэменения фазового (временного) сдвига

l сигналов f, .

Предположим, что в момент времени (фиг.4в) по входу 34 произведено запоминание положения сигнала f,„,.

Тогда при неизменной фазе (временном положении) следующий сигнал f дол1 жен формироваться в момент времени синхронно с импульсами f„(f,„,).

Если же фаза сигналов f изменяется на величину + л u и сигнал f, поступа- ig ет в момент времени t,, то измененному временному положению, соот— ветствует значение N, состояния счет— чика-делителя 30, При изменении фазы — в сторону запаздывания сигнал Й„поступает в момент времени t, которому соответствует состояние N < делителя 30.

Повторяя описанную процедуру запоминания и накопления N в момент 2 формирования f„ и запоминая текущее временное положение f„ путем сброса делителя, выполняющего функцию времяимпульсного элемента памяти, с каждым сигналом f„ или сигналом f вы- Зб деленным по некоторому признаку, на— пример по номеру, можно осуществлять накопление изменения фазы сигналов

Диапазон измерения изменения фазы определяется объемом накопителя.Дискретность измерения определяется коэффициентом К пересчета делителя 30.

Для этой цели в устройстве (фиг.1) шина !9 через элемент И 2 подключена к входу 24 регистра для запоминания 4п значения кода N. и через элемент 12

1 задержки — к входу 25 сброса элемента 7 памяти для запоминания текущего временного положения сигналов f„ на входе устройства. Числа N накапли- 4

1 ваются сумматором 11, Запоминаемые и накапливаемые числа N, и N представляют собой значение отклонения + q- или — л у и должны учитываться с разными знаками при накоплении. Для этой цели вся совокупность значений N разбивается на две области, например, с помощью старшего счетного двоичного разряда, входящего в состав времяимпульсного элемента 7 памяти. При этом область допустимых значений — dq -Q (фиг.4) обозначена "+" и занимает

1/2 периода следования сигналов f; после формирования сигналов f, ° 06ласть допустимых значений +лlf обоэна— чена знаком "-" и занимает 1/2 периода следования сигналов f, с опережением относительно сигналов f Код

N., в области +" должен восприниматься сумматором 11 в прямом коде и складываться,а код N. области должен восприниматься как дополнительный код до полного объема счетчика элемента 7 памяти и накапливаться в сторону вычитания в соответствии с порядком обработки чисел в дополнИтельном коде, т.е. должно восприниматься как число — (N -N ) (N

9 1 Ф объем счетчика элемента 7 памяти).

В том случае, если все сигналы поступающие на шину 19 устройства, используются для измерения изменения их временного (фазового) положения, показания сумматора 1! изменяются под воздействием всех изменений временного положения сигналов f„, включая девиацию вокруг некоторого среднего положения.

Для исключения влияния девиации фазы на результат измерения в устройство введены дешифраторы состояний N элемента 7 памяти в зоне сигналов f, охватывающей область девиации фазы ° Форма сигналов на выходах дешифраторов 8 и 9 показана на фиг.56,в.. Сигнал f, (фиг.5a) соответствует нулевому рассогласованию между сигналами г . и

Сигналами с выходов 17 и 18 дешифраторов 8 и 9 с помощью элемента

И 2 блокируетгя прохождение сигналов на вход фиксации изменения фазы, если он поступает в промежутки времени, соответствующие сигналам на фиг.56,в.

Если сигнал f„,,поступает на вход устройства в момент времени вне указанных зон (фиг ° 56,в), он проходит на вход регистра 10 для фиксации изменения фазы в соответствии с процедурой, описанной выше (см.фиг.4).Это соответствует быстрой отработке изменения фазы при больших значениях изменений (при большой скорости изменения фазы).

При малой скорости изменения фазы или при неизменной фазе под воздействием девиации в результате воздействия шумов, наводок, помех текущее значение изменений фазы невелико,так что сигнал f попадает в зону, охва13706

5 ченную сигналами на фиг.5б,в. При этом on не проходит на вход регистра через элемент И 2, а подается на вход реверсивного счетчика 5 через элемент

И 3 на вход сложения при попадании в зону фиг.5б или через элемент И 4 на вход вычитания при попадании в зону фиг.5в.

Сигнал на выходах реверсивного счетчика 5 формируется в том случае, 10 если суммарное число импульсов, подсчитанное счетчиком 5 с учетом направления на цикл усреднения, определяе— мыл» счетчиком 6 циклов, превышает объем счетчика 5. 15

Каждым сигналом переполнения счетчика, соответствующим усредненному рассогласованию, производится коррекция временного положения сигналов

f,. на один период следования сигналов Т на входе элемента 7 памяти в сторону опережения при преобладании сигналов Г„, попадающих в зону фиг.5б, или запаздывания при преобладании сигналов f „ в зоне фиг . 5в . Кроме того, указанными сигналами, поступающими на вход сумматора 11, производится добавление (или вычитание) единицы к результату измерения.

Если при девиации фазы в результате счета в равных направлениях за цикл усреднения не превышается объем счетчика 5, состояние схемы остается неизменным, а результат счета сбрасывается сигналом по входу 26 со 35 счетчика 6 циклов для подготовки к новому циклу усреднения.

Процесс измерения отличается простотой (в схеме отсутствует фазовый дискриминатор, требующий жесткое вре- 40 менное формирование сигналов, обеспечение одинакового количества входных и вспомогательных сигналов).

Коррекция временного положения выходных сигналов f; элемента 7 памя- 45 ти по входам 22 и 23 легко реализуется путем добавления или вычитания одного из импульсов на входе элемента

7 памяти согласно диаграмме фиг.6, 00где а — сигналы Т на выходе генератора 1, б — (+1) — сигналы переполнения счетчика 5 при сложении; в — результирующие сигналы. При вычитании сигнал — 1 (фиг.бг) с выхода переполнения счетчика 5 формируется по длительности, равной периоду Т, поэтому при их сложении (фиг.бд) общее число импульсов на один меньше, что и при— водит к смещению формирования сигналов f на один период Т.

Формула изобретения

Устройство для измерения изменения фазового сдвига, содержащее генератор опорных сигналов, три элемента

И, реверсивный счетчик и счетчик циклов, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, в него введены времяимпульсйый элемент памяти, два дешифратора, регистр, сумматор и элемент задержки, причем выход генератора опорных сигналов соединен с синхронизирующим входом времяимпульсного элемента памяти, информационные выходы которого соединены с входами дешифраторов и регистра памяти, выходы дешифраторов соединены с входами первого элемента И, третий вход кОторого соединен с шиной входных сигналов, которая соединена с первыми входами второго и третьего элементов И, второй вход второго элемента И соединен с выходом первого дешифратора, а второй вход третьего элемента И вЂ” с выходом второго дешифратора, выходы второго и третьего элементов И через реверсивный счетчик подключены к входам сумматора и времяимпульсного элемента памяти, выход первого элемента И соединен с входом регистра и через элемент задержки — с входом сброса времяимгульсного элемента памяти, вход устройства через счетчик циклов соединен с входом сброса реверсивного счетчика, выход регистра через сумматор соединен с выходом устройства.

l370600

Фиг. 4

l370600 г

Составитель В ° 111Ó HH

Редактор И,Рыбченко Техред А.Кравчук Корректор

И.Муска

Заказ 416/46 Тираж 772 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб °, д.4/5

Производственно-полиграфическое предприятие,г.ужгор д,у, р о л,11 оектная 4