Резервированное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть применено для резервирования всех типов схем памяти. Целью изобретения является повышение информационной емкости устройства. Устройство содержит основной 1 и резервный матричные накопители , блоки 3, 8 выбора строки. блок 4 выбор а столбца, дополнительный матричный накопитель 5, формирователь сигнала считывания, мультиплексор 7, формирователь 9 сигналов смены адреса, формирователь 10 управляющих сигналов чтения. В устройстве количество одновременно резервируе- - мых ячеек определяется количеством , адресных сигналов, поступающих на вход блока 8. При наличии одного адресного сигнала могут быть зарезервированы 2 ячейки памяти, двух- 4 ячейки, трех-8 ячеек, т.е. 2 ячеек . (где п - число адресных сигналов блока 8) . При этом используется всегр. один резервный столбец. Увеличение количества резервируемых ячеек дает возможность повысить процент выхода годных кристаллов. 2 ил. i (Л

COOS CO8ETCHHX

PECflVSЛИК

ЯЮ О1) (594 G1 С2

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО.ДЕЛАМ ИЗОБРЕТЕНИЙ И OTKPblTWI (21) 3874953/24-24 (22) 22 ° 03.85 (46) 30.01.88. Бюл. У 4 (72) А.Ф. Хоменко, С.В. Высочина, А.Г. Солод и В.П. Сидоренко (53) 681.327(088,8) (56) Электроника, 1984, У 15, с.39.

Электроника, 1980, Ф 20, с, 34, рис. 9. (54) РЕЗЕРВИРОВАННОЕ ЗАПОМИНАКМЦЕЕ

УСТРОЙСТВО (57) Изобретение относится к вычислительной технике и может быть применено для резервирования всех типов схем памяти. Целью изобретения является повышение информационной емкос- ти устройства. Устройство содержит основной 1 и резервный матричные накопители, блоки 3, 8 выбора строки, блок 4 выбора столбца, дополнительный матричный накопитель 5, формирователь сигнала считывания, мультиплексор 7, формирователь 9 сигналов смены адреса, формирователь 10 управляющих сигналов чтения. В устройстве количество одновременно резервируе-— мых ячеек определяется количеством, адресных сигналов, поступающих на вход блока 8. При наличии одного адресного сигнала могут быть зарезервированы 2 ячейки памяти, двух- 4 ячейки, трех-8 ячеек, т.е. 2 " ячеек . (где и — число адресных сигналов блока 8). При этом используется всегр, один резервный столбец. Увеличение количества резервируемых ячеек дает возможность повысить процент выхода годных кристаллов. 2 ил.

1 13

Изобретение относится к вычислительной технике и может быть применено для резервирования всех типов схем памяти.

Целью изобретения является повышение информационной емкости устройства.

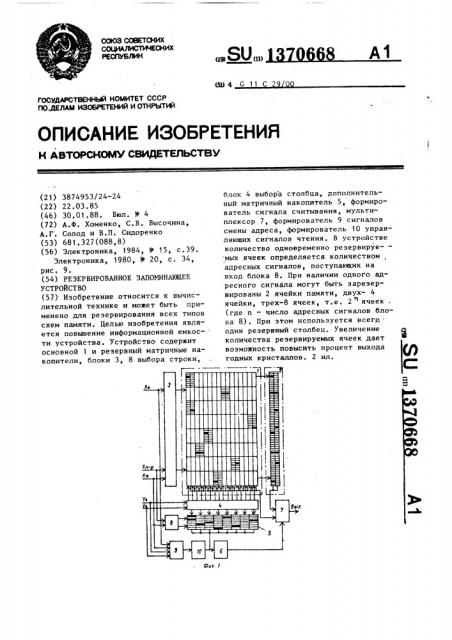

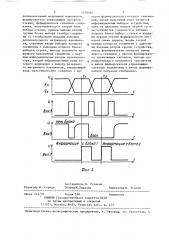

На фиг. 1 представлена схема резервированного запоминающего устройства; на фиг, 2 — временная диаграмма.

Устройство содержит основной 1 и резервный 2 матричные накопители, первый блок 3 выбора строки, блок 4 выбора столбца, дополнительный матричный накопитель 5, формирователь 6 сигналов считывания, мультиплексор 7, второй блок 8 выбора строки, формирователь 9 сигналов смены адреса, формирователь 10 управляющих сигналов чтения.

Устройство работает следующим образом. Резервный накопитель 2 разбит на группы строк. Число групп в столбцЕ равно и и определяется количеством управляющих входов первой группы устройства, поступающих на второй блок 8 выбора строки. Одна строка дополнительного матричного накопителя 5 соответствует одной группе строк в основном матричном накопителе 1 и резервирует эту группу в резервном накопителе 2, Дешифратор столбцевых шин (не показан) опрашивает оба накопителя — основной и резервный. Допустим имеется бракованная ячейка на пересечении третьей строки Х и первого столбца Y в накопителе 1. Производим запись информации о браке в ячейку, находящуюся на пересечении первой строки Х и первого столбца Y и дополнительном накопителе 5. Второй брак находится на пересечении двенадцатой строки и девятого столбца в накопителе 1. Производим запись информации о браке в ячейку, находящуюся на пересечении Z строки Х и девятого столбца Y в дополнительном накопителе 5 и т.д. согласно фиг. 1.

При смене адресного сигнала формирователь сигнала смены адреса вырабатывает сигнал смены адреса, который устанавливает нулевой потенциал на выходе дополнительного накопителя 5 (фиг. 2).

Одновременно блоки выбора строк производят выбор строки в основном и резервном накопителях, а блок выбора

70668 2

5

30 столбцов выбирает столбцы на обоих накопителях.

Если ячейка не была забракована и сигнал о наличии брака не был записан, то на выход дополнительного накопителя 5 (момент времени на фиг. 2) поступит положительный потенциал, который подключит выход устройства к первому информационному входу, т.е. к выходу дополнительного накопителя 5.

Если ячейка была забракована, то в дополнительный накопитель 5 будет записан сигнал брака и на выходе в момент времени будет установлен нулевой потенциал, который через формирователь 6 сигналов считывания подключит выход устройства к второму информационному входу, т.е. к выходу резервного столбца.

Количество одновременно резервируемых ячеек определяется количеством адресных сигналов входов первой группы устройства, поступающих на вход второго блока 8 выбора строки.

При наличии одного адресного сигнала могут быть зареэервированы 2 ячейки памяти, двух — 4 ячейки, трех — 8 ячеек, т.е. 2 ячеек (где n — число адресных сигналов второго блока 8 выбора строк. При этом используется всего адин резервный столбец. Увеличение количества резервируемых ячеек даст возможность повысить процент выхода годных кристаллов.

Формулаизобретения

Резервированное запоминающее устройство, содержащее основной и резервный матричные накопители, первый блок выбора строки, блок выбора . столбца, причем выходы первого блока выбора строки соединены со строчными входами выборки основного и резервного матричных накопителей, входы первого блока выбора строки являются адресными входами первой группы устройства, входы блока выбора столбца являются адресными входами второй группы устройства, выходы первой группы блока выбора столбца соединены со столбцовыми входами выборки основного матричного накопителя, о т л и ч а ю щ е е с я тем, что, с целью повышения информационной емкости устройства, в него введены формирователь сигналов смены адреса, 13;0 бв хп

Чп

Вих

Яых.

9öã. 2

Составитель В. Рудаков

Редакт@р Ю. Середа Техред М. Ходанич

Корректор И. Эрдейи

Заказ 423/50 Тираж 590

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Подписное

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 дополнительный матричный накопитель, формирователь управляющих сигналов чтения, формирователь сигналов считывания, мультиплексор и второй блок

5 выбора строки, причем выходы второй группы блока выбора столбца соединены со столбцовыми входами выборки дополнительного матричного накопителя, строчные входы выборки которого соединены с выходами второго блока-. выборки строки, выходы основного матричного накопителя соединены с первым информационным входом мультиплексора, второй информационный вход которого подключен к выходу резервного матричного накопителя, управляющий вход мультиплексора соединен с выходом формирователя сигналов считывания, выход мультиплексора является информационным выходом устройства, одни из адресных входор первой гр ипы устройства соединены с входами второго блока выбора строки и входами первой группы формирователя сигналов смены адреса, входы второй группы которого соединены с адресными входами второй группы устройства, выход формирователя сигналов смены адреса соединен с входом формирователя управляющих сигналов, выходы дополнительного матричного накопителя и выход формирователя управляющих сигналов подключены к входу формирователя сигналов считывания.