Амплитудный детектор

Иллюстрации

Показать всеРеферат

Изобретение м.б, использовано в аналоговых эл-тах памяти. Цель изобретения - повышение быстродействия и увеличение точности детект ования. Устр-во содержит операц. усилители 1 и 4, диоды 2,3,6, резисторы 5 и 7, запоминающий .конденсатор 8, разрядный ключ 9. Вновь введены диоды 10 и 12 и резистор 11. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ÄÄSUÄÄ 137071 (50 4 Н 03 D 1/00

ВП <

i l3 „g ! ЮЫ. ;:;-i

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ бых

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3948796/24-09 (22) 02.09.85 (46) 30.01.88. Бюп. У 4 (72) И.М. Петренко и И.А. Тосканов (53) 621.376(088.8) (56) Авторское свидетельство СССР

У 1113874, кл. Н 03 D 3/02, 11.10.82.

Алексенко А.Г. и др. Применение прецизионных аналоговых ИС, М.: Радио и связь, 1981, с. 184, рис.7.14б, (54) АМПЛИТУДНЫЙ ДЕТЕКТОР (57) Изобретение м б использовано в аналоговых эл-тах памяти. Цель изобретения — повьппение быстродействия и увеличение точности детектирования. Устр-во содержит операц. Усилители 1 и 4, диоды 2,3,6, резисторы

5 и 7, запоминающий .конденсатор 8, разрядный ключ 9. Вновь введены диоды 10 и 12 и резистор 11. 1 ил.

1370719 аналоговых элементах памяти.

Цель изобретения — повышение быст5 родействия и увеличение точности детектирования.

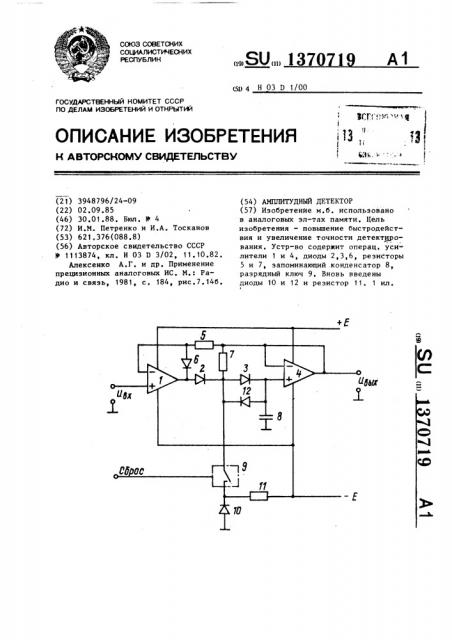

На чертеже изображена принципиальная электрическая схема предлагаемого амплитудного детектора. 10

Амплитудный детектор содержит первый операционный усилитель 1, первый

2 и второй 3 диоды, второй операционный усилитель 4, первый резистор 5, третий диод 6, второй резистор 7, запоминающий конденсатор 8, разрядный ключ 9, первый дополнительный диод 10, первый дополнительный резистор 11 и второй дополнительный диод 12.

Амплитудный детектор работает следующим образом.

В исходном состоянии на запоминающем конденсаторе 8 хранится напряжение, запомненное в предыдущем цик- 25 ле измерения. Непосредственно перед началом измерения на вход сброса амплитудного детектора подается короткий импульс, при этом замыкается разрядный ключ 9 и точка соединения первого 2 и второго 3 диодов подключается к катоду первого дополнительного диода 10. На первом дополнительном диоде 10 и первом дополнительном резисторе 11 реализован парамет35 рический стабилизатор, при этом катод первого дополнительного диода

10 является его выходом, Таким обра" эом образуется цепь разряда для запоминающего конденсатора 8. Разряд 40

1 осуществляется точно до нулевого значения благодаря тому, что выходное напряжение параметрического стабилизатора напряжения равно по абсолютной величине и противоположно по эна- 45 ку напряжению отпирания второго дополнительного диода 12, При появлении входного напряжения положительной полярности переходит в режим положительного насыщения пер- 50 вый операционный усилитель 1, открываются первый 2 и второй 3 диоды и происходит заряд запоминающего конденсатора 8, который длится до тех пор, пока напряжение на запоминающем конденсаторе 8 не превысит входное напряжение. Благодаря включению второго операционного усилителя 4 по схеме неинвертирующего повторителя

Амплитудный детектор, содержащий последовательно соединенные первый операционный усилитель, первый диод, второй диод и второй операционный усилитель, выход которого соединен с инвертирующим входом второго операционного усилителя непосредственно, а с инвертирующим входом первого операционного усилителя — через первый резистор, второй резистор, а также третий диод, второй резистор, запоминающий конденсатор и разрядный ключ, при этом анод третьего диода соединен с инвертирующим входом первого операционного усилителя, Изобретение относится к радиотехнике и может быть использовано в напряжения выходное напряжение ампли-. тудного детектора точно повторяет изменения напряжения на запоминающем конденсаторе 8 и по цепи общей отрицательной обратной связи подается на инвертирующий вход первого операционного усилителя 1 через первый резистор 5.

При превышении напряжения на запоминающем конденсаторе 8 входного напряжения первый операционный усилитель 1 переходит в режим отрицательного насыщения, при этом открывается третий диод 6 и фиксирует выходное напряжение первого операционного усилителя 1 на уровне напряжения отпирания третьего диода 6, что способствует уменьшению времени перехода амплитудного детектора от режима хранения к режиму выборки.

После этого запираются диоды 2 и 3 и амплитудный детектор переходит в режим хранения, причем благодаря тому, что ток, протекающий через второй резистор 7, практически равен нулю, диоды находятся в равновесном состоянии. Известно, что в равновесном состоянии утечка тока через диод определяется термическим потенциалом перехода (p, = 26 мВ), однако в предложенной схеме эти токи направлены встречно и практически полностью компенсируют друг друга.

Таким образом, предлагаемый ампли. тудный детектор позволяет уменьшить погрешность хранения запоминаемого напряжения (увеличить точность детектирования) или при той же погрешности хранения увеличить быстродействие, уменьшив емкость запоминающего конденсатора 8. формула изобретения

Составитель В.Цветков

Техред М. Ходанич

Редактор Е.Копча

Корректор В.Бутяга

Заказ 425/52

Тирах 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ухгород, ул. Проектная, 4

3 13707 а катод — с его выходом, точка сое- динения катода первого диода и анода второго диода через второй резистор подключена к выходу второго операционного усилителя, запоминающий конденсатор включен мелду неинвертирующим входом второго операционного усилителя и общей шиной, неинвертирующий вход первого операционного усилителя является входом, амплитуд- 10 ного детектора, выход второго операционного усилителя — выходом амплитудного детектора, а управляющий вход разрядного ключа — входом сброса амплитудного детектора, о т л и- 15 ч а ю шийся тем, что, с целью повышения быстродействия и увеличе19 4 ния точности детектирования, введены последовательно соединенные первые дополнительные диод и резистор, а также второй дополнительный диод, при этом анод первого дополнительного диода соединен с общей шиной, а катод — с выходом разрядного ключа, анод второго дополнительного диода соединен с неинвертирующим входом второго операционного усилителя, а катод — с входом разрядного ключа и точкой соединения катода первого диода, анода второго диода и первого вывода второго резистора, причем второй вывод дополнительного резистора подключен к выводу источника питания.