Способ измерения сопротивления изоляции электрических сетей постоянного тока и устройство для его осуществления

Иллюстрации

Показать всеРеферат

Изобретение относится к электроизмерительной технике и позволяет П повысить точность измерения сопротивления изоляции. Устройство содержит эквивалентную схему 1 контролируемой сети, запоминающие блоки 5 и 7, индикаторы 8 и 12, коммутатор 14 и блок 15 управления. В устройство введены блоки 4 и 9 согласования и фильтрации соответственно, вычислительный блок 6 и запоминающие блоки 10 и 11. В процессе работы устройства запоминают измеренные значения напряжений и отключают шунтирующий резистор 13. Затем измеряют напряжение контролируемой сети и напряжение на шунтируемом полюсе . По соотношениям, приведенным в тексте описания, определяют соответствующие величины сопротивления изоляции шунтируемого и нешунтируемого полюсов. 2 с.п. ф-лы, 2 ил. (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (11) А1 (51) 4 С 01 R 27/18

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К A ВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4081458/24-21 (22) 04.07.86 (46) 15.02.88. Бюл. Ф 6 (71) Всесоюзный научно-исследовательский институт электроиэмерительных приборов (72) А. Л. Лысенко, В, И. Якименко, Е. А. Беляев и А, В. Шехтман (53) 621.317.7(088,8) (56) Цаценко E.Ä.. Контроль изоляции в сетях до 1000 В.-M,: Энергия, 1972.

Авторское свидетельство СССР

У 840766. кл. G Ol R 27/18, 1981 ° (54) СПОСОБ ИЗМЕРЕНИЯ СОПРОТИВЛЕНИЯ

ИЗОЛЯЦИИ ЭЛЕКТРИЧЕСКИХ СЕТЕЙ ПОСТОЯННОГО ТОКА И УСТРОЙСТВО ДЛЯ ЕГО

ОСУЩЕСТВЛЕНИЯ (57) Изобретение относится к электроизмерительной технике и позволяет повысить точность измерения сопротивления изоляции. Устройство содержит эквивалентную схему 1 контролируемой сети, запоминающие блоки 5 и 7, индикаторы 8 и 12, коммутатор

14 и блок 15 управления. В устройство введены блоки 4 и 9 согласования и фильтрации соответственно, вычислительный блок 6 и запоминающие блоки 10 и 11. В процессе ра" боты устройства запоминают измеренные значения напряжений и отключают шунтирующий резистор 13. Затем измеряют напряжение контролируемой сети и напряжение на шунтируемом полюсе. По соотношениям, приведенным в тексте описания, определяют соответствующие величины сопротивления изоляции шунтируемого и нешунтируемого полюсов, 2 с.п. ф-лы, 2 ил.

1374145

Изобретение относится,к электроиэмерительной технике и может быть использовано для измерения сопротив" ления изоляции электрических сетей постоянного тока, находящихся под

5 напряжением, или объектов, питаемых от таких сетей. Цель изобретения - повышение точности измерения сопротивления изоляции путем исключения влияния изменения контролируемого напряжения сети.

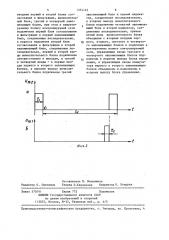

На фиг. 1 представлена блок-схема устройства, реализующего данный спо- 15 соб; на фиг. 2 1,О - диаграммы напряжений на выходе блока управления.

Представленная на фиг. 1 блоксхема содержит упрощенную эквивалентную схему контролируемой сети 20 (объекта) 1, в которой изоляция от- рицательного и положительного полюсов от корпуса представлена соответственно эквивалентными сопротивлени" ями 2 и 3, подключенные к нешунтиру" 25 емому (например, отрицательному) полюсу блок 4 согласования и фильтрации, запоминающий блок 5, вычислительный блок 6, запоминающий блок

7 и индикатор 8, соединенные после- 3р довательно. Подключенные к корпусу блок 9 согласования и фильтрации и соединенный последовательно запоминающий блок 10, выход которого подключен к второму входу вычислительного блока 6, второй выход которого

35 подключен к запоминающему блоку 11 и инидикатору 12, соединенным последовательно. Добавочный резистор 13 (Кд) и коммутатор 14, подключенный одним выводом к корпусу, а другим к коммутатору 14, а управляющий вход коммутатора 14 подключен к второму выходу блока управления 15.

Сущносчь способа измерения сопротивления изоляции электрических се45 тей постоянного тока поясняется следующим.

Сопротивления изоляции полюсов контролируемой сети образуют относительно корпуса делитель напряжения с неизвестными параметрами плеч.

Напряжение на сопротивлении изоляции шунтируемого (например, положительного) полюса при отключенном шунтирующем регисторе R описываетд ся выражением

ER ц 1.

R+R где К, R — сопротивления изоляции положительного (отрицательного полюса).

То же напряжение при подключенном шунтирующем резисторе R и напряже+ А ния сети Е (том же, что Е или другом) равно в Ь;, ERR

R+R й; Л

R R

ЬВ+RК+К

Ф 4 (2) Из уравнений (1) и (2) следует

R A(E U - EU )

m м . (3)

" ЕЦФ UU+% э

Кь(Е П - EU .1

Я « «аю,й с.» (4) из 1ЛР

После сокращения общего множите; ля K(E ) выражения (5) и (6) принимают вид о -

R = R — - —— (7)

"с(" сМ

R = R ---. (8)

A д.(+

Так как в выражениях (7) и (8) отсутствует связанный с изменением сетевого напряжения коэффициент К, то очевидно эти и исходные выражеКоммутации нагрузок сети сопровождаются колебаниями напряжения относительно установившегося значения.

В соответствии со способом при подключенном резисторе R измеряют

А и запоминают не только напряжение на шунтируемом полюсе (U ), но, в отличие от прототипа и известных решений, и напряжение контролируемой сети (Е"). Далее при отключенном резисторе R измеряют и запоминают напряжения U и Е и вычисляют искомые сопротивления изоляции по выражениям (3) и (4).

Указанная последовательность операций позволяет исключить погрешность от изменения величины напряжения сети..Последнее утверждение доказывается следующим образом.

Пусть Е/E =K; U/Å =с ; U /E <. х

Тогда выражения (3) и (4) приводятся к виду

Е Кс Е -КЕ о Ъ

А KE+ot E"-Ô КЕ "ol,"Е

R Е"Кс(Š— КЕ Ы Е

Е»- Д;к

1374145 ния (3) и (4) не зависят ни от величины, ни от закона и скорости изменения напряжения контролируемой сети. Это означает, что иэ результата измерения Е, R исключаются соответствующие дополнительные погрешности любого вида.

Устройство, реализующее данный способ, работает следующим образом.

С выхода блока 15 управления поступают две последовательности импульсов (фиг. 2о,о) с периодом ТК, являющимся периодом коммутации. Длительность с импульсов первой после1 довательности определяет время, в течение которого шунтирующий резистор 13 подключен через коммутатор

14 к полюсу контролируемой сети..

Сигна с контролируемой сети E и 20 с шунтируемого полюса U через блоки 4,9 согласования и фильтрации поступают на вход соответствующих запоминающих блоков 5 и 1Q в которых запоминаются по срезу (момент 25 времени t „ фиг. 2o) импульсы

После отключения шунтирующего резистора 13 на шунтируемом полюсе устанавливается напряжение U (напряжение сети Е при этом может быть

30 равным или не равным его значению Е

Х в момент коммутации) .

М- +

Напряжения Е, Е, U U поступают на входы вычислительного блока 6, осуществляющего преобразования в соответствии с выражениями (5) и (4).

После окончания переходных процессов в вычислительном блоке 6 на

его выходах устанавливаются напряжения, пропорциональные сопротивлениям изоляции 2,3 (R, R+) контролируемой сети 1. В конце очередного цикла измерения на первый выход блока 15 управления поступает импульс по которому осуществляется фиксация выходных напряжений вычисли45 тельного блока 6 в запоминающих блоках 7 и 11 до конца следующего цикла измерения.

Результат измерения R + и R отображается на индикаторах 8 и 12.

Формула изобретения

1. Способ измерения сопротивления изоляции электрических сетей 55 постоянного тока, основанный на измерении напряжения контролируемой сети, шунтировании добавочным резисгде R, R„

s кs значения сопротивлений изоляции шунтиру емого и нешунтируемого полюсов сети соответственно; значение шунтируемого резистора; значения напряжений контролируемой сети и шунтируемого полюса соответственно при под" ключенном шунтирующем резисторе; значения напряжений контролируемой сети и шунтируемого полюса соответственно при от» ключенном шунтирующем

А, Е, Uрезисторе.

2. Устройство для измерения сопротивления изоляции электрических сетей постоянного тока, содержащее шунтирующий резистор, коммутатор, первый и второй запоминающие блоки, блок управления, первый и второй индикаторы, при этом шунтирующий резистор одним выводом соединен последовательно с коммутатором и шунтируемым полюсом контролируемой сети, а другим выводом — к корпусу, о т л и ч а ю щ е е с я тем, что, с целью повьппения точности в него тором сопротивления изоляции, измерении напряжения на шунтирующем резисторе, определении по измеренным значениям величины сопротивления изоляции, отличающийся тем, что с целью повышения точности измерений sa счет исключения погрешности, обусловленной изменениями напряжения контролируемой сети, шунтирующйй резистор подключают к одному полюсу контролируемой сети, запоминают измеренные значения напряжений, отключают шунтирующий резистор, измеряют напряжение контролируемой сети и напряжение на шунти,руемом полюсе, определяют соответствуппцие величины сопротивления изоляции шунтируемого и нешунтируемого полюсов по соотношениям

Ra(E U EU)

ЕУ»- UU

Rp(EU-EU)

N$ ЦЦ %

1374145

f5

Составитель П. Мельников

Редактор О. Спесивых Техред Л.Сердюкова Корректор О. Кундрик

Заказ 570/41 Тираж 772 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д, 4/5

Производственно-полиграфическое предприятие, r, Ужгород, ул, Проектная, 4 введены первый и второй блоки согласования и фильтрации, вычислительный блок, третий и четвертый запоминающие блоки, при этом к нешунтируемому полюсу, контролируемой сети подключены первый блок согласования и фильтрации и первый запоминающий блок, соединенные последовательно, к корпусу подключен второй блок согласования и фильтрации и второй запоминающий блок, соединенные последовательно, первый и второй вхо" ды вычислительного блока подключены соответственно к выходам, а третий . и четвертый входы - к первым входам первого и второго запоминающих блоков, к первому выходу вычислительного блока подключены третий запоминающий блок и первый индикатор, соединенные последовательно, к второму выходу вычислительного блока подключены четвертый запоминающий блок и второй индикатор, соединенные последовательно, причем пятый вход вычислительного блока объединен с вторыми входами первого, второго, третьего и четвертого запоминающих блоков и подключен к . шунтируемому полюсу контролируемой сети, управляющие входы третьего и четвертого запоминающих блоков подключены к первому выходу блока управ. ления, а управляющие входы коммутатора первого и второго запоминающих блоков объединены и,подключены к второму выходу блока управления.