Устройство обработки данных

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для арифметической и логической обработки больших информационных массивов данных. Цель изобретения - повьшение быстродействия. Устройство состоит ;из. блока 1 памяти обмена данными, блока 2 обработки данных, блока 3 памяти данных, счетчиков 4 и 6 горизонтального и вертикального адресов и коммутаторов. Устройство работает следукнцим образом. Вначале производится считьшание исходного массива из блока памяти данных по соответствующим адресам через блок коммутации по соответствующим адресам в блок 1 памяти обмена данными, при этом заполнение памяти обмена данными производится в вертикальном направлении с помощью сдвига сверху вниз. Затем производится считывание массива данных из блока 1 памяти обмена данными, трансляция этих данных через блок 2 обработки данных и запись в блок 3 по соответствующим адресам , при этом в блоке 1 в каждый цикл производится сдвиг данных в горизонтальном направлении. 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

74250 А1 (19I SU(III (5D 4 С 06 F 15/62

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЙАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4102016/24-24 (22) 31 А7.86 (46) 15.02,88. Бюл. М 6 (72) М.Н.Шитьковский, В.К.Соколов и А.А.Косин (53) 681.325(088,8) (56) Авторское свидетельство СССР

У 482749, кл. С 06 Р 15/20, 1972.

Прангишвили и др. Параллельные вычислительные системы с общим управлением. М.: Энергоатомиздат, 1983, с. 101-106. (54) УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ (57) Изобретение относится к вычислительной технике и предназначено для арифметической и логической обработки больших информационных массивов данных ° Цель изобретения — повышение быстродействия. Устройство состоит

:из. блока 1 памяти обмена данными, блока 2 обработки данных, блока 3 памяти данных, счетчиков 4 и 6 горизонтального и вертикального адресов и коммутаторов. Устройство работает следующим образом. Вначале производится считывание исходного массива из блока памяти данных по соответствующим адресам через блок коммута-. ции по -соответствующим адресам в блок 1 памяти обмена данными, при этом заполнение памяти обмена данными производится в вертикальном направлении с помощью сдвига сверху вниз. Затем производится считывание массива данных из блока 1 памяти обмена данными, трансляция этих- данных а через блок 2 обработки данных и запись в блок 3 по соответствующим адресам, при этом в блоке 1 в каждый цикл производится сдвиг данных в горизонтальном направлении. 2 ил.

1374250

Изобретение относится к вычислительной технике и предназначено для арифметической и логической обработки больших информационных массивов данных, использования в составе параллельного процессора, предназначенного для цифровой обработки изображений и-распоЗнавания образов.

Цель изобретения — повышение быстродействия.

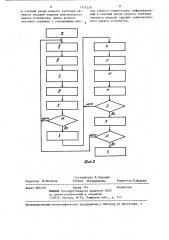

На фиг. 1 представлена структурная схема устройства обработки и хранения данных; на фиг.2 — алгоритм работы устройства. 15

Устройство содержит блок 1 памяти обмена данными, блок 2 обработки данных, блок 3 памяти данных, счет-: чик 4, коммутатор 5, счетчик 6 и коммутатор .7. . 20

Блок 1 является ортогональной памятью размерностью P íà М, выполненной на регистрах сдвига. Возможны сдвиги информации в блоке 1 влево, вправо, вверх и вниз. Блок 2 содержит P одноразрядных арифметико-логических узлов. Блок 3 представляет собой Р;разрядную оперативную память, а коммутатор 5 -коммутацию Р/M направлений на одно. направление. Раэ- ЗО рядность каждого направления M.

Управление блоками 1 и 2 и ком- . мутатором 7 осуществляется блоком управления (не показан).

Работу предлагаемого устройства 35 рассмотрим в соответствии с алгоритмом (фиг.2), В йачале работы необходимо установить начальный горизонтальный адрес

А и начальный вертикальный адрес 4п г

А4 в соответствующих счетчиках 4 и б

S для осуществления чтения слова из блока 3 памяти данных. Причем по адресу А из блока 3 памяти данных выбирается соответствующий вертикаль-. ный столбец, а по адресу А коммучт татор 5 выбирает слово разрядностью

N. Выбранное таким образом слово последовательно записывается в блок 1 памяти обмена данными через коммуI татор 7.Затем производят увеличение

А горизонтального адреса +1 и производят анализ конца считывания по гори I зонтальному адресу. Если считывание не окончено, производится повторение цикла, состоящего из блоков

- б. ..ж алгоритма, изображенного на фиг.2. После окончания записи слов из блока 3 памяти данных в блок 1 памяти обмена данными начинается фаза записи информации с разрядностью

P из блока 1 в блок 3 по горизонтальному адресу А, . При этом блок 1 производит последовательное продвижение информации с разрядностью P в горизонтальном направлении, блок 2— трансляцию. этой информации, а блок 3— запись (фиг.2, блоки с, к,...,0 алгоритма). После окончания фазы записи в блок 3 памяти данных происходит установка нового значения вертикального адреса в счетчик б, начального горизонтального адреса А, т в блоки П, Р алгоритма (фиг.2); При этом в блоке P алгоритма производит ся анализ конца работы по повороту всего заданного массива информации.

Если нет окончания, то происходит повторение циклов чтения информации разрядностью М из блока 3 в блок 1 . Так происходит повторение циклов записи и чтения в блоке 3 памяти данных до полного поворота заданного массива информации. г

Формула изобретения

Устройство обработки данных, содержащее блок памяти обмена данными, блок обработки данных, блок памяти данных, первый выход блока памяти обмена данными соединен с входом первого операнда блока обработки данных, выход которого соединен с информационным входом блока памяти данных, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены два коммутатора и два счетчика, причем выход блока памяти данных соединен с информационным входом первого коммутатора и входом второго операнда блока обработки данных, выход первого коммутатора соединен с первым информационным ьходом второго коммутатора, второй выход блока памяти обмена данными соединеч с вторым информационным входом второго коммутатора, третий информационный вход второго коммутатора является информационным входом устройства, выход второго коммутатора яв-яется выходом устройства и соединен с информационным входом блока памяти обработки данных, выход первого счетчика соединен с адресным входом блока памяти данных, информационный

Составитель В.Бородин

Техред Л.Сердюкова

Корректор М.Шароши

Редактор М.Петрова

Тираж 704

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 604/46

Подписное

Производственно-полиграфическое предприятие,г.ужгород,ул.Проектная, 4 э 1374250

4 и счетный входы первого счетчика яв- дом первого коммутатора, информационляются входами задания вертикального ный и счетный входы второго счетчика адреса устройства, выход второго являются входами задания горизонтальсчетчика соединен с управляющим вхо- ного адреса устройства.