Цифровой синтезатор частоты

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике . Цель изобретения - повьшение спектральной чистоты выходного сигнала. Цифровой синтезатор частоты содержит блок 1 установки частоты , накопитель 2, блок 3 синхронизации , регистр 4 памяти, преобразователь 5 кодов, перемножитель 6 кодов, сумматор 7, блоки памяти 8 и 9, ЦАП 11, фильтр нижних частот 12. Для достижения цели в устройство введен блок коррекции (БК) 10, устраняющий возможные искажения выходного сигнала за счет поддержания единичного кода на своем выходе по сигналу переполнения сумматора 7. В результатов использования БК 10 наибольшее значение макс, погрешности будет на середине линейного участка. Т.о., за счет введения БК 10 (при одних и тех же аппаратурньпс затратах по остальным блокам) точность цифрового вычисления синусоиды удваивается и соответственно повьшается спектральная чистота выходного сигнала. 2 ил. с S (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (50 4 Н 03 В 19/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (61) 1.190457 (21) 41 20620/09 (22) 17.09.86 (46) 15.02.88.Бюл. Р 6 (71) Таганрогский радиотехнический институт им.В.Д.Калмыкова (72) В.Ю.Капустин, В.С.Григорьев и П.А.Гадяцкий (53) 621.373.42(088.8) (56) Авторское свидетельство СССР

N - 1190457, кл. Н 03 В 19/00, 1983. (54) ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТЫ (57) Изобретение относится к радиотехнике. Цель изобретения — повышение спектральной чистоты выходного сигнала. Цифровой синтезатор частоты содержит блок 1 установки частоты, накопитель 2, блок 3 синхрониза,SU„„1374398 А 2 ции, регистр 4 памяти, преобразователь 5 кодов, перемножитель 6 кодов, сумматор 7, блоки памяти 8 и 9, ЦАП 11, фильтр нижних частот 12. Для достижения цели в.устройство введен блок коррекции (БК) 10, устраняющий возможные искажения выходного сигнала за счет поддержания единичного кода на своем выходе по сигналу переполнения сумматора 7. В результате использования БК 10 наибольшее значение макс. погрешности будет на середине линейного участка. Т.о., за счет введения БК 10 (при одних и тех же аппаратурных затратах по остальным блокам) точность цифрового вычисления синусоиды удваивается и соответственно повышается спектральная чистота выходного сигнала. 2 ил.

1374398

Изобретение относится к радиотехнике и может быть использовано для получения сетки частот в системах связи, гидролокации, в устройствах вычислительной и измерительной техники.

Цель изобретения — повышение спектральной чистоты выходного сигнала.

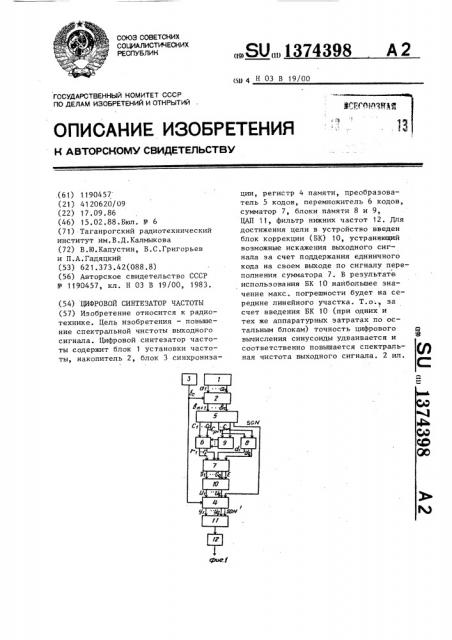

На фиг.1 представлена структурная 10 электрическая схема цифрового синхронизатора частот, на фиг.2 — аппроксимация синусоиды, (первый квадрант) обычным способом — кусочно-линейная кривая 2.1 и по средним точкам — ку- 15 сочно-линейная кривая 2.2.

Цифровой синтезатор частоты содержит блок 1 установки частоты, накопитель 2, блок 3 синхронизации, регистр 4 памяти, преобразователь 5 ко- 2р дов, перемножитель 6 кодов, сумматор 7,. первый 8 и второй 9 блоки памяти, блок 10 коррекции, цифроаналоговый преобразователь (ЦАП) 11 и фильтр 12 нижних частот (ФНЧ) . 25

Цифровой синтезатор частот работает оледующим образом..

При помощи блока 1 установки частоты в двоичном коде устанавливается число а, определяющее значение выход-30 ной частоты цифрового синтезатора частот. При работе на выходе накопитсля 2 результирующие значения чисел обновляются с частотой синхронизации

fc, задаваемой блоком 3 синхронизации. Код числа В с выходов накопителя 2 поступает на входы преобразователя 5 кодов, который в зависимости от четности или нечетности числа переполнений накопителя 2 формирует пря- 40 мой или дополнительный коды числа В.

Младшие из выходных разрядов преP образователя 5 кодов образуют 2 слов (по наибольшему возможному числу сту-45 пенчатых приращений на каждый линейный участок аппроксимируемой синусоидальной функции) . В результате в произвольный тактовый момент частоты fc на выходе преобразователя 5 кодов формируется i-й адрес обращения к блокам 8 и 9 памяти и множитель j, поступающий на вторые входы перемножителя 6 кодов (i=0,1,...,2 -1;

3=0,1,...,2 -1) .

В первый блок 8 памяти занесены

2 цифровых значений А ;= А, +0,5 ai, соответствующих равномерно расположенным на дуге единичной окружности

IT i аргументам х,= ---;, в пределах одного квадранта (где A . — sin x

0,5 di — поправка, связанная с аппроксимацией синусоиды линейными участками со знакопеременной погрешностью, т.е. аппроксимация по средним точкам — кривая 2,2).

Значение oi находят из треугольника AOD (фиг.2): д, i = Е D ° sin oI (i+1), OA где ED=OD-DE, OD. =

cos с(2

OA откуда ED = . — — — — — OE.

cos d/2

Для единичной окружности.

1-соs а(/2

ED

cos 8/2 тогда

i-соэ o(/2

Й=ЕП sin Ы (i+i) = — — — — — — sin(i+1) . сов

В результате получают величину

1-cos o|/2

А, = (1+0,5 — — —.— ) sin a" (i+1) cos ot/2

1-cos о(/2

А = (1+О 5 — — — — — ) A....

cos о(/2

Во второй блок 9 памяти занесены приращения синусоидальной функции от каждого линейного участка ее кусочно-линейной аппроксимации

В.= А — А.

i+1 откуда

1-cos a /2, B,=(1+0,5 -- — — — — - ) (sina

cos a(/2 (i+1) -sino(-i) или

1-со s o(/2

В. = (1+05 — — — — — ) В

cos ct/2

Таким образом, величины А . и В . предлагаемого устройства оказывают1-cos Ы/2 ся в (1+О, 5 — — — — --) большими,чем

cos a/3 величины А, и В,, используемые в прототипе.

1З74ЗЧ8

Значения A.è В. одновременно выбираются из блоков 8 и 9 памяти адресными выходами старших разрядов преобразователя 5 кодов и поступают соответственно на первые входы перемножителя 6 кодов и вторые входы сумматора 7.

Величина В., умноженная на двоичную кодовую комбинацию ) /2 числа j 10 образующуюся на выходах младших разрядов преобразователя 5 кодов, дает положительную поправку к величиI не А. грубого угла х; при определении модуля функции A .. Для любОГО 15 текущего аргумента

А ° .=А. + 2 .j В,, 1) з

1 где сомножитель 2 — масштабный коэф- 20

-P фициент, учитывающий, что операции умножения и сложения выполняются над двоичными числами меньше единицы.

В результате на выходе сумматора 7 формируется последовательность дис- 25 кретных цифровых значений амплитуды линейной аппроксимации синусоидальной функции по средним точкам, которая поступает на информационный вход блока 10 коррекции.

Аппроксимация синусоиды по средним точкам влечет за собой появление значений А .. 1 на линейных участ1) ках, примыкающих к углам 2n Ti+ Х/2, поэтому при переполнении сумматора 7 сигнал переноса поступает на управляющий вход блока 10 коррекции и устанавливает все его выходные разряды в единичное состояние. В обычном алгоритмическом режиме блок 10 40 коррекции пропускает двоичный код A с выхода сумматора 7 на вход регистра 4 памяти без изменения.

На выходе SGN преобразователя 5 кодов состояние изменяется на каждом 45 б втором импульсе переполнения накопителя 2 в результате на выходе SGN формируется импульсная последовательность, соответствующая изменениям знака выходного сигнала. В ре50 гистре 4 памяти вычисленные значения

I модуля амплитуды А; и знака амплиту" ды хранятся в течение времени 1/fc, после чего сменяются новыми. Код синусоиды с выхода регистра 4 памяти поступает на разрядные входы ЦАП 11, причем сигнал с выхода SGN регистра 4 памяти поступает на знаковый вход ЦАП 11, В результате на выходе последнего формируется синусоидальный сигнал, который через ФНЧ 12 поступает на выход цифрового синтезатора частоты.

Частота выходного сигнала и

f = afc/4N где N=2 — емкость наВйм

У копителя 2, которая численно совпадает с максимальным числом дискретных точек формирования синусоидального сигнала в пределах одного квадранта. Следовательно, если a=i то происходит синтез минимальной выходной частоты, равной fc/4N. Это же выражение определяет и шаг дискретности частоты на выходе синтезатора частоты. Часть младших k разрядов накопителя 2 можно не использовать, поэтому ш+р=п-k.

Наибольшее значение максимальной погрешности отклонения каждого линейного участка (из 2 возможных) от синусоиды / 4 max/ в пределах квадранта находится в точке x = it/2.

0 5(1-cos о(/2) соя с1/2

0 5(1-cos T1/2 )

4/шах б

cos 7/1/2

Значение погрешности /11max/ зависит только от числа линейных участков на четверть периода, например, при ш=5 (32 линейных участка) /dmax/=

=0 001506, что соответствует двенадцати точным разрядам вычисления значений синусоиды.

Вычисленное сумматором 7 значение синусоиды в интервале аргументов

111+Э

Г/2 — 7i /2 (Хс й/2 первого квадранта превышает не только истинное, но и единичное значение на величину

S /ämàx /, двоичный код которой в результате переполнения сумматора 7 при отсутствии блока 10 коррекции мог бы попасть на ЦАП 11 через регистр 4 памяти, что привело бы к неалгоритмическому спаду синусоидальной функции практически с единицы до нуля. Блок 10 коррекции устраняет эти возможные искажения выходного сигнала эа счет поддержания единичного кода на своем выходе по сигналу переполнения сумматора 7.

В результате использования блока

10 коррекции наибольшее значение максимальной погрешностиД„ имеется на середине линейного участка при х, = т(/2 и определяется выражением

1374398

1 Г 1 д max = — — cos — —,— (1-cos — — — )

2 п 2 " б

Составитель Л.Ананьева

Редактор Л.Пчолинская Техред М. Ходанич Корректор А.Тяско

Заказ 618/54 Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.ужгород,ул.Проектная, 4

Таким образом в предлагаемом цифУ

5 ровом синтезаторе частот за счет введения блока коррекции (при одних и тех же аппаратурных затратах по ос-: тальным блокам) точность цифрового вычисления синусоиды удваивается и соответственно повышается спектральная чистота выходного сигнала.

Формула из о бр етения

Цифровой синтезатор частоты по. авт.св. У 1190457, о т л и ч а юшийся тем, что, с целью повышения спектральной чистоты выходного сигнала, выходы сумматора соединены с соответствующими входами регистра памяти через введенный блок коррекции, управляющий вход которого соединен с выходом переполнения сумматора.