Формирователь импульсов

Иллюстрации

Показать всеРеферат

Изобретение может быть исполь-. зовано .в интегральных схемах динамического типа на МДП-транзисторах. Целью изобретения является повьпнение быстродействия и расширение области применения. Устройство содержит шину 1 питания, общую шину 2; входы: включения .3, перезаряда 4, удержания 5, бутстрепный 6, подготовки 7, прямой адресный 8, инверсный адресный 9; выходные шины 10 и 11; транзисторы; выключения 12 и 13, включения 14 и 15, проходные 16 и 17, удержания 18, ключевые 19 и 20, входные 21 и 22, перезаряда 23 и 24, подготовки 25,. бутстрепный 26; конденсаторы: управляющие 27 и 28, выходной 29. Расширение области применения достигнуто за счет введения второй выходной шины 11. Это позволяет использовать формирователь без дополнительной селекции сигналов при необходимости получения сигналов по двум выходным шинам, что приводит также к повьш1ению быстродействия. 2 ил. с сл со 4 4 05 аг/

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51) 4 И 03 Х 5/13

ЬМЬЛ!" -

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3851366/24-21 (22) 31.01.85 (46) 15.02.88. Бюл. Х- 6 (72) В.П. Беспалов, А.И. Макаров, В.Д. Мещанов и И.А. Телицын (53) 621.318.5(088.8) (56) Заявка Франции !!.- 2432799, кл. Н 03 Х 17/60, 1980 (54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ (57) Изобретение может быть исполь-. зовано .в интегральных схемах динамического типа на 1ЩП-транзисторах.

Целью изобретения является повышение быстродействия и расширение области применения. Устройство содержит шину 1 питания, общую шину 2; входы: включения 3, перезаряда 4, удержа„„su„„> 374416 А1 ния 5, бутстрепный 6, подготовки 7, прямой адресный 8, инверсный адресный 9; выходные шины 10 и 11; транзисторы: выключения 12 и 13, включения 14 и 15, проходные i6 и 17, удержания 18, ключевые 19 и 20, входные 21 и 22, перезаряда 23 и 24, подготовки 25, бутстрепный 26; конденсаторы: управляющие 27 и 28, выходной 29. Расширение области применения достигнуто за счет введения второй выходной шины 11. Это позволяет использовать формирователь без дополнительной селекции сигналов при необходимости получения сигналов по двум выходным шинам, что приводит также к повышению быстродействия.

2 ил.

1 137441

Изобретение относится к имп льсной технике и может быть использовано в интегральных схемах динамического типа на ЩП-транзисторах.

Цель изобретения — повышение быстродействия и расширение области применения.

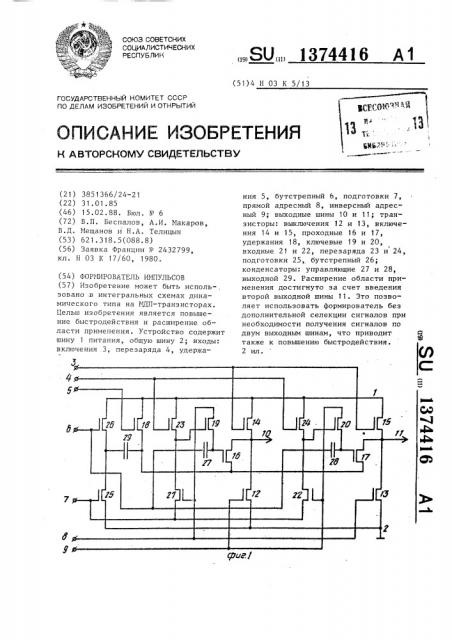

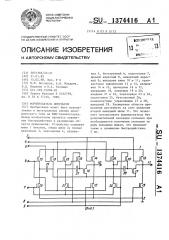

На фиг. 1 представлена схема устройства; на фиг. 2 — временные ди- 10 аграммы сигналов на входах и выходных шинах устройства.

Формирователь импульсов содержит шину питания 1, общую шину 2, входы включения 3, предзаряда 4, удержания 5, бутстрепный 6, подготовки 7, прямой адресный 8, инверсный адресный 9, первую 10 и вторую 11 выходные шины, транзисторы выключения первый 12 и второй 13, включения первый 20

14 и второй 15, проходные первый 16 и второй 17, удержания 18, ключевые первый 19 и второй 20, входные первый 21 и второй 22, предзаряда первый .23 и второй 24, подготовки 25, 25 бутстрепный 26, конденсаторы управляющие первый 27 и второй 29, выходной 29.

Сток первого транзистора выключения 12 соединен с первой выходной ши- 30 ной 10, истоком первого транзистора включения 14 и истоком первого проходного транзистора 16, сток которого соединен с первым выводом выходного конденсатора 29 ч истоком транзистора 35 удержания 18, а затвор первого проходного транзистора 16 соединен с первым выводом первого управляющего конденсатора 27 и истоком первого ключевого транзистора 19, затвор ко- 40 торого соединен с стоком первого входного транзистора 21 и истоком первого транзистора предзаряда 23, сток второго транзистора выключения

13 соединен с второй выходной шиной

11, истоком второго транзистора включения 15 и истоком второго проходного транзистора 17, сток которого соединен с первым выводом выходного конденсатора 29, а затвор второго проходного транзистора 17 соединен с первым выводом второго управляющего конденсатора 28 и истоком второго ключевого транзистора 20, затвор которого соединен с стоком второго входного транзистора 22 и истоком второго транзистора предзаряда 24, вторые выводы первого 27 и второго 28 управляющих конденсаторов соединены

6 г с бутстрепным входом 6 и затвором бутстрепного транзистора 26, исток которого соединен с вторым выводом выходного конденсатора 29 и стоком транзистора подготовки 25, затвор которого является входом подготовки

7 и соединен с истоками первого 21 и второго 22 входных транзисторов, затворы транзисторов включения 14 и 15 и предзаряда 23 и 24 подключены к входам включения 3 и предзаряда 4 соответственно, затвор транзистора удержания 18 является входом удержания 5, затворы первого входного транзистора 21 и,второго транзистора выключения 13 соединены с стоком первого ключевого транзистора 19 и образуют прямой адресный вход 8, затворы второго входного транзистора 22 и первого транзистора выключения 12 соединены с стоком второго ключевого транзистора 20 и образуют инверсный адресный вход 9, стоки первого 14 и второro 15 транзисторов включения, первого 23 и второго 24 транзисторов предзаряда, транзистора удержания 18 и бутстрепного транзистора 26 соединены с шиной питания 1, а истоки первого 12 и второго 13 транзисторов выключения и транзистора подготовки

25 подключены к общей шине 2.

Формирователь импульсов работает следующим образом.

В исходном состоянии на входах предзаряда 4, удержания 5, подготовки 7 установлен высокий уровень напряжения ЕП, равный напряжению на шине питания 1. На входе включения

3 установлен бутстрепный уровень напряжения И Ец+И, где И -- пороговое напряжение. На остальных входах формирователя установлен низкий уровень напряжения. Выходные шины первая 10 и вторая 11 заряжены до напряжения Е„. Через открытые первый 19 и второй 20 ключевые транзисторы на затворах первого 16 и второго 17 проходных транзисторов установлен низкий уровень напряжения, проходные транзисторы 16 и 17 закрыты, выходной конденсатор 29 изолирован от выходных шин 10 и 11 и через открытый транзистор удержания 18 заряжен до напряжения Г„.

В момент времени t, (фиг. 2) на входах предзаряда 4, удержания 5 и включения 3 устанавливается низкий уровень напряжения, при этом транзис1374416 торы предзаряда 23 и 24, удержания

18, включения 14 и 15 закрываются.

В момент времени t, (фиг. 2) на адресные входы прямой 8 или инверсный 9 подается сигнал высокого уровня. Пусть высокий уровень напряжения подан на прямой адресный вход 8. При этом, через открытый первый ключевой транзистор 19 первый вывод пер0 вого управляющего конденсатора 27 за— ряжается до высокого уровня напряжения Е Второй транзистор выклю-rf чения 13 переходит в открытое состояние и на второй выходной шине 11 устанавливается низкий уровень. В момент времени t на входе 6 устанавливается уровень напряжения Иб, а на входе подготовки 7 — низкий уровень напряжения. Через первый управляющий конденсатор 27 сигнал U переда— ется на затвор первого проходного транзистора 16, который открывается.

Через открытый бутстрепный транзистор 26 на втором выводе выходного конденсатора 29 устанавливается высокий уровень напряжения EÄ, при этом на первом выводе устанавливается уровень напряжения U E +U который через открытый первый проходной транзистора 16 передается на первую выходную шину 10. В то же время на истоках входных транзисторов 21 и

22 устанавливается низкий уровень напряжения, при этом первый входной транзистор 21 открывается и на затво-35 ре первого ключевого транзистора 19 устанавливается низкий уровень напря жения, он закрывается. Это предотвращает утечку заряда с первого вы40 вода первого управляющего конденсатора. Подключение истоков входных транзисторов 21 и 22 к входу подготовки 7 обеспечивает синхронизацию открывания входного транзи то- 45 ра 21 с закрыванием транзистора подготовки 25, т.е. с подачей высокого уровня напряжения на второй вывод выходного конденсатора 29.

В момент времени э (фиг. 2) на

50 входах прямом адресном 8 и бутстрепном 6 устанавливается низкий уровень напряжения, при этом первый входной

21 и бутстрепный 26 транзисторы закрываются. В момент времени t на входах предзаряда 4, удержания 5 и подготовки 7 устанавливаются высокие уровни напряжения Е„, а на вход включения 3 подается бутстрепный уровень И .

При этом, первый 23 и второй 24 транзисторы предзаряда, первый 14 и второй 15 транзисторы включения, транзистор удержания 18 и транзистор подготовки 25 открываются. На выходных шинах 10 и 11 устанавливается высокий уровень напряжения E„. Формирователь переводится в исходное состояние.

Расширение области применения предлагаемого формирователя импульсов по сравнению с известным достигнуто за счет введения второй выходной шины, что позволяет использовать формирователь беэ дополнительной селекции сигналов в случае необходимости получения сигналов по двум выходным шинам.

Предложенный формирователь импульсов предпочтительнее испольэовать в качестве формирователя сигнала записи, поскольку выходной сигнал высокого уровня может быть получен либо на первой 10, либо на второй 11 выходных шинах, при этом на противоположной выходной шине устанавливается низкий уровень напряжения.

Использование известного в качестве формирователя сигнала записи без селекции сигналов принципиально не— возможно. Подключение селектора сигналов уменьшает быстродействие иэза увеличения постоянной времени цепи нагрузки. В предложенном формирователе импульсов при использовании его в качестве формирователя сигнала записи селекция сигналов отсутствует что приводит к повышению быстродействия

Формула изобретения

Формирователь импульсов, содержащий первый транзистор выключения, сток которого соединен с первой выходной шиной, с истоками первого транзистора включения и первого проходного транзистора, сток которого подключен к истоку транзистора удержания и первому выводу выходного конденсатора, затвор первого проходного транзистора соединен с первым выводом первого управляющего конденсатора и истоком первого ключевого транзистора, транзистор подготовки, сток которого соединен с истоком бутстреп1374416

Фиг 2

Составитель В. Пятецкий

Редактор И. Сегляник Техред A.Кравчук Корректор M. Пожо

Заказ 619 55 Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 ного транзистора. стоки первого транзистора включения, транзистора удержания и будстрепного транзистора подключены к шине питания, истоки первого транзистора выключения

5 и транзистора подготовки подключены к общей шине, затворы первого транзистора включения и транзистора подготовки образуют соответственно входы 0 включения и подготовки, о т л и ч а ю шийся тем, что, с целью повышения быстродействия и расширения области применения, в него введены вторая выходная шина, второй транзис15 тор включения, второй транзистор выключения, второй ключевой транзистор, второй проходной транзистор, первый и второй транзисторы предзаряда, первый и второй входные транзисторы д1 и второй управляющий конденсатор, причем сток второго транзистора выключения соединен с второй выходной шиной, с истоками второго транзистора включения и второго проходного транзистора, сток которого подключен к первому выводу выходного конденсатора, затвор второго проходного транзистора соединен с первым выводом второго управляющего конденсатора и истоком второго ключевого транзистора, стоки первого и второго входных транзисторов соединены с истоками первого и второго транзисторов предзаряда и затворами первого и второго ключевых транзисторов выключения и сток первого ключевого транзистора подключены к прямому адресному входу, а затворы второго входного транзистора, первого транзистора выключения и сток второго ключевого транзистора подключены к инверсному адресному входу, истоки входных транзисторов и затвор транзистора подготовки подключены к входу заготовки, вторые выводы управляющих конденсаторов и затвор бутстрепного транзистора подключены к бутстрепному входу, исток бутстрепного транзистора соединен с вторым выводом выходного конденсатора, затвор транзистора удержания является входом удержания, затворы транзисторов предзаряда подключены к входу предзаряда, а затвор второго транзистора включения подключен к входу включения, стоки второго транзистора включения, первого и второго транзисторов предзаряда соединены с шиной питания, а исток второго транзистора выключения соединен с общей шиной.