Устройство для программируемой задержки информации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычисли- .тельной технике и может быть использовано в цифровых вычислительных машинах . Цель изобретения - повышение быстродействия устройства. Устройство содержит первьй 1 и второй 2 блоки памяти, счетчик 3, выходной 4 и входной 8 регистры данных, блок 6 синхронизации, регистр 10 кода задержки , элемент 11 задержки и элемент ИЛИ 14, При работе устройства происходит одновременная запись информации с входного регистра в один из блоков памяти, и чтение из другого блока памяти.с записью в выходной регистр по одному и тому же адресу. 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5i) 4 6 06 F 1/04

ВО":,Г. :

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

CO

Cb

4Р 3 (21) 4109146/24-24 (22) 15.08.86 (46) 23.02.88, Бюл. 9 7 (72) А.Н.Мельник, Б.В.Карпухин и E.Е.Береза (53) 681.327(088.8) (56) Авторское свидетельство СССР

М 556495, кл. С 11 С 11/00, 1971.

Авторское свидетельство СССР

Р 1193653, кл. G 06 Р 1/04, 1984. (54) УСТРОЙСТВО ДЛЯ ПРОГРАММИРУЕМОЙ

ЗАДЕРЖКИ ИНФОРИАЦИИ (57) Изобретение относится к вычислительной технике и может быть испольÄÄSUÄÄ 1376074 А 1 зована в цифровых вычислительных машинах. Цель изобретения — повышение быстродействия устройства. Устройство содержит первый 1 и второй 2 блоки памяти, счетчик 3, выходной 4 и входной 8 регистры данных, блок 6 синхронизации, регистр 10 кода задержки, элемент 11 задержки и элемент ИЛИ 14. При работе устройства происходит одновременная запись информации с входного регистра в один из блоков памяти и чтение из другого блока памяти.с записью в выходной регистр по одному и тому же адресу.

2 ил.

1376074

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах, Цель изобретения — повышение быстродействия устройства.

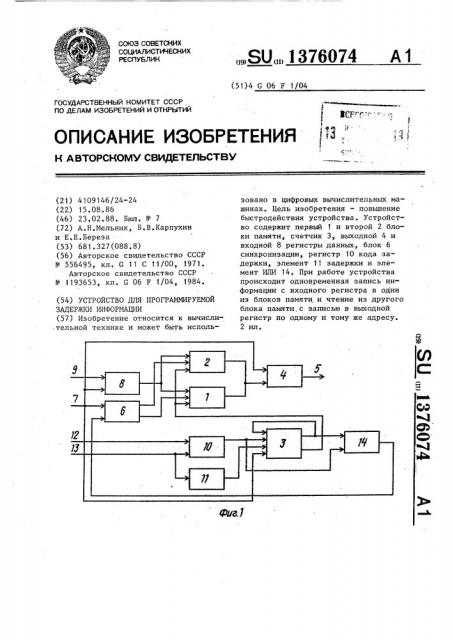

На фиг. 1 изображена структурная схема устройства для программируемой задержки информации; на фиг. 2 — диа- 10 граммы, поясняющие его работу.

Устройство (фиг. 1) содержит первый 1 и второй 2 блоки памяти, счетчик 3, выходной регистр 4 данных, выход которого является информационным выходом 5 устройства, блок 6 синхронизации, вход запуска которого является первым входом 7 синхронизации устройства, входной регистр 8 данных, информационный вход которого, является 20 информационным входом 9 устройства, регистр 10 кода задержки, элемент 11 задержки. Устройство имеет управляющий вход 12 и второй вход 13 синхронизации H содержит элемент ИЛИ 14. 25

Устройство для программируемой задержки работает следующим образом.

В начальный момент времени на входы 12 и 13 устройства поступают соответственно код задержки и сопро- 30 воздающий его управляющий сигнал, по которому осуществляется прием кода задержки в регистр 10 кода задержки.

Кроме того, управляющий сигнал через элемент 11 задержки поступает на вход

35 сброса счетчика 3, устанавливая его в нулевое состояние.

Элемент 11 задержки задерживает управляющий сигнал на время установки кода задержки на выходе регистра

10 кода задержки.

На вход запуска блока 6 синхронии It зации поступает сигнал типа меандр (фиг. 2а). С .выходов блока Ь синхронизации сигнала типа меандр (фиг.2б, 45 в) поступают на вход записи-считывания блоков,1 и 2. На вычитающий вход счетчика 3 подается сигнал с входа 7 синхронизации устройства. С приходом .на вычитающий вход счетчика 3 (нахо«50 дящегося в нулевом состоянии) нулевого значения сигнала на выходе заема счетчика 3 вырабатывается сигнал заема. Сигнал заема поступает на вход разрешения записи счетчика 3, кото55 рый при этом осуществляет прием кода задержки, подаваемого на его информационный вход с выхода регистра 10 кода задержки. При записи в счетчик 3 кода задержки, отличного от нуля, сигнал заема меняет свое значение, и прием кода в счетчик 3 прекращается. Приход каждого синхроимпульса на (вычитающий вход) счетчика 3 уменьшает значение его выхода на единицу. При достижении нулевого состояния счетчика 3 вновь вырабатывается сигнал .заема и осуществляется перезапись кода задержки с выхода регистра 10 кода задержки в счетчик 3.

Таким образом, счетчик 3 повторяет .каждое свое состояние через и тактов работы устройства, отсчитываемых входными синхросигналами (и — код задержки).

Код с выхода счетчика 3 (устанавливаемый в начале такта и действующий на всем его протяжении) подается на адресные входы блоков 1 и 2, обеспечивая обращение к определенной ячейке.

Сигнал типа "меандр", поступающий на вход блоков накопителей 1 и 2, задает по установленному адресу в первый период частоты синхронизации устройства (фиг. 2а, б, в), например, режим считывания для блока 1 и режим записи для блока 2 °

Сигнал типа "меандр", поступающий на синхровходы входного 8 и выходного 4 регистров обеспечивает запись информации, поступающей с входа 9 в регистр 8, затем в блок 2, а также с блока 1 в регистр 4. В момент времени t происходит изменение состоя3 ния счетчика 3 на единицу. На вход блока 1 поступает сигнал "Запись", на блок 2 — сигнал "Считывание". Сигналы "Считывание" и "Запись" на входах блоков 1 и 2 действуют в течение времени t > — t т.е. в течение периода частоты синхронизации устройства. За время t > — t новая информация, поступившая по входу 9 на устройство, запишется в регистр 8 и в блок 1, а с блока 2 — в регистр 4.

В момент времени t происходит изменение адреса на выходе счетчика 3 на единицу и в момент времени t — происходит считывание информации с блока 1 в регистр 4 и запись информации с выхода 9 устройства в регистр 8 и в блок 2 и т.д. Сигнал заема с выхода счетчика 3 поступает на один из входов элемента ИЛИ 14 на другой вход которого подается выход младшего разряда регис тра 10 кода

1376074 задержки. Если в регистре 10 кода задержки записано четное значение кода (младший разряд равен "0"), то с выхода элемента ИЛИ 14 снимается сигнал логического "0", который подается на блок 6 синхронизации и "опрокидывает" его, т.е. на выходах блока 6 синхронизации вырабатываются инверсные сигналы к изображенным на 10 фиг. 2б и в соответственно.

На выходе регистра 5 будет информация, записанная и тактов назад.

Если на выходе регистра 10 кода задержки записан нечетный код (младший 15 разряд равен "1"), то блок 6 синхронизации остается в прежнем состоянии, "Чтение" и "Запись" нужной ячейки памяти блоков 1 или 2 произойдет автоматически. 20

Формула изобретения

Устройство для программируемой задержки информации, содержащее входной регистр данных, первый блок памя- 25 ти, блок синхронизации, выходной регистр данных, регистр кода задержки, элемент задержки и счетчик, причем информационный вход входного регистра данных является информационным входом устройства, выход входного регистра данных подключен к информа.ционному входу первого блока памяти, вход записи-считывания которого соединен с первым выходом блока синхронизации, адресные входы первого бло35 ка памяти подключены к выходам разрядов счетчика, выход первого блока памяти подключен к информационному входу выходного регистра данных, выход которого является информационным . выходом устройства, выход заема счетчика подключен к входу разрешения записи счетчика, вход сброса счетчика соединен с выходом элемента задержки, входы разрядов счетчика соединены с выходами регистра кода задержки, вычитающий вход счетчика, вход запуска блока синхронизации и управляющие входы входного и выходного регистров данных объединены и являются первым входом синхронизации устройства, информационный вход ре» гистра кода задержки является управляющим входом устройства, вход элемента задержки и управляющий вход регистра кода задержки объединены и являются вторым входом синхронизации устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введен второй блок памяти и элемент ИЛИ, выход которого подключен к входу переключения состояния блока синхронизации, второй выход которого соединен с входом записи-считывания второго блока йамяти, адресные входы и информационный вход второго блока памяти подключены соответственно к выходам разрядов счетчика и выходу входного регистра данных, выход второго блока памяти соединен с информационным входом выходного регистра данных, первый и второй входы элемента ИЛИ подключены соответственно к выходу заема счетчика и к выходу младшего разряда регистра кода задержки.