Кодек самоортогонального квазициклического кода

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и позволяет повысить помехоустойчивость кодека при использовании восьмифазной модуляции. Кодек самоортогонального квазициклического кода содержит канал 2 связи, на передающей стороне 1 - кодер 4 и синхронизатор 5, на приемной стороне 3 - кодер 6, буферный регистр 7, блоки 9,10 оперативг ной памяти, полусумматоры 14-16., синдромные регистры 17,18, пороговые блоки 21,22 и синхронизатор 23. Введение на приемной стороне 3 буферного регистра 8, блоков 11,12 оперативной памяти, синдромных регистров 19,20 и корректора 13 обеспечивает многопороговое декодирование, дающее энергетический вьигрыш по сравнению с известным устройством. 4 з.п.ф-лы, 6 ил. S (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН g 4 H 03 М 13/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ-.

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4104988/24-24 (22) 04.06.86 (46) 23.02,88. Бюл. 9 7 (72) А.С. Данилин, А.Н. Козленко и С.Л. Портной (53) 621.391.25(088.8) (56) Труды НИИР, 1983, В 1, с .89-99.

IEEE Transactions.on Communication s, 19 78, ч. СОМ-26, У 10, р, 19-32, Некоторые вопросы теории кодирования: Сб. переводов/Под ред. Э.M. Блоха — М.: Мир, 1970, с.36-67, рис.2,4. (54) КОДЕК САМООРТОГОНАЛЬНОГО КВАЗИЦИКЛИЧЕСКОГО КОДА (57) Изобретение относится к автоматике и вычислительной технике и позволяет повысить помехоустойчивость

„„SU„„6247 А кодека при использовании восьмифазной модуляции. Кодек самоортогонального квазициклического кода содержит канал 2 связи, на передающей стороне

1 — кодер 4 и синхронизатор 5, на приемной стороне 3 — кодер 6, буферный регистр 7, блоки 9,10 оперативной памяти, полусумматоры 14-16, синдромные регистры 17,18, пороговые блоки 21,22 и синхронизатор 23. Введение на, приемной стороне 3 буферного регистра 8, блоков 11,12 оперативной памяти, синдромных регистров

19,20 и корректора 13 обеспечивает многопороговое декодирование, дающее энергетический выигрыш по сравнению с известным устройством. 4 з.п.ф-лы, 6 ил, 1376247

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах передачи информации.

Цель изобретения — повышение помехоустойчивости кодека при использовании восьмифазной модуляции.

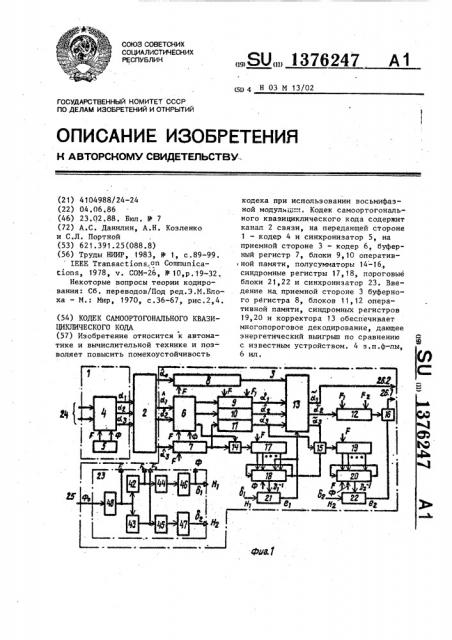

На фиг. 1 представлена блок-схема кодека самоортогонального квазицикли- 10 ческого кода;,на фиг.2-4 — функциональные схемы соответственно кодера, корректора и канала связи на фиг.5фазовая диаграмма сигналов на фиг.6временная структура сигналов в харак- 15 терных точках схемы кодека.

Кодек самоортогонального квазициклического кода состоит из (фиг.1) передающей стороны 1, канала 2 связи и приемной стороны 3. Передающая сто- 20 рона 1 кодека содержит кодер 4 и синхронизатор 5. Приемная сторона 3— включает в себя кодер 6, первый 7 и второй 8 буферные регистры, первыйчетвертый блоки 9-12 оперативной па- 25 мяти, корректор 13, первый-третий полусумматоры t4-16, первый-четвертый синдромные регистры 17-20, первый

21 и второй 22 пороговые блоки и синхронизатор 23. На фиг.1 обозначены 30 входы 24 кодека, вход 25 синхронизации приемной стороны 3 и выходы 26 кодека. о

Кодер 4 на передающей стороне и . кодер 6 на приемной стороне кодека выполнены одинаково (фиг.2): на первом-четвертом регистрах 27-30 сдвига и полусумматоре 31. На фиг.2 обозначены информационные 32 и тактовый 33 входы, вход 34 синхронизации и выходы 35.

Корректор 13 выполнен (фиг.3) на элементе НЕ 36, элементе ИЛИ 37, трех элементах И 38 и сумматоре 39. На фиг.3 обозначены входы 40 и выходы 41.45

Пороговый блок ?1 или 22 представляет собой сумматор, входы которого являются первыми входами блока, выходы подключены к первым входам элемента сравнения, вторые входы и выход которого являются вторыми входами и выходом порогового блока.

Синхронизатор 23 приемной стороны включает в себя (фиг.1) первый 42 и .второй 43 умножители частоты, .первый

44 и второй 45 делители <частоты, первый 46 и второй 47 вычитающие счетчики и генератор 48 тактовых импульсов. Соединения синхронизатора 23 с соответствующими блоками приемной стороны 3 обозначены буквами F F

F Ф, Н, и Н . На соединениях, выполненных шинами, указана их кратность.

Канал 2 связи представляет собой (фиг.4) соединенные последовательно первый преобразователь 49 кода, восьмифазный фазовый модулятор 50, линию

51 связи, шестнадцатифазный фазовый демодулятор 52 и второй преобразователь 53 кода. Преобразователи 49 и

53 обеспечивают соответственно преобразование двоичного кода в восьми-. ричный и шестнадцатиричного кода в двоичный.

Регистры 7,17-20, 27-30, а также ! блоки 9-12 имеют емкость M бит, где

М вЂ” длина ко<ового слова циклического кода, из которого построен используемый квазициклический (N,К,D)— код, где N=3M — общее число символов в кодовом слове;К=2М вЂ” число информационных символов; D — расстояние

Хэмминга используемого кода. Регистр

8 имеет емкость 2М бит.

Частоты сигналов синхронизатора

23 имеют следующие значения: на первом выходе F на втором и пятом выхоFD< FDa дах F †; — F =, на третьем

Р выходе Ф = — на четвертых и шестых

F< F выходах Н = — и Н = - . Кратность

< М 2 М последних из указанных выходов ; =

=)1о8 (П;--1)Г; i=1,2; à — ближайшее меньшее целое число.

Кодек самоортогонального квазициклического кода работает следующим образом, Исходная информация с входов 24 в двоичной форме Двумя импульсными потоками поступает на входы 32 кодера 4. При этом символы о, и с поступают соответственно на регистры 27 и 28. После их заполнения по сигналу на входе 34 (сигнал цикловой метки, фиг.6) информация переписывается в параллельном виде в регистры 29 и 30 и подвергается циклическим сдвигам по тактовым импульсам на входе 33.

В результате на выходе полусумматора

31 формируются проверочные символы

aL» которые вместе с информационными символами ol, a oL2 подаются на соответствующие выходы 35. Таким образом, 1376247 в кодере 4 осуществляется кодирование информации путем перемножения информационного слова на порождающую матрицу самоортогонального кваэициклического кода.

С выходов кодера 4 каждая двоичная последовательность М, М,ot попадает в канал 2 связи, где она преобразуется в цифровой сигнал со значениями от 0 до 7 (преобразователь 49,фиг.4), по которому в модуляторе 50 образуется сигнал несущей частоты с одним из восьми значений фазы (фиг.5). В линии 51 связи этот сигнал искажается15 под действием шумов и помех. В демодуляторе 52 искаженный сигнал оценивается так, что его фазе ставится в соответствие ближайшая из оценок, имеющих значения от 0 до 15. Эта оценка преобразуется в двоичный сигнал (преобразователь 53), причем символы кода л л л оценки с,,,, ос поступают на первый-третий выходы канала 2 связи, а символ о4, (младший разряд полученно- 25 го кода) — на четвертый выход канала 2. л л

Далее оценку информационных, Ы, л л проверочных oC и вспомогательных ь, символов параллельно поступают на входы приемной стороны 3. ИнформаЛ л ционные символы,,м, кодируются в кодере 6 аналогично тому, как это делается в кодере 4, т.е. на третьем выходе кодера 6 вырабатываются проУ 35 верочиые символы nL . Проверочные и л, л вспомогательные символы 0L и са, запоминаются в регистрах 7 и 8. В полусумматоре 14 соответствующие символы

v и 06 складыВаются по модулю дВа 40 образуя синдром, который запоминается в регистре 17. Одновременно симл л л волы,, о и, запоминаются в блоках 9-11 оперативной памяти.

По сигналу цикловой метки с выхода 45 старшего разряда вычитающего счетчика 46 синхронизатора 23 информация из регистра 17 переписывается в ре, гистр 18, где начинаются циклические сдвиги информации и Р,/2 циклов для последующего исправления, При этом исправляются только символы eL,è по следующие проверки в первом пороговом блоке 2.1 относятся тоже только к символу к, Результаты исправлений символа оь1

55 в виде параллельного кода подаются на вход первого порогового блока 21 с изменяемым порогом, который устанавливается на его вторых .входах (Н,). Если на выходе блока 21 символ е, =1, то по обратной связи он исправляет те символы во втором синдромном регистре 18, которые соответствуют проверкам. Если е, =О, то исправление не производится.

Задержанные во втором буферном регистре 8 и в блоках 9-11 символыс, М, (k,(а и симВОл е< с ВЫХОда перВОГО пОрогового блока 21 поступают на входы корректора 13, алгоритм функционирования которого имеет вид где все принимают двоичные значения

0 либо 1; (9 — сумма по модулю восемь запись о ь, eL имеет смысл целого числа от 0 до 7 в двоичной системе исчисления, е, — символ ошибки на пятом входе корректора 13.

Согласно этому алгоритму все симл л л волы о, eL М,сигнала корректируются только в том случае, если е =1, при л

Э этом, если < =1, то к фазе сигнала

I прибавляется „—, а если ь .,=О, то вычитается VN/4 (фиг.5) . В этом процесл л се еа, корректируется всегда, а к -в половине случаев.

После коррекции символы < поступают на второй выход 26.2 кодека, символы Г запоминаются в четвертом блоке 12, а символы о4 вместе с некорз ректированными символами еС складываются во втором полусумматоре 15 и результат используется для исправления синдрома, поступающего с выхода второго синдромного регистра 18 на один из входов второго полусумматора.

Если корректор 13 исправляет проверочный символ o7., (т.е. ìI ф ), то вторым полусумматором 15 осуществля ется коррекция соответствующего символа синдрома, поступающего на один из входов полусумматора 15.

Аналогично в процессе обработки в третьем 19 и четвертом 20 синдромных.регистрах, втором пороговом блоке 22 с другим изменяемым порогом и третьем полусумматоре 16 производит-, ся коррекция символа с, в результате которой формируется сигнал на первом выходе -26.1 кодека. На ВХОДА

1376Z47

25 приемной стороны 3 поступает сигнал с тракта синхронизации.

Рассмотренный кодек обрабатывает код с неодинаковой защитой символов.

Проверочная матрица кода имеет вид

Н =(С,С Х3 где С,, С вЂ” квадратные циркулятные

NxN матрицы, полученные

10 циклическим сдвигом перВой строки, T. — единичная NxN матрица.

Кодовая конструкция построена по следующим правилам: М =g +Q +1, g целое число, выбирается разностное

15 множество (i» i,, i,..., I <) порядка g причем ia=l, в первой строке матрицы С, ставятся единицы на пози Hõ (iо, >г,...,i ), а в первой строке матрицы Сz- единицы на позициПусть (всегда четное. Если j=

= /2, то имеем код с параметрами (ЗМ, 2М,D), где NI=q +q+1, Э=О/2+2.

Пример 1. /=4, М=16+4+1=21,, разностнОе мнО>кество (1, 2, 5, 1 5, 1 7 ) в

Для построения С„берем (1,2,5), а для С (1,15,17), т.е. для символов х,проверками являются 1-й, 2-й и 5-й

ЗО символы синдрома а для <«2 < й„15, и и 17-й.

Если не ставить задачу максимизировать минимальное расстояние кода, то получаются коды с неравной защитой символов. Первые М символов, за- 5 щищены с расстоянием О,, а вторые М симвОлОВ К вЂ” с расстоЯнием D „ причем

Э<+ В -Ц/4 и <> =Р2, При этом условии символы«>L можно называть более надеж40 ными, а символы е,менее надежными, Пример 2. (=4, М=16+4+1=21.

Для С, берем (1,2,5, 15), а для С (1, 17). Для символов М, проверками HB ляются 1-й 2-й 5-й и 15-й символы

У У . 45 синдрома, а для символов <> 1-й и 17-й символы синдрома. Таким образом, П<=5, Э,-З.

В восьмифазном модуляторе 50 канала 2 сВЯзи (фиго4-) каждому стОлбцу М,)50

«< >,М,символов ставится в. соответствие р =2(1-Ф(2Ь siI<«/8) ) =2 р, =2ф(421г sin « /4) (1-ф (=2(1-Ф(<2) ) Ф(.Я), При декодировании более надежных л символов м< (до коррекции) вероятодна из восьми фаэ (фиг.5). В шестнадцатифазном демодуляторе 52 вырал а л батывается оценка«,ñ,g>>, а также . информация (в виде символа о4, ) о том, к какому "соседу (какому из возможных сигналов) ближе принятый сигнал.

На приемной стороне 3 сначала декодируются более надежны<е символы nl, с расстоянием D Зтот процесс происходит многократно (D2>

При е,=1 в корректо1>е 13 корректи и л а руется весь столбец М, <>L,Û ïo указанному алгоритму. После этого осуществляется исправление менее надежных и символов g, с расстоянием 0 и вырабатывается сигнал ошибки е для них (вторая ступень декодирования).

Пусть В кодовом слове из N столбл цов <><,,<>,<, Ошибочно принято m N столбп и и цов видай.,«>I, Пусть также из них

m m ошибок сдвигают сигнал по фазе л в соседнее положение (фиг.5) такое, что принятый сигнал ближе к переданному, чем к другому "соседу". Если в первой ступени декодирование более и надежных символов, происходит без

Ошибок, то для второй ступени остается m — m, ошибок для исправления. Тем самым, если более надежные символы м, декодируются в "плохом" канале с восьмифазной модуляцией (с малой различающей способностью), то менее на,це>кные символы « декодируются как бы в канале с четырехфазной модуляцией (с большей различимостью).

Оценим для этих случаев верность передачи.

Пусть h — отношение сигнал/шум в канале, р, и p — вероятности ошибки в символе для восьми-и четырехфазной модуляции в канале с известным h. Тогда

1 (1-Ф(" 0, 293 h) ), 2h sin 74))>I < равна р <, вероятность ошибки

13762

47 8 вания 1 дБ при ) =10 по сравнению с четырехфазной модуляцией без кодирования.

Кодек с многопороговым декодиро30

1 31- I р = — (1-(1-2р ) (1-р ) й, 1 1

50 (1--р, /2) ), 1 D -11

= — )1-(1-2р )(1-p ) J . н г 2 .) в проверочных символах(равна р, /2, а вероятность ошибки в информационных символах а равна р,/4.

При декодировании менее надежных л символов ()г (после коррекции) вероятность ошибки в проверочных символах равна рг, а вероятность ошибки в откорректированных символак равна р /2. 10

Поэтому при декодировании бит I)L1 имеем высокую вероятность ошибки, а при декодировании остальных бит низкую, т.е. имеем повышение помеЛ л хоустойчивости в битахМ м,за счет л правильного декодирования. бит М, Пусть р, и p — частоты появления ошибок на втором и первом выходах

26 (()(.. и ()Ьг) кодера. Тогда ) = Р1 +

+ P, где ) — частота ошибок на вто- 20 ром выходе при правильном декодировании более надежных символов Ы1, а суммарная частота ошибок

1) 1" 2

31-1

Q+» (1-р„)

Bi-(1 г

31-1

«(1-Р«) СР «Р, (1-.Р„)

g«+ I с г 2 ()«=Р, СР p „(1-p„)

D2- I 35 г

Z) 2-I

«(1-Р,) С, p,, (1-p„) *, 0111 .40 где р — вероятность нечетного числа

И, ошибок в проверке на первом шаге (ступени); рн то же, на втором шаге при

Нг условии, что первые информационные символы декодированы правильно, I

С вЂ” число сочетаний иэ Э по г) Расчеты по этим формулам показывают, что при однопороговом декодирова-55 нии предлагаемый кодек с использованием восьмифазной модуляции обеспечивает энергетический выигрыш кодированием,как следует из результатов математического моделирования,обеспечивает энергетический выигрыш по сравнению,с четырехфазной модуляцией

6 без кодирования 4 дБ при $ =10

Таким образом, предлагаемый кодек обеспечивает повышение помехоустойчивости сигналов при работе в кана-. лах с восьмифазной модуляцией.

Формула изобретения

1. Кодек самоортогонального квазициклического кода, содержащий на передающей стороне кодер. информационные входы которого являются входами кодека, и синхронизатор, первый и второй выходы которого соединены соответственно с тактовым входом и входом синхронизации кодера, первыйтретий выходы которого подключены к входам канала связи, на приемной стороне — кодер, первый, второй и третий выходы котoporо соединены соответственно с информационными входами первого и второго блоков оперативной памяти и первым входом первого полусумматора, первый буферный регистр, выход которого соединен с вторым входом первого полусумматора, выход которого подключен к информационному входу первого синдромного регистра, параллельные выходы которо

ro соединены с установочными входами второго синдромного регистра, параллельные выходы которого подключены к первым входам первого порогового блока, второй полусумматор, второй лоро говый блок, выход которого соединен с первым входом третьего полусумматора, и синхронизатор, первый выход которого соединен с тактовыми входа- . ми первого буферного регистра, первого и второго синдромных регистров, первого и второго блоков оперативной памяти и кодера, второй выход синхронизатора подключен к входам синхронизации первого и второго блоков оперативной памяти, третий выход синхронизатора соединен с входами синхронизации кодера и второго синдромного регистра, последовательный выход которого соединен с его информационным входом, четвертые выходы синхраниза9 1376247 1 О тора подключены к вторым входам первого порогового блока, выход которого соединен с управляющим входом второго синдромного регистра, первый и второй информационные входы кодера и инфор5 мационный вход первого буферного регистра подключены соответственно к первому - третьему выходам каналам связи, выход третьего полусумматора является пергым выходом кодека, о тличающи йс я тем, что, с целью повышения помехоустойчивости кодека при использовании восьмифаз ной модуляции на приемной стороне кодека введены корректор, третий и четвертый блоки оперативной памяти, третий и четвертый синдромные регистры и второй буферный регистр, выход которого соединен с первым входом корректора, выходы первого и второго блоков оперативной памяти соединены соответственно с вторым и третьим входами корректора, первый и второй выходы которого соединены соответственно с информационным входом четвертого блока оперативной памяти и с первым входом второго полусумматора, выходы которых подключены соответственно к второму входу третьего полусумматора и к информационному входу третьего синдромного регистра, информационный вход третьего блока оперативной памяти подключен к выходу первого буферного регистра, выход тре35 тьего блока оперативной памяти соединен с вторым входом второго полусумматора и четвертым входом корректора, пятый вхоц которого подключен к выходу первого порогового блока, третий вход второго полусумматора подключен к последовательному выходу второго синдромного регистра, параллельные выходы третьего сипдромного регистра соединены с установочными входами четвертого синдромного регистра, параллельные выхоцы которого соединены с установочными входами второго порогового блока, тактовые входы второго буферного регистра, третьего

50 блока оперативной памяти, третьего и четвертого синдромных регистров подключены к первому выходу синхрони.затора, вход синхронизации третьего блока оперативной памяти и тактовый

55 вход четвертого блока оперативнои памяти подключены к второму выходу синхронизатора, вход синхронизации четвертого синдромного регистра подключен к третьему выходу синхронизатора, пятый и шестой выходы которого соединены соответственно с входом синхронизации четвертого блока оперативной памяти и вторыми входами второго порогового блока, последовательный выход четвертого синдромного регистра соединен с его информационным входом, информационный вход второго буферного регистра подключен к четвертому выходу канала связи, вход синхронизатора является входом синхронизации кодека, третий выход корректора является вторым выходом кодека °

2. Кодек по п.1, о т л и ч а юшийся тем, что кодер передающей и приемной стороны выпОлнен на регистрах сдвига и полусумматоре, параллельные выходы первого и второго регистров сдвига соединены с установочными входами соответственно третьего и четвертого регистров сдвига, параллельные выходы которых подключены соответственно к первым и вторым входам полусумматора, последовательные выходы третьего и четвертого регистров сдвига соединены со своими информационными входами, информационные входы первого и второго регистров сдвига являются соответственно первым и вторым информационными входами кодера, тактовые входы всех регистров сдвига объединены и являются тактовым входом кодера, входы синхронизации третьего и четвертого регистров сдвига объединены и являются входом синхронизации кодера, последовательные выходы первого и второго регистров сдвига и выход полусумматора являются соответственно первым — третьим выходами кодера.

3. Кодек по п.1, о т л и ч а ю— шийся тем, что корректор выпол-, нен на элементах И, элементе НЕ, сумматоре и элементе ИЛИ, выход которого соединен с первым входом первого элемента И, выход элемента HE подключен к первому входу элемента ИЛИ и первым входам второго и третьего элементов И, выходы первого-третьего элементов И соединены с соответствующими первыми входами сумматора, второй вход элемента HJIH и вход элемента НЕ объединены и являются первым входом корректора, вторые входы сумматора являются вторым — четвертым входами корректора, вторые входы

1376247

12 всех элементов И объединены и являются пятым входом корректора, выходы сумматора являются соответствующими выходами корректора.

4. Кодек по п.1 о т л и ч а ю— шийся тем, что синхронизатор приемной стороны выполнен на умножителях частоты, делителях частоты, вычитающих счетчиках и генераторе 10 тактовых импульсов, выход которого подключен к входам умножителей частоты и является первым выходом синхронизатора, выходы первого и второго умножителей частоты через одноименные делители частоты подключены к входам одноименных вычитающих счетчиков, вход генератора тактовых импульсов является входом синхронизатора выход первого умножителя частоты, 20 выход старшего разряда первого вычитающего счетчика, выходы всех разрядов первого вычитающего счетчика, выход второго умножителя частоты и выходы разрядов второго вычитающего счетчика являются соответственно вторым, третьим, четвертыми, пятым и шестьпы выходами синхронизатора.

5. Кодекпоп.1, отличаюшийся тем, что канал связи выполнен на соединенных последовательно первом преобразователе кода, восьмифазном фазовом модуляторе, линии связи, шестнадцатифазном фазовом демодуляторе и втором преобразователе кода, первый-третий информационные входы первого преобразователя кода являются соответствующими входами канала связи, первый-четвертый выходы второго преобразователя кода являются одноименными выходами канала связи.

1376247

АФ (1О 0

1376247 (2)

ВХ

Вых(2)

Фиг. b

Составитель О. Ревинский

Редактор О. Головач Техред Л.Олийнык Корректор Л. Патай

Заказ 798/56 Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4