Аналого-дискретное интегрирующее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, а именно к гиб- . ридным вычислительным устройствам, предназначенным для .точного и длительного интегрирования произвольно меняющихся функций времени. Целью Von изобретения является расширение функциональных возможностей за счет оперативного изменения в процессе расширения постоянной времени в широком диапазоне. Аналого-дискретное интегрирующее устройство содержит блок 1 преобразования полярности ВХ.ОДН о го сигнала, аналоговый интегратор 2, компараторы 3 и 4, счетчик 5, блок 6 определения полярности входного сигнала, блок 7 формирования порогового уровня, элемент ИЛИ 8, управляющий триггер 9, блок 10 определения направления счета, формирователь 11 счетных импульсов, дешифратор 12 и масштабный счетчик 13. Введенный в устройство масштабный счетчик 13 позволяет дискретно в широком диапазоне изменять постоянную времени интегрирования. 2 ил. W со ч| 00 4j ел (JiUtl

СОК)3 СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН ая> в) С51) 4 G 06 G 7/186 3 г< j >,4"! У

Ы, ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

Н Д BTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 4019126/24-24 (22) 97.02.86 (46) 29.02.88. Бюл. В 8 (71) Институт проблем моделирования в энергетике АН УССР (72) Г.И.Грездов, 9.П.Космач и Г.А.Лобок (53) 681.335(088.8) (56) Авторское свидетельство СССР

9 556463, кл. G 06 I 1/00, 1975.

Авторское свидетельство СССР

9 875407, кл. G Об С 7/186, 1979. (54) АНАЛОГО-ДИСКРЕТНОЕ ИНТЕГРИРУ10ЩЕЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике, а именно к гиб- . ридным вычислительным устройствам, предназначенным для .точного и длительного интегрирования произвольно меняющихся функций времени, Целью

I изобретения является расширение функциональных возможностей эа счет оперативного изменения в процессе расширения постоянной времени в широком диапазоне. Аналого-дискретное интегрирующее устройство содержит блок 1 преобразования полярности входного сигнала, аналоговый интегратор 2, компараторы 3 и 4, счетчик 5, блок 6 определения полярности входного сигнала, блок 7 формирования порогового уровня, элемент ИЛИ

8, управляющий триггер 9, блок 10 определения направления счета, формирователь 11 счетных импульсов, дешифратор 12 и масштабный счетчик 13.

Введенный в устройство масштабный счетчик 13 позволяет дискретно в широком диапазоне изменять постоянную времени интегрирования.

1377875

Изобретение относится к вычислительной технике, а именно к гибридным вычислительным устройствам, предназначенным для точного и длитель- 5 ного интЕгрирования произвольно меняющихся функций времени.

Цел. э изобретения является расширение функциональных возможностей устройства за счет оперативного измене- 10 ния в процессе решения постоянной времени в широких пределах.

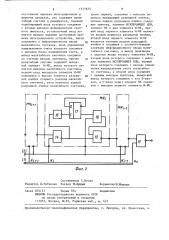

На фиг. 1 представлена функциональная схема аналого-дискретного интегрирующего устройства; на фиг. 2 — 15 схема масштабного счетчика.

Аналого-дискретное интегрирующее устройство (фиг. 1) состоит из блока

1 преобразования полярности входного сигнала, аналогового интегратора 20

2, компараторов 3 и 4, счетчика 5, блока 6 определения полярности входного сигнала, блока 7 формирования порогового уровня элемента ИЛИ 8, управляющего триггера 9, блока 10 определения направления счета, формирователя 11 счетных импульсов,,цешифратора 12 и масштабного счетчика 13.

Масштабный счетчик 13 (фиг, 2) со- 30 ,цержит N разрядных ячеек, каждая иэ .которых состоит из элементов И-НЕ

14, 15, элемента НЕ 16, триггера 17, элемента ИСКЛ10ЧА10ЩЕЕ ИЛИ 18, и общий ,цля всех ячеек выходной элемент И-НЕ

19.

Устройство работает следующим образом.

Входной сигнал поступает через блок 1 преобразования полярности вход-40 ного сигнала на вход аналогового интегратора 2. Как только напряжение на гыходе интегратора достигнет порогового уровня, срабатывает соответствующий компаратор и знак подынтегральной функции на выходе блока 1

:изменяется на противоположный. Таким образом при знакопостоянном входном сигнале компараторы срабатывают поочередно. Блок 6 определяет полярность входного сигнала и вырабатывает управляющий сигнал, с помощью которого из входного сигнала и эталонного опорного напряжения на выходе блока

7 формируется компенсационное порого-5>

:вое напряжение, которое подается на

:вторые входы компараторов 3 и 4.

Счетные импульсы с выхода формирователя 11 счетных импульсов поступают на стробирующий вход дешифратора

12. Значение двоичного кода, поступающего на установочный вход дешифратора 12, определяет номер N; выхода дешифратора, на котором появляются счетные импульсы. Масштабный счетчик

13, представляющий собой реверсивный счетчик с изменяемым кратным двойке коэффициентом пересчета, в зависимости от направления счета на его втором входе накапливает счетные импульсы, поступающие по информационному входу. При этом формируется дискретная часть постоянной интегрирования.

Счетные импульсы, появляющиеся на выходе масштабного счетчика с постоянной интегрирования о, поступают на счетный вход счетчика 5, который осуществляет накопление результата интегрирования.

Формула изобретения

Аналого-дискретное интегрирующее устройство, содержащее последовательно соединенные блок преобразования полярности входногб сигнала, вход которого является информационным входом устройства, и аналоговый интегратор, выход которого подключен к первым входам компараторов, выходы которых соединены с информационными входами блока определения направления счета и через элемент ИЛИ подключены к входам управляющего триггера и формирователя счетных импульсов, первый выход которого соединен с входом сброса аналогового интегратора, выход управляющего триггера связан с входом управления знаком блока преобразования полярности и управляющим входом блока определения направления счета, блок формирования порогового уровня, потенциальные входы которого подключены к входу опорного напряжения устройства и информационному входу устройства, соединенному через блок определения по лярности с управляющим входом блока формирования порогового уровня, и счетчик, выход которого является выходом устройства, а вход управления направлением счета подключен к выходу блока определения направления счета, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей устройства за счет оперативного изменения в процессе решения

1377875

Составитель С, Белан

Редактор И.Рыбченко Техред И.Дидык

Корректор: И. Шароши

Заказ 876/47 Тираж 704

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Подписное

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 постоянной времени интегрирования в широких пределах, оно содержит масштабный счетчик и дешифратор, съемный стробирующий вход которого соединен с вторым выходом формирователя счетного импульса, установочный вход является входом задания постоянной времени интегрирования устройства, выход подключен к информационному входу . 1p масштабного счетчика, вход управления направлением счета которого соединен с выходом блока направления счета, а выход масштабного счетчика соединен со счетным входом счетчика, причем 15 масштабный счетчик содержит выходной элемент И-НЕ, выход которого является выходом масштабного счетчика, первый вход выходного элемента И-НЕ подключен к выходу переноса разряд- Zp ной ячейки старшего разряда масштабного счетчика, вход переноса каждой разрядной ячейки масштабного счетчика, кроме первой, соединен с выходом переноса предыдущей разрядной ячейки, причем каждая разрядная ячейка содержит триггер, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент НЕ и два элемента И-НЕ, первый вход первого элемента И-НЕ является входом переноса разрядной ячейки, второй вход первого элемента И-HE является счетным входом разрядной ячейки и соединен с соответствующим разрядом информационного входа масштабного счетчика, а выход подключен к первому входу второго элемента -HE второй вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с входом управления направлением счета масштабного счетчика, а второй вход соединен с прямым выходом триггера, инверсный выход которого соединен с его D-вхо— дом, а С-вход через элемент НЕ соединен с выходом первого элемента И-НЕ.