Запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в устройствах памяти с коррекцией ошибок. Цель изобретения состоит в упрощении устройства за счет уменьшения площади интегральной микросхемы памяти, занятой разделительными элементами 15. Б случае замыкам кия транзистора выборки элемента памяти 1 на подложку выходит из строя только один элемент памяти, а не элементы памяти всего слова. Ошибочная информация корректируется с помощью элементов памяти 2 контрольного разряда и первой 7 и второй 8 групп элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. Поставленная цель достигается применением в качестве разделительных элементов 15 диодов, а не конденсаторов, как в прототипе. 1 ил. Ш

СОЮЗ СО8ЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51) 4 С 11 С 11/40

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTMA

Н АBTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 4041753/24-24 (22) 10.02.86 (46) 29.02.88. Бюл. № 8 (72) P.À. Лашевский, Н.Н. Брагин и А.И. Сегаль (53) 681.327,66 (088.8) (56) Микроэлектроника, 1978, т.7, вып. 4; с. 328-336.

Авторское свидетельство СССР № 1293760, кл, G ll С 11/40, 1985.

I (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике и может быть использовано в устройствах памяти с коррекцией ошибок. Цель изобретения сос„,Я0„„1377913 A 1 тоит в упрощении устройства sa счет уменьшения площади интегральной микросхемы памяти, занятой разделительными элементами 15. В случае замыка ния транзистора выборки элемента памяти 1 на подложку выходит из строя только один элемент памяти, а не элементы памяти всего слова. Ошибочная информация корректируется с помощью элементов памяти 2 контрольного разряда и первой 7 и второй 8 групп элементов ИСКЛЮЧАК1ЦЕЕ ИЛИ. Поставленная цель достигается применением в качестве разделительных элементов 15 диодов, а не конденсаторов, как в прототипе. 1 ил.

1377913

Изобретение относится к вычислительной технике, в частности к полупроводниковым интегральным устройствам памяти.

Целью изобретения является упрощение устройства за счет уменьшения площади интегральной микросхемы памыти, занятой разделительными элементами.

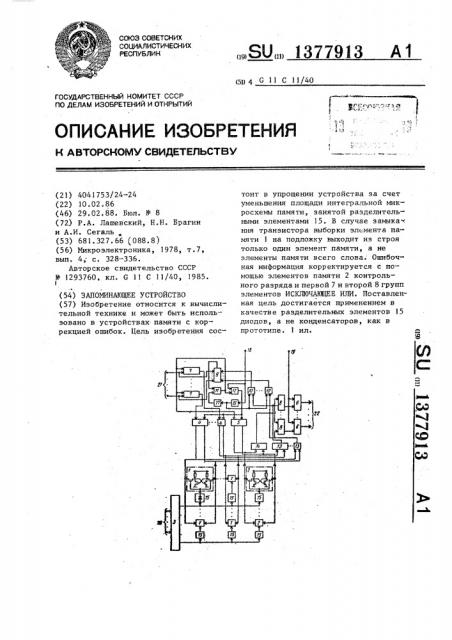

На чертеже представлена структурная схема запоминающего устройства.

Устройство содержит элементы 1 . памяти информационных разрядов, элементы 2 памяти контрольного разряда, дешифратор 3, блоки записи информационных 4 и контрольного 5 разрядов, блоки 6 считывания информационных разрядов, элементы ИСКЛЮЧАКМЦЕЕ ИЛИ первой 7 и второй 8 групп, блок 9 сравнения, группу элементов И 10, элемент И 11, элемент ИЛИ 12, усилители считывания информационных }3 и контрольного 14 разрядов, разделительные элементы 15 на диодах, первый 16 и второй 17 элементы. задержки, вход 18 разрешения записи, вход

19 разрешения считывания, адресные входы 20,.информационные входы

21 и выходы 22 устройства.

Устройство работает следующим образом.

В режиме записи (единичный сигнал на входе 18) с входов 21 через элементы ? информация в прямом коде поступает на входы блоков 4 записи, с выходов которых она поступает на числовые входы-выходы элементов 1 памяти информационных разрядов.. Одновременно дешифратор 3 в соответствии с кодом. адреса на входах 20 возбуждает одну из адресных шин, отпирая адресные транзисторы в элементе 1 памяти информационных разрядов и элементе 2 памяти контрольного разряда, подключенных к соответствующему выходу дешифратора 3 через разделительные элементы 15..

В результате, информация, установленная на входах 21, записывается в соответствующие элементы 1 памяти информационных разрядов, Одновременно в элемент 2 памяти контрольного разряда через блок 5 записи контрольного разряда записывается

"0", так как отсутствует сигнал на выходе элемента И 11. Для обнаружения возможной ошибки из-за неисправности одного из элементов памяти ин15

Если ошибка есть, то на выходе блока 9 сравнения формируется сигнал ошибки записи, который поступает через .элемент И 11 на соответствующие входы элементов 7, разрешая инвертирование в последних содержимого всего записываемого слова и перезапись его в таком виде по данному адресу. При этом в элемент 2 памяти контрольного разряда, подключенный к данному выходу дешифратора 3 через разделительный элемент 15. записывается единичный символ, поступающий с выхода элемента И 11 через блок 5 записи контрольного разряда. Сигнал, тактирующий работу блоков записи информационных 4 и контрольного 5.разрядов, формируется на выходе элемента ИЛИ 12, на входы которого подаются сигналы "Раз" решение записи" с входа 18 .и с выхода второго элемента 17 задержки через элемент И 11.

В режиме считывания. (единичный сигнал на входе 19) дешифратор 3, как и в режиме записи, возбуждает одну из адресных шин, отпирая адресные транзисторы в соответствующих элементах 1 памяти информационных разрядов и элементе 2 памяти контрольного разряда, Считываемая нз элементов 1 памяти информация через соответствующие усилители 13 считы- .: вания поступает на входы элементов 8, на другие входы которых с элемента

2 памяти контрольного разряда через усилитель 14 считывания контрольного разряда поступает сигнал, который при наличии в слове дефектного элемента памяти инвертирует считываемую информацию (на элементе 8),и, таким образом, исправляет сигнал; считанный из дефектного элемента памяти, поскольку он не инвертируется при повторной записи из-за неисправности элемента памяти (информация в де фектном элементе памяти не изменена).

Информация с исправных элементов 1

t формационного разряда после записи информации по сигналу. с выхода первого элемента 16 задержки происходит контрольное считывание по этому же адресу и сравнение в блоке 9 сравнения считываемой информации, поступающей с выходов соответствующих усилителей 13 считывания, через эле1О менты И группы 10 с имеющейся на инФормационных входах 21 устройства.

1377913

15

25 памяти остается неизменной, так как инвертируется дважды:. при повторной записи и при считывании. С выходов

8 элементов считываемая информация поступает на входы блоков 6 считывания и на информационные выходы 22 устройства.

Функции, выполняемые разделительным элементом 15 на диоде.

Если выход дешифратора 3 не выбран, то он имеет низкий потенциал.

При этом емкости затворов адресных транзисторов элементов памяти разряжены обратным током диода 15 ° . Параметры диода 15 выбираются такими, чтобы время разряда емкостей затворов адресных транзисторов элементов

1 памяти его обратным током было достаточно малым (десятки нс).

При записи или считывании на выбранном выходе дешифратора 3 устанавливается высокий потенциал. Емкости затворов адресных транзисторов элементов 1 памяти заряжаются через открытЬ|й диод 15, подготавливая элемент 1 памяти для записи или считывания.

При пробое .подзатворного окисла адресного транзистора в области затвор-cTQK и наличии на соответствующем числовом входе-.выходе высокого- напряжения при отсутствии диода 15 возможно возбуждение невыбранной строки, что приведет к сбою в работе устройства. Наличие диода

15 .позволяет ограничить ток, связанный с таким замыканием, и сохранить низкий потенциал на невыбранной строке.

Формула изобретения

Запоминающее устройство, содержащее элементы памяти информационных и контрольного разрядов, дешифратор, блоки записи информационных и контрольного разрядов, усилители считывания информационных и контрольного разрядов, .блоки считывания информационных разрядов, блок сравнения, первую и вторую группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группу элементов И, элемент ИЛИ, элемент И, первый и второй элементы задержки и группы разделительных элементов, причем числовые входы-выходы элементов памяти информационных и контроль30

50 ного разрядов соединены с выходами блоков записи соответственно информационных и контрольного разрядов, первые входы блоков записи информационных и контрольного разрядов соединены с выходом элемента ИЛИ, вторые входы блоков записи информационных разрядов соединены с выходами соответствующих элементов ИСКЛЮЧАЮЩЕЕ

ИЛИ первой группы, первые входы которых соединены с выходом элемента И, первым входом элемента ИЛИ и вторым входом блока записи контрольного разряда, второй вход элемента

ИЛИ соединен с выходом первого элемента задержки и является входом разрешения записи устройства, выход первого элемента задержки соединен с первыми входами элементов И группы и с входом второго элемента задержки, выход которого соединен с первым входом элемента И, второй вход кото.рого соединен с выходом блока сравнения, выходы блоков записи информационных и контрольного разрядов соединены с входами усилителей считывания соответственно информационных и контрольного разрядов, выходы усилителей считывания информационных разрядов соединены с вторыми входами соответствующих элементов И группы и с первыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, вторые входы которых соединены с выходом усилителя считывания контрольного разряда, а выходы — с первыми входами соответствующих блоков считывания информационных разрядов, вторые входы которых являются входом разрешения считывания устройства, а выходы — информационными выходами устройства, выходы элементов

И группы соединены с входами первой группы блока сравнения., входы второй группы которого соединены с вторыми входами элементов ИСКЛЮЧА10ЩЕЕ ИЛИ первой группы и являются информационными входами устройства, адресные входы элементов памяти информационных и контрольного разрядов соединены с первыми выводами разделительных. элементов групп, вторые выводы разделительных элементов каждой группы соединены с сответствующими выходами дешифратора, входы которого являются адресными входами устройства, отличающееся тем, что, с целью упрощения устройства, 1377913 каждый разделительный элемент выполнен в виде диода, катод которого яв-: ляется первым, а анод — вторым выводами разделительного элемента.

Составитель А. Дерюгин

Редактор H. Слободяник Техред И.Попович Корректор С. Шекмар

Заказ 880/49 Тираж 590 Подписное

ВНИИНИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4