Устройство аналоговой памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к аналоговой вычислительной технике, в частности к устройствам обработки выходного сигнала интегральных схем с зарядовой связью. Цель изобретения - повышение точности устройства аналоговой памяти. Поставленная цель осуществляется за счет того, что в интервалах времени между выбЪрками компенсирующие элементы на резисторах, ключевые элементы на транзисторах первого и второго типов проводимости, а также накопительный элемент на конденсаторе образуют резистивно-емкостные делители входного сигнала с маг лым коэффициентом передачи, обеспечивающие экранирование накопительного элемента и входа усилителя. Устройство содержит накопительный элемент 1 на конденсаторе, ключевые элементы на транзисторах 3, 6 первого типа проводимости, ключевые элементы на транзисторах 4,5 второго типа провоз дикости, компенсирующие элементы на резисторах 7, 8, коммутирующие и компенсирующие на диодах 9-12, стробируемые генераторы 13, 14 тока. 1 ил. с € сл

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБ ЛИК (дц 4 G 11 С 27/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4133246/24-24 (22) 08.10.86 (46) 29.02.88. Бюл. У 8 (71) Московский инженерно-физический институт(72) 10.А.Зубец и В.Я.Стенин (53) 681.327.66(088.8) (56) Бахтиаров Г.Д. и др. Аналогоцифровые преобразователи. М.: Сов, радио, 1980, с. 135, рис. 6.12.

Патент Японии Ф 60-31130, ил. Н 03 К 17/60, опублик. 1985. (54) УСТРОЙСТВО АНАЛОГОВОЙ ПАМЯТИ

{57) Изобретение относится к аналоговой вычислительной технике, в частности к устройствам обработки выходного сигнала интегральных схем с зарядовой связью. Цель изобретения— повышение точности устройства аналоговой памяти. Поставленная цель осу„„SU,» 1 77916 А1 ществляется за счет того, что в ийтервалах времени между выборками компенсирующие элементы на резисторах, ключевые элементы на транзисторах первого и второго типов проводимости, а также накопительный элемент на конденсаторе образуют резистивно-емкостные делители входного сигнала с ма.лым коэффициентом передачи, обеспечивающие экранирование накопительного элемента и входа усилителя. Устройство содержит накопительный элемент

1 на конденсаторе, ключевые элементы на транзисторах 3, 6 первого типа проводимости, ключевые элементы на транзисторах 4, 5 второго типа прово димости, компенсирующие элементы на резисторах 7, 8, коммутирующие и компенсирующие элементы на диодах

9-12, стробируемые генераторы 13, 14 тока. 1 ил.

1377916

Изобретение относится к автоматике и вычислительной технике и может найти применение в дискретно-аналоговых преобразователях сигналов, в устройствах считывания выходных сигналов ИС с зарядовой связью ИСЗС} и других устройствах.

Цель изобретения — повышение точности устройства. 10

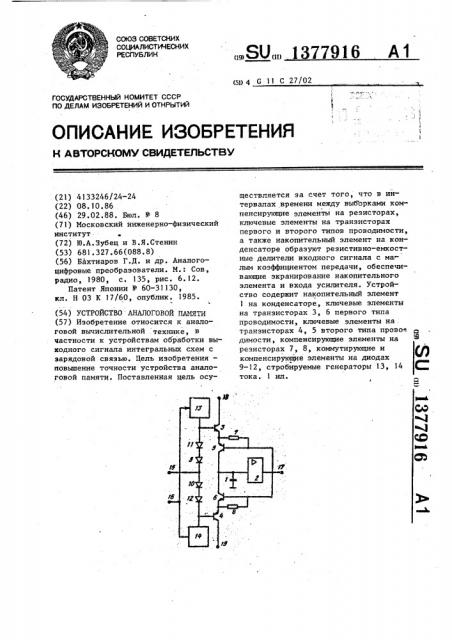

На чертеже представлено устройство аналоговой памяти.

Устройство содержит накопительный элемент 1 на конденсаторе, усилительповторитель 2, первый и второй ключе- !5 вые элементы на транзисторах 3, 4 соответственно первого и второго типа проводимости, третий и четвертый ключевые элементы на транзисторах

5, 6 соответственно второго и перво- 20 го типов проводимости, первый и второй компенсирующие элементы Hà резисторах 7, 8, первый и второй комму= тирующие элементы на диодах 9, 10, первый и второй компенсиру щие эле- 25 менты на диодах 11 12> первый 13 и второй 14 стробируемые генераторы тока, информационный 15 и управляющий

16 входы, информационный выход 17, шины 18, 19 питания. 30

Устройство работает следующим об" разом.

В режиме выборки на входе 16 устройства имеется высокий уровень управляющего сигнала. Первый !3 и второй 35

14 генераторы тока вырабатывают токи, проходящие соответственно через диоды 11, 9, !0, 12. Величины токов генераторов 13, 14 выбираются равными, диод 11 и транзистор 3, диод 9 и 40 транзистор 5, диод 10 и транзистор

6, диод 12 и транзистор 4 подбираются в пары по равным падениям напряжения на прямосмещенном переходе диода и на эмиттерном переходе транзистора 45 в активной области при одинаковых токах. Входные сигналы передаются через диоды 9, 11 на базу транзистора

3 и через диоды 10, 12 — на базу транзистора 4. Разность токов, проте- 50 кающая через транзисторы 3, 5 и 4, 6, уравнивает потенциал на входе усилителя 2, входе 15 и выходе 17.

Транзисторы 5, 6, усилитель 2 образуют усилительный блок с повторителя- 55 ми тока на входе и с емкостью коррекции на накопительном элементе 1.

При появлении на входе 16 сигнала низкого уровня устройство переходит в режим хранения, генераторы 13, 14 тока выключаются,.диоды 9-12. закрываются, потенциал базы транзистора

3 становится меньше потенциала его эмиттера, и транзистор 3 закрывается. Аналогично потенциал базы тран зистора 4 становится больше потенциала его эмиттера, и он закрывается.

При изменении напряжения на входе 15 в режиме хранения входной сигнал устройства поступает в базовые цепи транзисторов 3, 4 через приоткрывающиеся диоды 9, !1 или 10, 12 в зависимости от полярности или через их барьерные емкостФ. Далее сигнал может проникать на вход усилителя 2 и на выход 17, существенно ослабленным дифференцирующими цепочками, состоящими из емкостей эмиттерных переходов транзисторов 3, 4 и рез:исторов 7, 8, а также емкостными делителями из проходных емкостей транз:исторов 5, 6 и элемента 1. Сопротивления резисторов 7, 8 выбираются небольшими, чтобы постоянные времени дифференцирующих цепочек были меньше постоянной времени форми рования входного сигнала или постоян. ной усилителя 2, и тогда амплитуда сигналов, приходящих с входа 15 на выход 17, будет дополнительно уменьшена в несколько раз.

Формула изобретения

Устройство аналоговой памяти, содержащее первый и второй стробируемые генераторы тока, первый и второй ключевые элементы на транзисторах соответственно первого и второго типов проводимости, первый и второй коммутирующие элементы на диодах, усилитель-повторитель., первый и второй компенсирующие элементы на резисторах, накопительный элемент на конденсаторе, обкладки которого подключены соответственно к шине нулевого потенциала устройства и входу усилителя-повторителя, выход которого соединен с первыми выводами первого и второго компенсирующих элементов на резисторах и является информационным выходом устройства, анод первого и катод второго коммутирующих элементов на диодах объединены и являются информационным входом устройства, входы первого и второго стробируемых генераторов тока объединены и являют1377916

Составитель А.Ершова

Техред И.Попович Корректор М.Демчик

Редактор Н.Слободяник

Заказ 880/49 Тираж 590 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 ся управляющим входом устройства, а их выходы подключены соответственно к базам" первого и второго ключевых элементов на транзисторах, коллекторы которых подключены соответственно к первой и второй шинам питания уст-ройства,.о т л и ч а ю щ е е с я тем, что, с целью повышения точности устройства, в него введены первый и второй компенсирующие элементы на. диодах, третий и четвертый ключевые элементы на транзисторах, коллекторы которых объединены и подключены к .входу усилителя-повторителя, эмиттеры объединены соответственно с змиттерами первого и второго ключевых элементов на транзисторах и подключены соответственно к вторым выводам первого и второго компенсирующих элементов на резисторах, первые выводы которых подключены соответственно к базам третьего и четвертого ключевых элементов на транзисторах, анод первого и катод второго компенсирующих элементов на диодах подключены соот-, ветственно к выходам первого и второго стробируемых генераторов тока, катод первого и анод второго компенсирующих элементов на диодах подключены соответственно к аноду первого и катоду второго коммутирующих элементов на диодах.