Синхронный режекторный фильтр

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и улучшает подавление синхронной помехи. Фильтр содержит конденсатор (К) 1, ключ 3, повторитель 5 напряжения, блок 6 коммутируемых К, блок 8 выборки и хранения, распределитель 9 импульсов. Вновь введены К 2, ключ 4 и алгебраич. сумматор 7. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) SU (Ill (51) 4 Н 03 H 19/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHGMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3957449/24-09 (22) 24.09.85 (46) 29.02.88. Бюл. к- 8 (72) С,Е. Ремизов, С.Я. Ивандов и И.В. Мальппко (53) 621.372.543(088.8) (56) Авторское свидетельство СССР

9 1142888, кл. Н 03 H 19/00, 1983. (54) СИНХРОННЫЙ РЕЖЕКТОРНЫИ ФИЛЬТР (57) Изобретение относится к радиотехнике и улучшает подавление синхронной помехи. Фильтр содержит конденсатор (К) 1, ключ 3, повтори- . тель 5 напряжения, блок 6 коммутируемых К, блок 8 выборки и хранения, распределитель 9 импульсов. Вновь введены К 2, ключ 4 и алгебраич. сумматор 7. 2 ил.

137801 7

Изобретение относится к радиотехнике и может быть использовано для подавления синхронной периодической помехи.

Цель изобретения — улучшение подавления синхронной помехи.

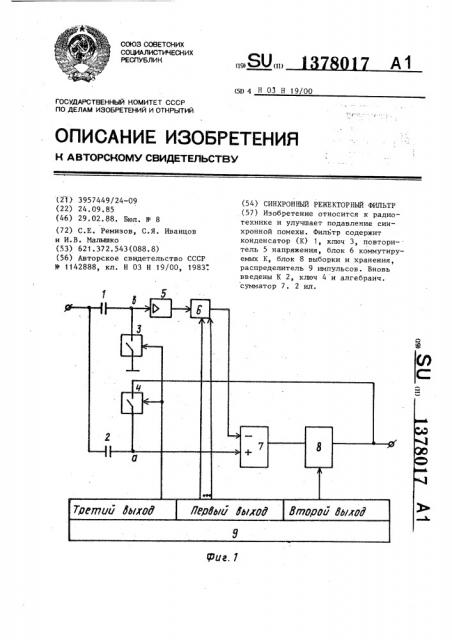

На фиг. 1 приведена принципиальная электрическая схема синхронного режекторного фильтра; на фиг. 2 — 10 эпюры сигналов распределителя импульсов.

Синхронный режекторный фильтр содержит первый 1, второй 2 конденсаторы, первый 3, второй 4 ключ и по- 15 вторитель 5 напряжения, блок б коммутируемых конденсаторов, алгебраический сумматор 7, блок 8 выборки и хранения, распределитель 9 импульсов.

Синхронный режекторный фильтр ра- 20 ботает следующим образом.

Входной сигнал подается на цепочку, состоящую из первого конденсатора 1 и первого ключа 3, которая осуществляет дельта-модуляцию входного сигнала с частотой, выбранной в соответствии с теоремой Котельникова (фиг. 2в). Преобразованный таким образом сигнал подается через повторитель 5 на блок 6 коммутиру- 30 емых конденсаторов, осуществляющий селекцию синхронных составляющих входного сигнала. При этом на управляющие входы блока 6 подаются сдвинутые друг относительно друга неперекрывающиеся последовательности импульсов (фиг. 2б) с частотами, равными или кратными частоте синхронной составляющей входного сигнала. Эти последовательности импуль- 40 сов в блоке б открывают ключи, через которые происходит заряд конденсаторов входным сигналом. Если сигнал, подаваемый на вход .блока 6, имеет гармонические составляющие с частотами, равными или кратными частоте управляющих блоком 6 импульсов (синхронные составляющие), то в установившемся режиме на конденсаторах блока 6 фиксируются суммарные выборки

50 синхронных составляющих. Асинхронные же составляющие входного сигнала не могут зарядить конденсаторы блока 6, т.к. выборки сигнала происходят в раличные моменты периода асинхронных составляющих, В моменты времени, когда блок 8 выборки и хранения получает управляющие импульсы (фиг ° 2а), на инвертирующий вход алгебраического сумматора 7 подаются выборки синхронных составляющих сигнала, накопленных на конденсаторах блока 6.

На управляющий вход второго ключа 4 подается последовательность коротких импульсов, задержанных относительно управляющих импульсов блока

6 и не перекрывающихся с ними по времени. Длительность этих импульсов меньше, чем импульсов, управляющих блоком 6. За время замкнутого состояния второго ключа 4 происходит заряд второго конденсатора 2 до мгновенного уровня синхронной составляющей, т.к. через второй ключ 4 на второй вывод конденсатора 2 подается за- помненное в блоке 8 значение асинхронной составляющей входного сигнала. Таким образом на неинвертирующем входе алгебраического сумматора 7 в каждый момент времени формируется напряжение, равное сумме асинхронной составляющей входного сигнала и приращения синхронной составляющей входного сигнала за время, прошедшее после заряда второго конденсатора 2.

В момент,. когда блок 8 получает. импульс управления, на инвертирующий вход алгебраического сумматора

7 поступает с блока 6 напряжение, равное приращению синхронной составляющей входного сигнала, а на выходе алгебраического сумматора 7 выделяется только асинхронная составляющая входного сигнала, которая запоминается в блоке 8 и проходит на его выход и, следовательно, на выход синхронного режекторного фильтра. Благодаря дельта-модуляции на входе синхронного режекторного фильтра высоковольтная синхронная помеха получает дополнительное ослабление, а асинхронная составляющая проходит по цепи: второй конденсатор 2, алгебраический сумматор

7, блок 8 практически без ослабления.

Формула изобретения

Синхронный режекторный фильтр, содержащий первый ключ, блок выборки и хранения, выход которого является выходом синхронного режекторного фильтра, последовательно соединенные первый конденсатор, один вывод которого является входом синхронного ре1378017

Составитель Ю. Чернышов

Техред Л. Олийнык Корректор В Гирняк

Редактор М. Циткина

Заказ 889/54 Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 жекторного фильтра, повторитель напряжения, блок коммутируемых конденсаторов и распределитель импульсов, причем первые выходы распределителя импульсов соединены с управляющими входами блока коммутируемых конденсаторов, второй выход распределителя импульсов соединен с управляющим входом блока выборки и хранения, третий 10 выход распределителя импульсов соединен с управляющим входом первого ключа, при этом вход первого ключа подключен к входу повторителя напряжения, отличающийся тем, что, с целью улучшения подавления синхронной составляющей входного сигнала, введены второй конденсатор, второй ключ и алгебраический сумматор, причем первый вывод второго конденсатора соединен с входом синхронного режекторного фильтра, второй вывод второго конденсатора соединен с неинвертирующим входом алгебраического сумматора, выход которого соединен с входом блока выборки и хранения, выход которого через второй ключ соединен с неинвертирующнм входом алгебраического сумматора, инвертирующий вход которого соединен, с выходом блока коммутируемых конденсаторов, выход первого ключа соединен с общей шиной, а управляющие входы первого и второго ключей объединены.