Цифровой управляемый генератор

Иллюстрации

Показать всеРеферат

Изобретение может быть исполь - зовано для построения устройств синхронизации с дискретным управлением. Устройство содержит задающий генератор 1, линию 4 задержки с отводами. мультиплексор 5, элемент 6 задержки и блок 7 управления. В генератор введены управляемьй делитель с дробным коэффициентом деления (ДДКД) 2 и ДДКД 3, каждый из которых включает линию 8 (13) задержки с отводами, мультиплексор 9 (14), элемент 10 (15) задержки и счетчик 12 (16). ДДКД 2 включает помимо этого еще блок 11 добавления-исключения импульсов . Благодаря этому повьшается точность подстройки фазы выходного сигнала генератора .. В описании приведены примеры реализации блока 7 управления, блока 11 добавления-исключения импульсоВ: и счетчика 12 (16). 1 з.п. ф-лы. 4 ил.

СОЮЗ СОВЕТСНИХ

СО1.1ИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4066092/24-21 (22) 05.05,86 (46) 29.02.88. Бюл. У 8 (71) Минский радиотехнический институт (72) С.А.Ганкевич (53) 621.374.5 (088.8) (56) Авторское свидетельство СССР

Ф 644044, кл. Н 04 L 7/02, 17.12.75. (54) ЦИФРОВОЙ УПРАВЛЯЕМЫЙ ГЕНЕРАТОР (57) Изобретение может быть исполь зовано для построения устройств синхронизации с дискретным управлением.

Устройство содержит задающий генератор 1, линию 4 задержки с отводами, „„SU,„, 1378022 А1 (gg 4 Н 03 К 3/64, Н 04 Ь 7/02 мультиплексор 5, элемент 6 задержки и блок 7 управления. В генератор введены управляемый делитель с дробным коэффициентом деления (ДДКД) 2 и

ДДКД 3, каждый из которых включает линию 8 (13) задержки с отводами, мультиплексор 9 (14), элемент 1О (15) задержки и счетчик 12 (16). ДДКД 2 включает помимо этого еще блок 11 добавления-исключения импульсов,Благодаря этому повыщается точность подстройки фазы выходного сигнала генератора. В описании приведены примеры реализации блока 7 управления, блока

1 1 добавления-исключения импульсов и счетчика 12 (16). 1 з.п, ф-лы. 4 ил.

1378022

Изобретение относится к импульсной технике и может быть использовано для построения устройств синхронизации с дискретным управлением.

Целью изобретения является повышение точности подстройки фазы выходного сигнала цифрового управляемого генератора.

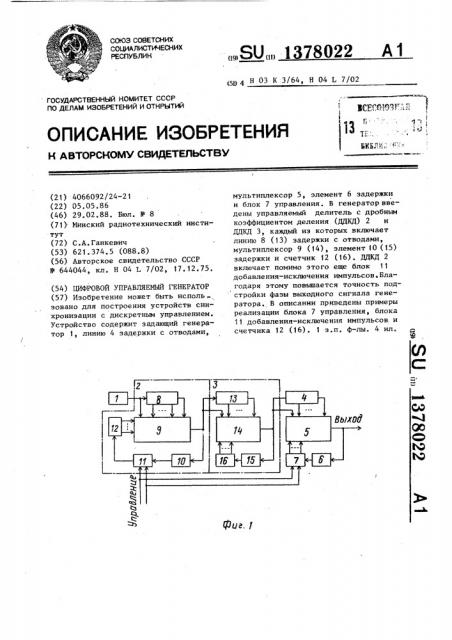

На фиг. 1 представлена функциональная схема цифрового управляемого генератора; на фиг. 2 — блок управления, блок добавления-исключения импульсов, счетчик; на фиг. 3, 4 временные диаграммы работы цифрового управляемого генератора.

Цифровой управляемый генератор (фиг. 1) содержит последовательно соединенные задающий генератор 1, управляемый делитель 2 с дробным ко- 2р эффициентом деления (ДДКД), ДДКД 3, линию 4 задержки с отводами, мультиплексор 5, элемент 6 задержки, блок

7 управления. Вход и отводы линии

4 задержки соединены с сигнальными входами мультиплексора 5, управляющие входы которого подключены к соответствующим выходам блока 7 управления.

Шина управления подключена к входам управления управляемого ДДКД 2 и бло- 3р ка 7 управления.

Управляемый ДДКД 2 (фиг . 1) содержит линию 8 задержки с отводами, мультиплексор 9, элемент 10 задержки, блок 11 добавления-исключения 35 импульсов 11, счетчик 12.

Вход, выход и отводы линии 8 задержки подключены к сигнальным входам мультиплексора 9, а его выход через последовательно соединенные 40 элемент 10 задержки, блок 11 добавления-исключения импульсов 11 соединены с входом счетчика 12, выходы разрядов которого подключены к управляющим входам мультиплексора 9. 45

Вход линии 8 задержки с отводами является входом управляемого ДДКД 2, а выход мультиплексора 9 — его выходом;

Вход управления блока t1 добавленияисключения импульсов 11 является вхо- gp дом управления управляемого ДДКД. 2.

ДДКД 3 (фиг. 1) содержит линию 13 задержки с отводами, мультиплексор

14, элемент 15 задержки и счетчик 16.

Вход, выход и отводы линии 13 задержки подключены к сигнальным входам мультиплексора 14, а его выход через элемент. 15 задержки соединен с входом счетчика 16, выходы разрядов которого подключены к управляющим входам мультиплексора 14. Вход линии

13 задержки с отводами является входом ДДКД 3, а выход мультиплексора

14 — его выходом.

Задающий генератор 1 (фиг. 2) содержит последовательно соединенные генератор 17, стабилизированный кварцем, и формирователь 18, который формирует импульсную последовательность, соответствующую фронтам выходного сигнала генератора 17. Блок 7 управления (фиг. 2) содержит RS-триггеры

19, 20, элементы И-НЕ 21, 22, реверсивный счетчик 23, элемент 24 задержки.

Прямые выходы RS-триггеров 19,. 20 соединены с соответствующими первыми входами элементов И-НЕ 21, 22, вторые входы которых объединены и соединены с входом элемента 24 задержки, выход которого соединен с входами установки RS-триггеров 19, 20. Выходы элементов И-НЕ 21, 22 соединены соответственно с суммирующим и вычитающим входами реверсивного счетчика

23, выходы разрядов которого являются выходами блока 7 управления, Вход элемента 24 задержки является входом блока 7 управления. Входы предустановки RS-триггеров 193 20 являются входами управления блока 7 управления.

Блок 11 добавления-исключения импульсов (фиг. 2) содержит RS-триггеры 25, 26,-элемент И-HE 27, элемент

28 задержки.

Инверсные выходы RS-триггеров 25, 26 и вход элемента 28 задержки соединены с соответствующими входами элемента И-НЕ 27. Выход элемента 28 задержки соединен с входами установки RS-триггеров 25, 26. Прямой выход RS-триггера 25, выход элемента И-ИЕ 27 и вход элемента 28 задержки являются соответственно первым, вторым, третьим выходами блока

11 добавления-исключения импульсов

11. Входы предустановки RS-триггеров

25, 26 являются входами управления блока 11 добавления-исключения импульсов 11.

Счетчик 12 содержит D-триггер 29, элементы И-НЕ 30-32, счетчик 33.

Прямой выход D-триггера 29 соединен с первым входом элемента И-НЕ

31 и является выходом первого разряда счетчика 12. Выходы разрядов счет1378022 чика 33 являются выходами остальных разрядов счетчика 12. Счетный вход

D-триггера 29, входы элемента И-НЕ

30, второй вход элемента И-НЕ 31 являются соответственно первым, вторым, третьим, четвертым входами счетчика 12. Выходы элементов И-НЕ 30, 31 через элемент И-НЕ 32 соединены со счетным входом счетчика 33.

Линии 4, 8, 13 задержки содержат одинаковое число отводов, Число дискретов задержки в линиях равна (К-1) и выбирается в соответствии с заданным значением дискрета подстройки фазы выходного сигнала, величина которого равна для рассматриваемой схемы 2 й/Кв.

Общая задержки каждой из линий равна 20 где t „ — период входного сигнала.

Поскольку периоды входного сигнала для каждой из линий 4, 8, 13 различны, последние должны иметь различную величину задержки.

Цифровой управляемый генератор работает следующим образом. .Импульсная последовательность час-30 тоты задающего генератора 1 (фиг. 1) поступает на вход линии 8 задержки управляемого делителя с дробным коэффициентом деления -2. В зависимости от состояния счетчика 12 один из отводов линии задержки коммутируется

35 на выход мультиплексора 9. Выходной сигнал мультиплексора 9 через элемент 10 задержки и элемент И-НЕ 27 поступает на вход счетчика 12 и увеличивает на единицу число в счетчике.

В результате на выход мультиплексора

9 коммутируется соседний отвод линии задержки, с которого снимается сигнал, задержанный на величину дискэета относительно коммутируемого в предыдущем периоде сигнала.

Таким образом, период выходного сигнала управляемого ДДКД 2 увеличивается на дискрет задержки относительно входного сигнала, т.е. (К-1 ) зг к

55 или (к-1)

f вс зг где t t — соответственно период следования импульсов задающего генератора

1 и период импульсов на выходе управляемого ДДКД 2; соответственно частоуг Вс та импульсов задающего генератора 1и частота импульсов на выходе управляемого

ДДКД 2.

Коррекция фазы выходного сигнала управляемого ДДКД 2 производится под воздействием импульсов управления, поступающих на управляющие входы блока 11 добавления-исключения импульсов 11. При коррекции фазы на опережение импульс подается на вход RSтриггера 26 (фиг. 2) и переводит его в состояние "1". Низким уровнем напряжения с инверсного выхода RS-триггера 26 закрываются элементы И-НЕ 27, 31, в результате чего очередной импульс с выхода мультиплексора 9 не проходит на вход счетчика 12 и код последнего не изменяется. Восстановление первоначального состояния RSтриггера 26 производится выходным импульсом мультиплексора 9, задержанным на его длительность элементом 28 задержки.

При коррекции фазы выходного сигнала управляемого ДДКД 2 на отставание управляющий импульс поступает на вход RS-триггера 25, который перебрасывается в состояние " 1". В результате этого на вход элемента И-НЕ

30 подается сигнал разрешения, а на вход элемента И-НЕ 27 — сигнал запрета, Очередной импульс с выхода мультиплексора 9 через элемент 10 задержки, элементы И-НЕ 30, 32 поступает непосредственно на вход второго разряда счетчика 12, что соответствует записи в счетчик двух импульсов.

Задержанный элементом 28 задержки импульс восстанавливает первоначальное состояние триггера 25.

Элементы 6, 10 задержки предотвращают подачу на выход мультиплексоров

5, 9 в течение одного периода входного сигнала двух импульсов с двух соседних отводов линий задержки при коррекции фазы на отставание. Величина задержки определяется из условия

1378022 где п„ вЂ” период входного сигнала; ь„ — длительность входного сигнала;

K.<, — сумма задержек элемента

6 (10), элемента И-НЕ 21 (27), счетчика 23 (12) (фиг. 2).

На выходе ДДКД 3 формируется сигнал частоты Е . Период выходного IO

Ьь1 сигнала меньше периода вспомогательного сигнала, поступающего на вход

ДДКД 3, на величину дискрета задержки линии 13 задержки. Дробное деление входного сигнала производится, как и 1-5 в управляемом ДДКД 2, за счет коммутации отводов линии 13 задержки выходным сигналом мультиплексора 14, поступающим на вход счетчика 16 через элемент 15 задержки. Поскольку 20 подключенного к выходу отвода линии

13 задержки должен сниматься сигнал с опережением, управляющий код подается на мультиплексор 14 с инвертированных выходов разрядов счет- 25 чика 16. Элемент 15 задержки обеспечивает задержку выходного сигнала мультиплексора на его длительность.

Выходной сигнал ДДКД 3 поступает на вход линии 4 задержки. С помощью 30 линии 4 задержки, мультиплексора 5, элемента 6 задержки и блока 7 управления производится коррекция фазы выходного сигнала на величину дискрета 2п/К в сторону, противополож35 ную осуществляемой в управляемом

ДДКД 2 под воздействием сигнала управления. Под действием импульса управления триггер 19 (фиг. 2 при коррекции фазы на отставание) или триггер 20 (при коррекции на опережение) переводится в состояние "1" и выходной сигнал через элемент задержки 6, элемент И-НЕ 21 (22) поступает на вход реверсивного счетчика и изменяет его состояние. На выход цифрового управляемого генератора коммутируется соседний отвод линии задержки 4, при этом фаза выходного сигнала изменяется на дискрет подстройки 2ii/К, 50 а с учетом коррекции (одновременной) на входе — на дискрет подстройки, равный 2п/Kç

Временные диаграммы (фиг, 3, 4) иллюстрируют процесс коррекции фазы выходного сигнала в цифровом управляемом генераторе.

При коррекции фазы выходного сигнала на опережение фаза сигнала задающего генератора 1 с помощью управляемого ДДКД 2 корректируется на отставание (фиг. 3), при этом положение импульса (фиг. 3 a) изменяется на величину t „ /К и соответствует моменту-t что приводит к изменению временного положения вспомогательного сигнала (фиг, 3 б) и выходного сигнала.(фиг. 3 в). Следующий импульс задающего генератора 1 сформируется в момент t, вспомогательного сигнала — в момент t, а выходного сигнала — в момент . Одновременная коррекция временного положения (фазы) выходного сигнала на опережение на величину „,„/К приводит к тому, что очередной импульс выходного сигнала занимает положение t . Таким образом, коррекция, фазы выходного сигнала на опережение составляет величину 2 /К .

При коррекции фазы выходного сигнала на отставание (фиг. 4) фаза сигнала задающего генератора 1 коррек тируется на опережение, а фаза выходного сигнала — на отставание.

Формула изобретения 1 . Цифровой управляемый генератор, содержащий задающий генератор, линию задержки е отводами, вход и отводы которой соединены с сигнальными входами мультиплексора, элемент задержки, выход которого соединен с входом блока управления, управляющие входы которого соединены с шиной управления, а выходы блока управления— с управляющими входами мультиплексора, отличающийся тем, что, с целью повьппения точности подстройки фазы выходного сигнала, введены последовательно соединенные управляемый делитель с дробным коэффициентом деления и п делителей с дробным коэффициентом деления, причем вход управляемого делителя с дробным коэффициентом деления соединен с выходом задающего генератора, а входы управления соединены с шиной управления, выход последнего из и делителей с дробным коэффициентом деления соединен с входом линии задержки с отводами.

2. Генератор по п. 1, о т л и— ч а ю шийся тем, что управляемый делитель с дробным коэффициентом

1378022 деления содержит линию задержки с отводами, мультиплексор, элемент задержки, блок добавления-исключения импульсов, счетчик, причем вход и отводы линии задержки с отводами соединены с сигнальными входами мультиплексора, выход которого через последовательно соединенные элемент задержки и блок добавления-исключения импульсов соединен с входом счетчика, выходы разрядов которого подключены к управляюцим входам мультиплексора, выход которого является выходом управляемого делителя с дробным коэф5 фициентом деления, вход линии задержки с отводами является входом управляемого делителя с дробным коэффициентом деления, вход управления блока добавления-исключения импульсов является входом управления управляемого делителя с дробным коэффициентом деления.

1378022

Составитель Ю.Сибиряк

Редактор М.Циткина Техред Л.Олийнык Корректор Н,Король

Заказ 889/54 Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 13035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4