Кодек адаптивного дельта-модулятора

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике. Его использование в системах передачи данных позволяет упростить кодек и повысить точность преобразования за счет расширения динамического диапазона . Кодек адаптивного дельта-модулятора содержит компаратор 1, триггер 2, анализатор 3 перегрузки, интегратор 5, источник 6 тока, усилитель 7 и переключатели 9, 10. Благодаря введению генератора 4 сигнала компандиррвания, источника 8 опорного напряжения и переключателей 11 и 12 коэффициент усиления усилителя 7 изменяется так же, как и аппроксимирующий сигнал, что обеспечивает расширение динамического диапазона. 1 з.п. ф-лы, 2 ил.

СО}ОЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)4 Н 03 М 3/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

77 Ц 1 18

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4076364/24-24 (22) 09.06,86 (46) 29. 02 ..88. Бюл, 11 - 8 (71) Московский инженерно-физический институт (72) А. В . Алюшин и М, В. Алюшин (53) 621.376.56(088.8) (56.) ТИИЭР, !974, т. 62, У 5, с. 97, рис, 21.

Патент США !! 4123709, кл. Н 03 К 13/22, опублик. 1978. (54) КОДЕК АДАПТИВНОГО ДЕЛЬТА-МОДУЛЯТОРА (57) Изобретение относится к автоматике и вычислительной технике. Его использование в системах передачи

„„SU,„, 1378063 А1 данных позволяет упростить кодек и повысить точность преобразования за счет расширения динамического диапазона. Кодек адаптивного дельта-модулятора содержит компаратор 1, триггер 2, анализатор 3 перегрузки, интегратор 5, источник 6 тока, усилитель 7 и переключатели 9, 10. Благодаря введению генератора 4 сигнала компандирования, источника 8 опорного напряжения и переключателей 11 и 12 коэффициент усиления усилителя

7 изменяется так же, как и аппроксимирующий сигнал, что обеспечивает расширение динамического диапазона.

1 э.п, ф-лы, 2 ил.

1378063

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах передачи данных.

Цель изобретения " упрощение кодека и повышение точности преобраэо" вания эа счет расширения динамического диапазона.

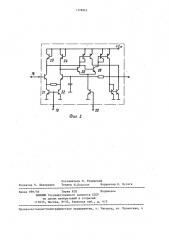

На фиг. 1 приведена функциональная схема кодека адаптивного дельтамодулятора; на фиг. 2 - пример выполнения усилителя.

Кодек адаптивного дельта-модулятора содержит (фиг. 1) компаратор 1,триг-15 гер 2,анализатор 3 перегрузки, генератор 4 сигнала компандирования, интегратор 5, источник 6 тока, усилитель 7, источник 8 опорного напря.жения и первый — четвертый переклю" чатели 9-12. На фиг, 1 обозначены аналоговый 13 и цифровой 14 входы, вход 15 синхронизации, цифровой 16 и аналоговый 17 выходы 16, 1? а также информационный и первый и вто- 25 рой управляющие входы 18-20 усилителя 7.

Анализатор 3 перегрузки служит для регистрации появления в дельта" модулированном сигнале наперед заданного числа (обычно 3-4} идущих подряд единиц или нулей.

Генератор 4 сигнала компандирования обеспечивает регулировку шага квантования в зависимости от скорос- 35 ти изменения аналогового сигнала.

Источник 6 тока служит для регу- лировки тока заряда интегратора 5 с учетом знака дельта-модулированного сигнала. Усилитель 7 (фиг. 2) выпол- 40 нен в виде перемножителя аналоговых сигналов.

Кодек адаптивного дельта-модулято" ра работает следующим образом.

В случае, когда переключатели 912 поставлены в указанные на фиг. 1 положения, т.е. первый переключатель 9 соединяет с выходом свой первый вход, второй переключатель 10второй вход, третий переключатель

11 коммутирует свой вход с первым выходом, а четвертый переключатель

12 " с вторым выходом, кодек работа" ет в режиме модулятора. При переводе переключателей 9-12 в другое положение кодек работает в режиме демодулятора.

В режиме модулятора входной сигнал с входа 13 устанавливается в усилителе 7 и поступает на прямой вход компаратора 1 ° На инверсный вход компаратора 1 подается аппроксимирующее напряжение, сформированное на интеграторе 5, Результат сравнения компаратора 1 s момент прихода синхросигнала с входа 15 записывается в триггер 2, который определяет знак приращения аппроксимирующего напряжения.

При большой скорости нарастания входного сигнала аппроксимирующее напряжение не успевает его отслеживать. В выходной последовательности модулятора появляются пачки импульсов одного знака. Когда длитель" ность этих пачек достигает 3, на вы" ходе анализатора 3 появляется высокий потенциал, что приводит к заряду емкости генератора 4 и увеличению выходного тока на его первом входе.

Ток интегратора 5, задаваемый источником 6 тока, увеличивается, следовательно, увеличивается и приращение аппроксимирующего налряжения. Таким образом, осуществляется адаптация модулятора под входной сигнал.

При уменьшении входного сигнала пачки импульсов одного знака исчезают, что приводит к уменьшению величины аппроксимирующего напряжения.

Выходной сигнал снимается с выхода

16.

В режиме демодулятора входной цифровой сигнал поступает на вход

14, а выходной декодированный сигнал снимается с выхода 17.

Работа усилителя 7, управляемого тем же самым сигналом, что и интег" ратор, приводит к тому, что сигнал, поступающий на компаратор 1, имеет более узкий амплитудный диапазон, что позволяет уменьшить чувствительность компаратора 1 и снизить требования к интегратору 5, использо" вать более простую схемотехнику и снизить протребляемую мощность. При сохранении чувствительности компаратора 1 на прежнем уровне предлагаемый кодек воспринимает и обрабатывает входные сигналы в значительно большем амплитудном диапазоне.

Достоверность передачи речи увеличивается, так как одновременное управление усилителем 7 и интегратором 5 приводит к реализации нелиней1378063 ного закона компандиро вания в э ави" симости от выходного тока генератора 4.

При увеличении выходного тока генератора 4 в 2 раза относительное

5 изменение приращения аппроксимирующего напряжения по отношению к сигналу на выходе усилителя 7 состав" ляет 4 раза, что позволяет обрабатывать резкие изменения речевого сигнала с меньшей ошибкой, при меньшем сигнале перегрузки, т.е. с большей достоверностью.

Работа усилителя 7 в случае реализации его в виде перемножителя аналоговых сигналов (фиг. 2) проис" ходит следующим образом.

При изменении коллекторных токов транзисторов 21 и 22 пропорционально току генератора 4 на входе

19 коэффициент усиления первого кас" када и всего усилителя 7 изменяется обратно пропорционально величине этих токов за счет изменения величины сопротивления перегрузки первого каскада (транзисторы 23 и 24 в диодном включении).

В режиме декодирования, когда ток управления подается на вход 20 усилителя 7, коэффициент усиления первого каскада постоянен, а коэф" фициент усиления второго каскада на транзисторах 25 и 6 изменяется пря" мо пропорционально току управления, что обеспечивает восстановление ис" ходного сигнала на выходе 17 кодека.

Таким образом, кодек адаптивного дельта-модулятора имеет простое выполнение и обладает большим ампли40 тудным диапазоном передаваемых сигналов, что обеспечивает более высокую достоверность восстановления ре" чи.

Формула изобретения

1. Кодек адаптивного дельта-моду- лятора, содержащий первый переключатель, первый вход которого являет" ,ся аналоговым входом кодека, выход, соединен с информационным входом усилителя, компаратор, второй переключатель, первый вход которого является цифровым входом кодека, триггер, вход синхронизации которого является входом синхронизации кодека, прямой выход триггера соединен с первым информационным входом анализатора перегрузки и является цифровым выходом кодека,,источник тока, выход которого через интегратор подключен к инверсному входу компаратора и второму входу первого переключателя, отличающийся тем, что, с целью упрощения кодека и повышения точности преобразования за счет расширения динамического диапазона, в кодек введены генера" тор сигнала компандирования, третий и четвертый переключатели и источник опорного напряжения, выход усилителя соединен с прямым входом компаратора и является аналоговым выходом кодека, выход компаратора соединен с вторым входом второго переключателя, выход которого соединен с инфор" мационным входом триггера, первый вход источника тока подключен к прямому выходу триггера, инверсный выход которого соединен с вторым входом источника тока и вторым информационным входом анализатора перегрузки, вход синхронизации которого подключен к входу синхронизации кодека, выход анализатора перегрузки соединен с входом генератора сигнала компандирования, первый и второй выходы которого подключены соответственно к третьему входу источника тока и входу четвертого переключателя, выход источника опорного напряжения соединен с входом третьего переключателя, первый и второй выходы которого объединены с одноименными выходами четвертого переключателя и подключены к одноименным управляющим входам усилителя.

2. Кодек по п. 1, о т л и ч аю шийся тем, что усилитель выполнен в виде перемножителя аналоговых сигналов.

1378063

Составитель О. Ревинский

Техред И.Попович Корректор В. Бутяга

Редактор Т. Лазоренко

Заказ 896/56 Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4