Устройство для передачи и приема дискретной информации

Иллюстрации

Показать всеРеферат

. Изобретение относится к электросвязи и повьшает скорость передачи. Устр-во содержит передатчик 1, канал 2 связи, входной усилитель 3, синхронизатор 4, перемножитель 6, интеграторы 7, г-р 10 сетки частот, счетчик 12, запоминающий блок t3, блок 14 вычисления разности фаз, решающий блок 15. Вновь введены многополюсный перестраиваемый режекторный фильтр 5 и коммутаторы 8 и 9. Фильтр 5 состоит из усилителя, перестраиваемого режекторного фильтра, блока задержки и сумматора. 1 з.п. ф-лы, 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)4 Н 04 1. 27/26

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ/ СВИДЕТЕЛЬСТВУ

РЯ 1 ьФ 1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4019737/24-09 (22) 05.02 ° 86 (46) 29.02.88. Бюл. В 8 (71) Научно-исследовательский институт автоматизированных систем планирования и управления в строительстве (72) О.Н. Чепорнюк, А.М. Куприенко, А.В. Гирнык и М.Л. Цыбулевский (53) 621.396.6(088.8) (56) Авторское свидетельство СССР

У 559410, кл, Н 04 L 3/10, 1978. (54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕИА ДИСКРЕТНОЙ ИНФОРИАЦИИ. SU„„1378082 А 1 (57). Изобретение относится к электросвязи и повышает скорость передачи.

Устр-во содержит передатчик 1, канал

2 связи, входной усилитель 3, синхронизатор 4, перемножитель 6, интеграторы 7, г-р 10 сетки частот, счетчик

12, запоминающий блок 1.3, блок 14 вычисления разности фаз, решающий блок 15. Вновь введены многополюсный перестраиваемый режекторньФ фильтр 5 и коммутаторы 8 и 9. Фильтр 5 состоит из усилителя, перестраиваемого режекторного фильтра, блока задержки и сумматора. 1 з.п. ф-лы, 2 ил.

1378082

Изобретение относится к электросвязи и может использоваться для передачи данных сигналами с фаэочастотной модуляцией.

Цель изобретения — повышение скорости передачи.

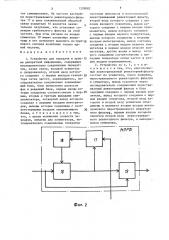

На фиг. 1 изображена структурная электрическая схема предлагаемого устройства; на фиг. 2 — структурная электрическая схема многополюсного перестраиваемого режекторного фильтра.

Устройство для передачи и приема дискретной информации содержит передатчик 1, канал 2 связи, входной усилитель 3, синхронизатор 4, многополюсный перестраиваемый режекторный фильтр (МПРФ) 5, перемножитель б, интеграторы 7, коммутаторы 8 и 9, гене- 20 ратор 10 сетки частот,- генератор 11 тактовых импульсов, счетчик 12, запоминающий блок 13, блок 14 вычисления разности фаз, решающий блок 15.

Многополюсный перестраиваемый ре- 25 жекторный фильтр 5 состоит из усилителя 16, перестраиваемого режекторного фильтра 17, блока 18 задержки и сумматора 19.

Устройство работает следующим .об- 30 разом.

Поступающая в передатчик 1 дискретная информация распределяется по каналам, в каждом из которых осуществляется дискретная фаэовая модуляция несущих с частотами КйР (К вЂ” целое число, а dP — интервал частот между несущими). Модулированные несущие суммируются и передаются по каналу

2 связи. 40

В приемнике с помощью входного усилителя 3 устанавливается уровень сигнала, необходимый для нормальной работы последующих блоков. Групповой сигнал с выхода входного усилителя 3 45 поступает на МПРФ 5 для разделения канальных несущих. Выделенные значения несущих каждого канала следуют циклически друг за другом последовательно во времени. Вычисление разности фаз между принимаемыми и опорны50 ми сигналами производится с помощью корреляторов, перемножение сигналов по каждому каналу производится общим перемножителем 6, а интегрирование

55 в каналах производится соответствующими интеграторами 7. Для этого тактовый генератор 11 вырабатывает импульсы, период следования которых много меньше длительности единичного элемента сигнала. Эти импульсы циклически изменяют состояние счетчика 12 сигналы которого одновременно изменяют состояние МПРФ 5 и коммутаторов 8 и 9. При этом, если на очередном тактовом интервале с МПРФ 5 на один вход перемножителя б поступает сигнал канала с номером i то ко второму его входу коммутатор 9 подключает опорный сигнал с тем же номером i а сигнал с выхода перемножителя 6 подается с помощью коммутатора 8 на интегратор

7 с тем же номером i.На следующем тактовом интервале код счетчика увеличивается на 1, изменяются состояния

МПРФ 5 и коммутаторов 8 и 9, и на перемножитель 6 подаются сигналы следующего выделяемого канала и опорного колебания. Одновременно к выходу перемножителя 6 коммутатор 8 подключает следующий интегратор 7. Таким образом,, этот процесс многократно повторяется циклически ча протяжении длительности единичного элемента сигнала, в конце которого значения напряжений с выходов интеграторов 7 записываются в запоминающий блок 13 по сигналам, поступающим из синхронизатора 4.

Полученные при обработке двух соседних единичных элементов сигнала и записанные в запоминающем блоке 13 напряжения поступают на блок 14 вычисления разности фаз для относительного декодирования. По результатам вычислений блока 14 решающий блок 15 принимает решение о переданных символах и выдает принятую информационную последовательность получателю.

МПРФ 5 работает следующим образом.

Входной сигнал поступает на входы сумматора 19 и усилителя 16, образующего вместе с включенными в цепь по= ложительной обратной связи перестраиваемым режекторным фильтром 17 и блоком задержки 18 гребенчатый фильтр.

На частотах селекции гребенчатого фильтра ы„ = К2и/Т (где К = 1,2,3....-. а Т вЂ” дпительность задержки) сигналы на входы сумматора 19 поступают в противофазе и при коэффициенте передачи гребенчатого фильтра, равном единице, выходное напряжение сумматора

19 на этих частотах практически равно нулю. На других частотах фазовые соотношения между сигналами на входе сумматора 19 изменяются и на его выходе присутствует ненулевой резуль1378082 тат суммирования. На частоте настройки перестраиваемого режекторного фильтра 17 в цепь положительной обратной связи усилителя 1б вносится значи5 тельное затухание, что устраняет селекцию гребенчатого фильтра на этой частоте. При этом сигналы на входах сумматора 19 имеют различные амплитуды и это позволяет выделить из груп-(0 пового сигнала колебание только одной частоты.

Формула изобретения

1. Устройство для передачи и прие- 15 ма дискретной информации, содержащее последовательно соединенные передатчик, канал связи, входной усилитель и синхронизатор, второй вход которого соединен с первым выходом генера- 20 тора сетки частот, перемножитель, последовательно соединенные запоминающий блок, блок вычисления разности фаз и решающий блок, первые входы которых соединены соответственно с пер- 25 вым, вторым и третьим выходами синхронизатора, четвертый выход которого соединен с первыми входами интеграторов, выходы которых соединены с соответствующими входами запоминающего 3Q блока, о т л и ч а ю щ е е с я тем, что, с целью повышения скорости передачи, введены два коммутатора, последовательно соединенные генератор тактовых импульсов и многополюсный перестраиваемый режекторный фильтр, второй вход которого соединен с выходом входного усилителя, выход которого соединен с первым входом перемножителя, выход которого соединен с первым входом первого коммутатора, выходы которого соединены с вторыми входами интеграторов, выход счетчика соединен с вторым входом первого коммутатора и первым входом второго коммутатора, другие входы и выход которого соединены соответственно с выходами генератора сетки частот и вторым входом перемножителя.

2, Устройство по п. 1 о т л ич а ю m е е с я тем, что, многополюсный перестраиваемый режекторный фильтр состоит из усилителя, блока задержки, перестраиваемого режекторного фильтра и сумматора, выход усилителя через последовательно соединенный перестраиваемый режекторный фильтр и блок задержки соединен с первым входом усилителя, выход которого соединен с первым входом сумматора, второй вход которого и второй вход усилителя объединены и являются вторым входом многополюсного перестраиваемого режекторного фильтра, первым входом которого является второй вход перестраиваемого режекторного фильтра, а выходом— выход сумматора.