Устройство для сложения в избыточной двоичной системе счисления

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики и вычислительной техники. Цель изобретения - упрощение устройства и увеличение его быстродействия. Устройство для сложения в избыточной двоичной системе счисления содержит первый, второй, третий, четвертый информационные входы 1, 2, 3, 4, три элемента задержки 5, 6, 7, блок 8 формирования промежуточного результата , блок 9 формирования окончательного результата, выходы 10, 11 результата устройства. 2 ил, 2 табл..

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (192 (112 (5124 G 06 F 7 49 и»(l

%»

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4021696/24-24 (22) 12.02.86 (46) 15.03.88. Бюл. Ф 10 (71) Кировский политехнический институт (72) С.И.Гаврилин (53) 681.325.5 (088.8) (56) Авторское свидетельство СССР

В 997032, кл. G 06 F 7/49, 1981 °

Авторское свидетельство СССР

У 717763, кл. G 06 F 7/49, 1977. (54) УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ В ИЗБЫТОЧНОЙ ДВОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ (57) Изобретение относится к области, автоматики и вычислительной техники.

Цель изобретения — упрощение устройства и увеличение его быстродействия.

Устройство для сложения в избыточной двоичной системе счисления содержит первый, второй, третий, четвертый информационные входы 1, 2, 3, 4, три элемента задержки 5, 6, 7, блок

8 формирования промежуточного результата, блок 9 формирования окончательного результата, выходы 10, 11 результата устройства. 2 ил, 2 табл., 1381487 ставляется при этом двумя двоичными

+ цифрами Х и Хр. к

Х=,хр г . (3)

Х =Х -Х

Р P P где Xp — р-й разряд;

Х вЂ” положительная цифра р-го

P разряда;

Х вЂ” отрицательная цифра р-го

P разряда.

Кодирование значений избыточного разряда можно свести в табл. 1. (4) 15

Таблица 1

1 t

Хр

+1

Т а б л и ц а 2

Варианты подключения устройства

Первый

Второй

Входы и выходы устройства I 2 4 3 10 11 1 2 4 3 10 11

X Х У У M M Х Х У У M М

Шины операндов

Процесс алгебраического суммирования М = х + у для каждого р-го разряда представляется формулами

2П, — С

Ф

М, -2М

Xp Xp + Yp (1 ) и, — с, — У, (2) Изобретение относится к вычислительной технике и может быть использовано в вычислительных машинах и устройствах, работающих в избыточной

5 двоичной системе счисления с цифрами

1, О, 1.

Цель изобретения — упрощение устройства и увеличение его быстродействия. 10

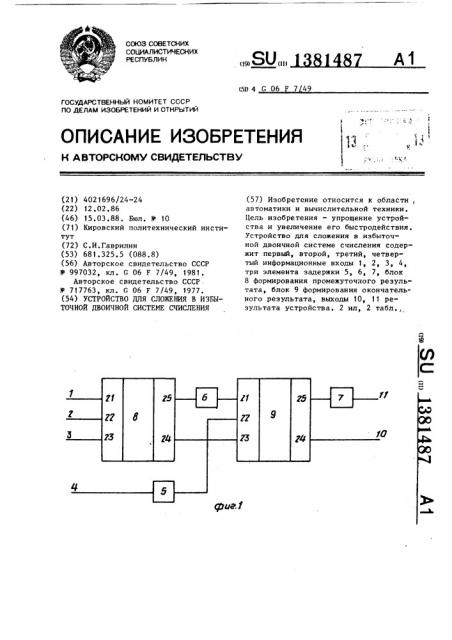

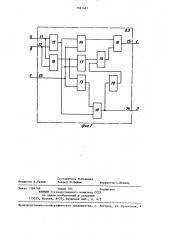

На фиг. 1 изображена функциональная схема предлагаемого устройства, на фиг. 2 — блок формирования промежуточного результата и блок формирования окончательного результата.

Устройство содержит (фиг.1) первый 1, второй 2, третий 3 и четвертый 4 информационные входы, три элемента 5-7 задержки, блок 8 формирования промежуточного результата, блок

9 формирования окончательного результата, первый 10 и второй 11 выходы результата.

Блок 8 формирования промежуточного результата и блок 9 формирования 25 окончательного результата выполнены в виде одноразрядных сумматоров, каждый иэ которых содержит четыре элемента И 12-15, четыре элемента

ИЛИ 16-19, элемент НЕ 20, первый 21 3р и второй 22 информационные входы одноразрядного сумматора, вход 23 переноса одноразрядного сумматора и выходы 24 и 25 соответственно переноса и суммы одноразрядного сумматора.

Устройство работает следующим образом.

Любое К-разрядное нормализованное число Х в избыточной двоичной системе счисления можно передавать 4п последовательно от старших разрядов б к младшим по шинам Х и Х, причем каждый разряд Х этого числа предP

Для сложения двух чисел М = х+у в избыточной системе счисления они подаются последовательно, начиная со старших разрядов, на входы 1-4 устройства, при этом на выходах 10 и

11 в той же последовательности от старших разрядов к младшим формируются разряды результата в той же системе счисления., Возможны два варианта подключения операндов к устройству, приведенные в табл. 2, при этом работа устройства идентична для обоих случаев подключения, поэтому далее рассматривается второй вариант.

1381487 где М, Мр, У, Yp„Х 1 Х двоичные цифры операндов; двоичная цифра промежуточной суммы р-ro разряда цифра переноса в р-й разряд.

В формулах (1) и (2) переменные правых частей имеют одинаковый вес, l они поступают на входы блоков 8 и 9.

Переменные Пр 1 в левой части (1) и

М, в левой части (2) имеют удвоенный вес, на что указывает множитель

2. Для согласования веса переменной с временем ее поступления на вход формирователя служат элементы 5-7 задержки. Блоки 8 и 9 служат для выполнения алгебраического сложения вводных переменных в соответствии с формулами (1) и (2) .

На входы 1-4 поступают операнды

Х, Х, У,, У соответственно ° В блоках 8 и 9 вычисляются на каждом р-ом такте значения промежуточных и окончательных результатов. С выхода 25 блока 8 на вход элемента 6 задержки поступает значение промежуточной суммы С, с выхода 24 того же блока на вход 23 блока 9 поступает

+ сигнал переноса П,, с выходов элементов 5 и 6 задержки на входы 21 и

22 блока 9 поступают соответственно сигналы У и С

После окончания переходных процессов в схеме блока 9 на р-ом такте на выход 10 устройства поступает значение результата М с выхода

Ф

25, а значение результата М р, с выхода 24 поступает на вход элемента

7 задержки, с выхода которого на выход 11 устройства поступает значе+ ние результата М . Сложение двух

1О

К-разрядных чисел выполняется эа (К+2) такта работы.

Формула изобретения

Устройство для сложения в избыточной двоичной системе счисления, содержащее блок формирования промежуточного результата блок формиров.— ния окончательного результата и три элемента задержки, причем первый, второй, третий информационные входы устройства соединены соотве;ственно с первым, вторым, третьим информационными входами блока формирования промежуточного результата, первый выход которого соединен через первый элемент задержки с первым информационным входом блока формирования окончательного результата, второй информационный вход которого через второй элемент задержки соединен с четвертым информационным входом устройства, второй выход блока формирования промежуточного результата соединен с третьим информационным входом блока формирования окончательного результата, первый выход которого соединен с входом третьего элемента задержки, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства и повышения его быстродействия, блоки формирования промежуточного и окончательного результатов содержат по одному одноразрядному двоичному сумматору, причем входы первого и второго операндов и переноса каждого из одноразрядных двоичных сумматоров являются соответственно первым, вторым и третьим входами соответствующего блока, а выходы суммы и переноса— соответственно первым и вторым выходами соответствующего блока, выход третьего элемента задержки и второй выход блока формирования окончательного результата являются выходами устройства.

1381487 фО Я

Составитель М.Есенина

Техред М.Дидык Корректор С.Шекмар

Редактор А.Ревнн

Заказ 1184/44 Тирах 704 Подписное

ВНИИПИ Государственного коиитета СССР по делам изобретений и открытий

113035, Москва, Ж-35,.Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4