Устройство для контроля логических схем

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики и вычислительной техники и м.б. использовано для контроля логических схем. Цель изобретения - повышение достоверности контроля. Устройство содержит генератор тестов J, регистр теста 2, группу ЦАП 3, схемы сравнения 4,25, контролируемую схему 5, вычитатель 6, блок синхронизации 7, блок индикации 8, блок хранения эталона 9, регистр входов-выходов 10, коммутатор входов-выходов 11, шинные формирователи 16, регистр маски 17, генератор 18, группы элементов И 19,21, группу счетчиков 20, группу формирователей импульсов, регистр эталонных временных интервалов 24, группу элементов задержки 26. 4 ил. (Л 00 00 ел

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТ 1ЧЕСНИХ

РЕСПУБЛИН

„„SU„„ 1 381517 А1 (51)4 G 06 F ll/26

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АBTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4159835/24-24 (22) 11.09,86 (46) 15,03.88. Бюл. h- 10 (7l) Калининградский технический институт рыбной промышленности и хозяйства (72) II ° 3.Þñóïîâ, А.H.Øëåìèí и А.Н.Румянцев (53) 681.3(088 ° 8) (5e) Авторское свидетельство СССР

lI 498619, кл. 06 F 11/00, 1974 °

Авторское свидетельство СССР

М 1003090) кл. .": 06 1 ll/16, 1981 ° (54) УСТРОЙСТВО Д11Я КОНТРОЛЯ ЛОГИЧЕСКИХ СХЕМ (57} Изобретение относится к области автоматики и вычислительной техники и м ° б. использовано для контроля логических схем. Цель изобретения — повышение достоверности контроля. Устройство содержит генератор тестов 1, регистр теста 2, группу ЦАП 3, схемы сравнения 4,25, контролируемую схему 5, вычитатель 6, блок синхрониэа" ции 7, блок индикации 8, блок хранения эталона 9, регистр входов-выходов 10, коммутатор входов-выходов ll, шинные формирователи !6, регистр маски 17, генератор 18, гругпы элементов И 19,21, группу счетчиков 20, группу формирователей импульсов, регистр эталонных временных интервалов 24, группу элементов задержки 26.

4 ил.

1381517

Изобретение относится к вычислительной технике, а именно к устройствам для контроля логических схем.

Цель изобретения — повышение дос5 товерности контроля.

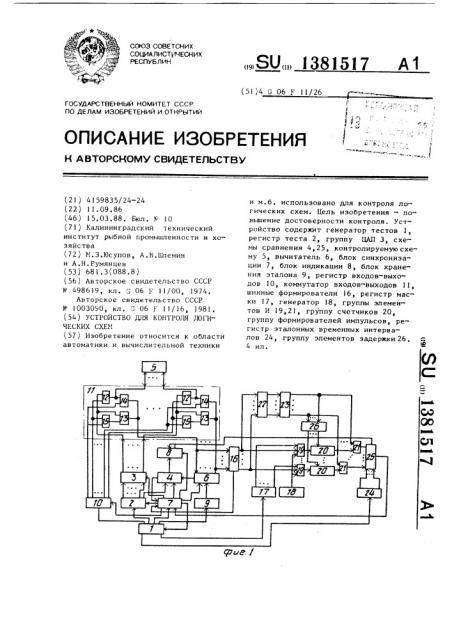

На фиг.l показана схема устройства для контроля; на фиг.2 — схема блока управления; на фиг,3 — временная диаграмма работы устройства; на фиг.4 -!0 временная диаграмма работы блока управления.

Устройство (фиг.)) содержит генератор 1 тестов, регистр 2 теста, группу цифроаналоговых преобразовате- !5 лей Э, вторую схему 4 сравнения, контролируемую схему 5,вычитатель 6, блок 7 синхронизации, блок 8 индикации, блок 9 хранения эталонов, регистр 10 входов-выходов, коммута- 2р тор 11 входов-выходов, элементы 12-14 с третьим состоянием, элемент ИЛИНЕ 15, шинные формирователи 16, регистр 17 маски, генератор 18 синхроимпульсов, первую группу элементов 25

И 19, группу счетчиков 20, вторую группу элементов И 21, группу формирователей импульсов образованную из группы элементов HE 22 и группы дифференцирующих элементов 23,регистр 24 30 эталонных временных интервалов, первую схему 25 сравнения, группу элементов 26 задержки, Блок управления (фиг.2) содержит элемент 27 задержки, элемент И 28, элемент НЕ 29, счетчик 30, элемент

HE 3!, элемент ИЛИ-НЕ 32, элемент

И 33, триггер 34, элемент ИЛИ-НЕ 35, семь элементов НЕ 36, кнопка 37 начальной установки, дешифратор 38, 40 дифференцирующий элемент 39.

Генератор тестов предназначен для введения информации, необходимой для анализа схемы 5. Регистр 2 предназначен для хранения и выдачи на бло- 45 ки 3 и 4 необходимой информации в дискретной форме для анализа схемы 5, Группа цифро-аналоговых преобразователей 3 предназначена для преобразования информации, поступающей с регистра 2 в дискретной форме, и выдачи ее в виде сигналов в аналоговой форме через коммутатор 1) на контролируемук схему 5 или входы вычитателя 6 и формирователи 16.

Схема 4 сравнения предназначена для сравнения сигналов в дисКретной форме, поступающих с вычитателя 6 и регистра 2, с которого задается эталонный результат, а также выдачи результатов сравнения в блоки 7 и 8.

Вычитатель 6 предназначен для анализа сигналов в аналоговой форме, поступающих с коммутатора ll путем сравнения их с эталонами верхних и нижних параметров, поступающими с блока 9 хранения эталонов, а также преобразования сигналов аналоговой формы, поступающих с выходов коммутатора )1, в сигналы дискретной формы, выдаваемые в схему 4 сравнения, Блок 7 синхронизации вырабатывает управляющие сигналы и синхронизирует работу всего устройства в зависимости от сигналов, поступающих на него с блоков l 4,è 25. Блок 8 индикации предназначен для индикации результатов сравнения. Блок 9 хранения эталонов предназначен для хранения верхних и нижних пределов параметров в соответствии с требованиями, предъявляемыми к параметрам контролируемой схемы 5.

Регистр 10 предназначен для хранения и выдачи на коммутатор I! информации о входах-выходах схемы 5, Коммутатор l) предназначен для коммутации входов-выходов схемы объекта 5, Если на управляющие входы коммутатора 11 проходит код (01) с выходов регистра 10, элемент 12 открывается, а элементы 13 и 14 закрываются. Контрольные сигналы с выхода регистра 2 через преобразователь 3 ,поступают на вход контролируемой схемы 5, Если на управляющие входы коммутатора приходит соответствующая комбинация (10) с выхода регистра 10, элементы 12 и 13 закрыты и открыт элемент 14. Сигнал данного выхода контролируемой схемы поступает через элемент )4 на вход вычитателя 6 и формирователи 16, Если на управляющие входы коммутатора 11 приходит соответствующая комбинация (00), выходной сигнал элемента ИЛИ-HE 15 открывает элемент 13 а управляющие сигналы регистра 10 закрывают элементы 12 и !4, Тестовые сигналы с выхода регистра 2 через преобразователь 3 поступают на преобразователь 6 и формирователи 16 и обеспечивается пассивный режим коммутации устройства с контролируемым объектом, что позволяет достигнуть логической гибкости, возможности контроля параметров логической схемы по

1381517 заданным пределам, оперативности перестройки устройства при смене объекта контроля и перехода в режим самоконтроля, Формирователь предназначен дляпре5 образования различных сигналов в уровни сигналов транзисторно-транзисторной логики (ТТЛ) .

Регистр 17 маски предназначен для хранения и выдачи информации, управляющей прохождением импульсов с генератора 18 через элементы И 19. При наличии на входе элемента И 19 разрешающего сигнала с регистра 17 в те- 15 чение времени присутствия на другом входе элемента И 19 единичного информационного сигнала с соответствующего выхода формирователя 16 на вход соответствующего счетчика 20 проходят импульсы стабильной частоты генератора 18. Число этих импульсов, проходящих на вход того или иного счетчика, определяет длительность соответствующего информаиионного сигнала. 25

Группа элементов И 21, группа элементов НЕ 22 и группа дифференцирующих элементов 23 обеспечивают прохождение сигналов со счетчиков íà схему 25 сравнения лишь после окончания счета. Сигналом, разрешающим прохождение сигналов с какого-либо счетчика через соответствующие элементы

И 21, является производная заднего фронта единичного информационного сигнала с соответствующего выхода фор3 мирователя 16 сброс счетчика осуществляется той же производной заднего фронта информационного сигнала с некоторым запаздыванием, обеспечиваемым соответствующим элементом 26 задержки.

Регистр 24 предназначен для хранения и выдачи на схему 25 необходимой информации по временным характерис- 45 тикам сигналов в дискретной форме для анализа схем объекта, Схема 25 сравнения временных интервалов предназначена для сравнения сигналов в дискретной форме, поступающих с группы счетчиков 20 через группу элементов И 21 и регистра 24, а также выдачи результата сравнения в блоки 7 и 8.

На фиг.3 приведены временные диаграммы сигналов, поясняющие принцип

55 работы устройства.

Программа проверки объекта и тестирования устройства, в качестве носителя которой выбрана перфолента, начинается с кода "Начало программы", после которого следует код, определяющий режим коммутации каждого входного-выходного узла, при котором выходы регистра 2 подключаются через группу элементов коммутатора 11 к входам вычитателя 6 и формирователей 16.Далее следует подпрограмма тестового контроля устройства, состоящая из 3n+i строк, где п - максимальное число контактов подключения анализируемой схемы.

Каждые три строки подпрограммы соответствуют определенному каналу тракта контроля, а записанная в них .информация соответствует коду того сигнала с определенными параметрами, которым необходимо произвести контроль канала. При проверке устройства контролируются все каналы прохождения информации. 0 правильности работы устройства свидетельствуют сигналы, поступающие со схем 4 и 25 сравнения на блок 7, который выдает на генератор 1 синхросигнал, по которому формируется следующий тестовый набор, В случае какой-либо неисправности со схемы 4 и/или 25 на блоки 7 и 8 поступает сигнал "Неисправность устройства", по которому блок 7 прекращает дальнейший ввод тестов, блок 8 высвечивает табло !!Неготовность"! а также указывает адрес неисправности устройства, после чего неисправность устраняется оператором и цикл проверки повторяется. Если программа контроля устройства прошла успешно, с перфоленты по сигналу блока 7 в генератор l поступает код "Конец подпрограммы контроля устройства, соответствующий сигнал генератора 1 в блоке 7 вызывает формирование команд возврата в исходное состояние всех блоков устройства, после чего на выходных шинах регистра 10 с генератора 1 устанавливается код, который переводит коммутатор в режим !!Контроль !! объекта, причем узлы коммутатора, соответствующие входам контролируемого объекта, настраиваются на вывод контрольной информации из устройства на объект контроля, а узлы, соответствующие выходам схемь!, устанавливаются в состояние !!Ввод на соответствую!..их входах формирователей 16 устанавливаются требуелыс значения уставок, 1381517

Далее производится контроль объекта. Информация трех строк подпрограммы считывается из генератора 1 в регистры 2, 24 и 17. При этом в каждом

5 разряде регистра 2 формируется кодовая информация, задающая сигнал с необходимыми амплитудными и временными параметрами по каждому контакту контролируемой схемы 5, в разрядах регистра 24 формируются кодовые комбинации, задающие сигналы с требуемым временным параметром по тем контактам с контролируемого объекта, по которым необходим контроль временных характеристик. сигналов, на соответствующих выходах регистра 17 устанавливаются единичные уровни напряжения.

Содержимое регистра 2 по команде из блока 7, вырабатываемой так же, как 20 и в процессе контроля устройства,по коду считывания строки преобразуется в аналоговую форму через преобразователь 3 и поступает через коммутатор ll на контролируемую схему 5. Эта же ин- 25 формация с регистра 2 поступает в схему 4 сравнения, Блок 7 осуществляет опрос контролируемой схемы 5 по всем контактам.

Сигнал в аналоговой форме поступа- 30 ет от контакта через коммутатор 11, вычитатель 6 и формирователи 16. В вычитателе 6 сигнал анализируется по величине сравнения с эталонами верхнего и нижнего пределов анализируе«35 мой амплитуды. Результат преобразуется в дискретную форму и по команде блока 7 подается на схему 4 сравнения, где сравнивается с сигналами,поступающими с регистра 2. Результат 40 сравнения подается в блоки 7 и 8. В формироваТелях 16 коммутаторов уровня сигналов преобразуются в уровни ТТЛ и поступают на вторые входы трехвходовых элементов И. Через те элементы, 45 на первом и втором входах которых присутствуют единичные уровни, на входы соответствующих счетчиков 20

-проходят импульсы с генератора 18.

Поступление импульсов на входы счет50 чиков прекращается с окончанием действия соответствующих единичных сигналов с выходов формирователей на вторые входы элементов И 19. Таким образом, в счетчиках 20 оказываются

55 записанными числа, характеризующие длительность сигналов на соответствующих выходах контролируемого объекта.

Элементы НЕ 22 и дифференцирующие элементы 23 из заднего фронта единичных сигналов с выходов формирователей 16 формируют импульсы, которые разрешают прохождение сигнапов с выходов счетчиков 20 через элементы 21 на схему 25 сравнения временных интервалов, где эти сигналы сравниваются с сигналами, поступающими с регистра 24, Результат сравнения подается в блоки 7 и 8. Если анализируемая схема по данной подпрограмме работает нормально, блок 7 вырабатывает сигнал для считывания следующей программы, и цикл повторяется, По окончании всей программы проверок блок 7 вырабатывает сигнал о годности контролируемой схемы 5, который поступает в блок 8 индикации и высвечивает табло "Годен", В случае несоответствия логического функционирования либо заданных амплитудных и/или временных параметров проверяемой схемы 5 в соответствии с программой, блок 7 вырабатывает сигнал, останавливающий дальнейшую проверку объекта. Этот сигнал поступает в блок 8 индикации, который высвечивает табло Брак", а также указывает адрес неисправности контролируемой схемы, Это позволяет включить в устройство диагностику отказов ° При необходимости дальнейшая проверка контролируемой схемы осуществляется ручным запуском у тройства.

Блок работает следующим образом.

Перед началом работы кратковремен ным нажатием кнопки элементы с памятью устанавливаются в исходное состояние: счетчик 30 — в начальное состояние, триггер 34 — в единичное состояние.

Синхроимпульсы с генератора тестов поступают на вход элемента задержки, который служит для задержки синхроимпульсов относительно соответствующих информационных сигналов на время, необходимое для окончания переходных процессов в блоках, на которые поступают информационные сигналы, Единичный сигнал с прямого выхода триггера 34 разрешает прохождение синхроимпульсов с выхода элемента задержки через элемент И 28, счетный вход счетчика 30, Сигналы с выхода счетчика поступают на входы дешифратора 38 ° Счетчик с дешифратором выполняют функции распределителя импульсов . Сигналы с выходов дешифрато1381517 формула и з о б Р е т е н и я 45

Устройство для контроля логических схем, содержащее генератор тестов, первую схему сравнения, блок шинных формирователей, коммутатор входов-выходов, генератор синхроимпульсов, регистр входов-выходов регистр теста и блок синхронизации,причем первый выход блока синхронизации соединен с входом синхронизации генератора тестов, о т л и ч а ю щ е е55 с я тем, что, с целью повышения достоверности контроля, устройство содержит блок хранения эталона, регистр

50 ра инвертируются элементами НЕ 36 в соответствии с временной диаграммой, приведенной на фиг.4 и последовательно управляют работой блоков 10,2,3, 6,16,48.

Нулевой импульс с выхода дешифратора 38 поступает на вход сброса триггера 34 и устанавливает его в состоя!! 1! ние 0 . При этом происходит останов- 10 ка генератора 1 тестов и блокируется прохождение импульсов через элемент И (это повышает помехоустойчивость схемы).

Если результаты контроля при данном входном наборе положительные (амплитуда и временные параметры выходных сигналов укладываются в заданные пробелы), то на выходах блоков 4 и 25 сравнения устанавливаются еди- 20 ничные уровни сигналов. На этом цикл контроля с одним набором входных сигналов заканчивается, и разрешается дальнейшая проверка °

Следующий цикл проверки начинается с поступления единичных сигналов с выходов блоков 4 и 25 сравнения на входы элемента И 33 ° При этом единичный сигнал с выхода этого элемента, дифференцируясь цепочкой 39, посту- 30 пает на вход элемента ИЛИ-НЕ 35,нулевой импульс с выхода которого поступает на единичный вход триггера 31, устанавливая его в единичное состояние. Этот сигнал запускает ге35 нератор 1 и разрешает прохождение задержанных синхроимпульсов на вход счетчика.

В дальнейшем работа устройства аналогична описанной выше. 40

Если результат контроля в какомлибо цикле отрицательный, то устройство прекращает работу. маски, группу формирователей импульсов, группу элементов задержки, две группы элементов И, вторую схему сравнения, регистр эталонных временных интервалов, группу счетчиков, блок индикации, вычитатель, r ðóïïó цифроаналоговых преобразователей,причем выход генератора синхроимпульсов соединен с первыми входами элементов И первой группы, выходы которых соединены со счетными входами счетчиков группы, группы разрядных выходов которых соединены с группами входов соответствующих элементов И второй группы, входы которых соединены с выходами соответствующих формирователей импульсов группы и через соответствующие элементы задержки группы — с- входами сброса соответствуюших счетчиков группы, счетные входы которых соединены с выходами соответствующих элементов И первой группы, вторые входы которых соединены с выходами регистра маски, информационные входы которого соединены с выходами признака маски генератора тестов, выходы задания эталонного временного кода которого соединены с информационными входами регистра эталонных временных интервалов, группа выходов которого соединена с первой группой входов первой схемы сравнения, вторая группа входов которой соединена с выходами элементов И второй группы, выходы Равно и Неравно первой схемы сравнения соединены с первым входом блокировки блока синхронизац .и и с первым информационным входом блока индикации соответственно, третьи входы элементов И первой группы соединены с выходами блока шинных формирователей и входами соответствующих формирователей импульсов группы, информационные входы блока шинных формирователей соединены с выходами коммутатора входов-выходов и с первой группой информационных входов вычитателя, вторая группа информационных входов которого соединена с группой выходов блока хранения эталона, адресные входы которого соединены с выходами признака адреса генератора тестов, выход признака начала контроля которого соединен с входом пуска блока синхронизации, второй вход блокировки блока синхронизации соединен с выходом Равно второй схемы сравнения, выход "Неравно которой соеди1381517

1О нен с вторым информационным входом блока индикации, вход синхронизации которого соединен с вторым выходом блока синхронизации, третий выход которого соединен с синхровходом вычитателя, группа выходов которого соединена с первой группой информационных входов второй схемы сравнения, вторая группа информационных входов которой 10 соединена с группой выходов признака эталона регистра тестов, информационные входы которого соединены с выходами признака теста генератора тес-. тов, выходы признака входов-выходов 15 которого соединены с информационными входами регистра входов-выходов, выходы которого соединены с управляющими входами коммутатора входов-выходов, информационные входы которого соединены с выходами соответствующих цифроаналоговых преобразователей группы, стробирующие входы которых объединены с четвертым выходом блока синхронизации, пятый выход которого соединен с синхровходом второй схемы сравнения, шестой выход блока синхронизации соединен с синхровходом регистра входов-выходов, седьмой выход блока синхронизации соединен с синхровходом блока шинных формирователей, восьмой выход блока синхронизации соединен с синхровходом регистра теста, входыгвыходы коммутатора входоввыходов являются входами-выходами устройства для подключения к входамвыходам контролируемой логической схемы.

1381517

Фиг.Я Us

0ЕА

UPlfpf

ОБК

УБС

Рож

УБИ ццщщц Заказ ) )85/45 Тираж 704 Подписное

Произв.-иолигр. пр-тие, г. Ужгород, ул. Проектная,