Устройство для сопряжения процессора с внешними устройствами

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных вычислительных машинах для связи процессора с внешними устрйствами (ВУ). Целью изобретения является повышение производительности устройства при работе с различными типами ВУ и расширение его функциональных возможностей. Поставленная цель достигается тем, что в устройство, содержащее блок 10 формирования выходного кода, блок 9 анализа входного кода , элементы НЕ 2 и 3 и пять регистров 4-8, введен блок 1 шифрации команд , включаюший память микропрограмм, регистр микрокоманд и регистр адреса, в блок анализа входного кода введен второй сумматор по модулю два, а блок 10 формирования выходного кода содержит регистр кода обратной связи и третий сумматор по модулю два. 4 ил. &

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (50 4 G 06 F 13 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (2!) 4100956/24-24 (22) 06.08.86 (46) 15.03.88. Бюл. № 10 (72) А. Д. Гвинепадзе, А. Г. Киреев, В. Н. Мартынов, А. В. Мыскин и В. А. Торгашев (53) 681.3(088.8) (56) Авторское свидетельство СССР № 1174933, кл. G 06 F 13/00, 1983, Авторское свидетельство СССР № 1129602, кл. G 06 F 13/00, 1984. (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ

ПРОЦЕССОРА С ВНЕШ НИМИ УСТРОЙСТВАМИ (57) Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных вы„,SU» 1381521 А1 числительных машинах для связи процессора с внешними устрйствами (ВУ). Целью изобретения является повышение производительности устройства при работе с различными типами ВУ и расширение его функциональных возможностей. Г1оставленная цель достигается тем, что в устройство, содержащее блок 10 формирования выходного кода, блок 9 анализа входного кода, элементы НЕ 2 и 3 и пять регистров 4 — 8, введен блок 1 шифрации команд, включающий память микропрограмм, регистр микрокоманд и регистр адреса, в блок анализа входного кода введен второй сумматор по модулю два, а блок 10 формирования выходного кода содержит регистр кода обратной связи и третий сумматор по модулю два. 4 ил.

1381521

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных вычислительных машинах для связи процессора с внешними устройствами (BY).

Целью изобретения является повышение производительности устройства при работе с различными типами BY и расширение его функциональных возможностей.

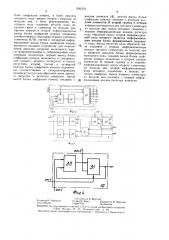

На фиг. 1 представлена структурная схема устройства; на фиг. 2 структурная схема блока шифрации команд; на фиг. 3 структурная схема блока анализа входного кода; на фиг. 4 — структурная схема блока формирования выходного кода.

Устройство (фиг. 1) содержит блок 1 шифрации команд, элементы HE 2 группы, элемент НЕ 3, пять регистров 4 — 8, блок 9 анализа входного кода, блок 10 формирования выходного кода, шину 1 данных от процессора, вход 12 сопровождения кода операций, вход 13 управления от процессора, выход 14 управления процессором, шину 15 выходных данных, шины 16 и 17 соответственно выходной и входной информации устройства, шины 18 и 19 управления устройства.

Блок 1 шифрации команд (фиг. 2) может быть реализован на микропрограммных принципах и содержит регистр 20 адреса, память 21 микропрограмм, регистр 22 микрокоманд.

Блок 9 анализа входного кода (фиг. 3) содержит лва элемента ИЛИ 23, 24, элементы И 25, 26 первой и второй групп, первый и второй сумматоры 27, 28 по модулю два и регистр 29 инверсии.

Блок 10 формирования выходного кола (фиг. 4) содержит третий сумматор 30 по модулю два и резистор 31 кода обратной связи.

Устройство работает следующим образом.

Необходимый режим работы устройства задается процессором. Начальный адрес управляющей подпрограммы, которая обеспечивает требуемый режим работы устройства, поступает по входу 13 на регистр 22, откуда при наличии низкого логического уровня на входе 12 начальный адрес заносится на регистр 20.

По командам вывода из процессора, поступающим по шине 1, данные могут быть занесены на регистр 4 или через блок 10 на регистр 5 с помощью определенных разрядов микрокоманды. По командам ввола информация снимается с регистра 6.

Основным режимом работы устройства является режим с использованием функций, выполняемых блоками 1,9 и 10, обеспечивающими режим универсального автономного управления внешним устройством.

Перед началом обмена информацией блоки 9 и 0 настраиваются на заданный

35 алгоритм управления ВУ путем занесения в них по соответствующим командам кодов настройки, поступающих из процессора через элементы НЕ 2. Причем установка режима и настройка устройства осуществляются только один раз, после чего обмен выполняется всего по одной команде чтения или записи информации.

Способ настройки, независимый от способа кодирования управляющих сигналов BY, заключается в том, что в регистры 29 и 31 процессор заносит информацию, считанную из регистра 8, т. е. коды, соответствующие исходному неактивному состоянию управляющих сигналов BY.

По команде вывода из процессора информация заносится в регистр 4, а в блоке

l0 формируется управляющий код запроса

ВУ. Сумматор 30 реализует функцию независимого изменения заданного разряда в регистре 31. Номер разряда задается кодом маски, поступаюгцим из блока I. По этому запросу внешнее устройство включается в работу, читая содержимое регистра 4. После этого BY выдает код подтверждения, который фиксируется на регистре 8 и по которому в блоке 9 вырабатывается сигнал готовности. По этому сигналу в блоке 1 выбирается новая команда, а в блоке )О формируется новый код обратной связи, который передается в регистр 5. т. е. автоматически снимается выставленный запрос или устанавливается при необходимости новый. Одновременно по управляющим сигналам блока 1 информация из ВУ фиксируется на регистрах 7 и 8, если соответствующие функции разрешены кодами режима. Кроме того, из блока I на выход 14 в процессор поступает сигнал прерывания, а на регистр 6 передачи данных заносится информация из регистра 7 или 8 в зависимости от заданной функции, разрешенной кодом режима.

Процессор узнает о готовности устройства либо программно (анализируя состояние выхода 14), либо через механизм прерывания. Получив готовность, процессор передает в устройство очередную информацию.

Ввод из BY происходит в следующей последовательности. Внешнее устройство выставляет на шины 17 и 19 очередные данные на регистр 7 и управляющие сигналы на регистр 8. Код запроса с выхода регистра 8 поступает на вход сумматора 27. Наличие кода запроса от ВУ означает перевод соответствующего управляющего сигнала BY из неактивного состояния в активное. Сумматор 27 выполняет функцию сравнения предыдущего, запомненного в регистре 29 и текущего, зафиксированного в регистре 8, значений управляющих сигналов BY. В момент изменения требуемого управляющего сигнала на выходе элемента ИЛИ 23 формируется сигнал готов1381521

10

Формула изобретения

55 ности, выполняющий те же функции, что и при записи информации.

Из блока I по сигналу готовности считывается код маски, который формирует с помощью сумматора 30 в регистре 31 новый код запроса BY, который заносится в регистр 5, сообшая ВУ о занятости устройства. Одновременно в регистре 29 формируется с помощью сумматора 28 и кода маски, полученного из блока 1, код, соответствуюший новому состоянию заданных управляюших сигналов ВУ. Приняв сигнал готовности устрйства одним из указанных выше способов, процессор выдает адрес микрокоманды, обеспечивающей передачу данных через регистр 6. Передача данных может также осуществляться в режиме прерывания работы процессора. Одновременно из блока 1 в блок 10 и далее в регистр 5 поступает новый код, указывающий ВУ о готовности устройства для приема следующей информации. После выдачи последних данных ВУ выставляет по шине 19 код конца обмена, который заносится на регистр

8 и далее поступает на сумматор 27.

В момент появления требуемого кода на выходе элемента ИЛИ 24 появляется сигнал конца обмена, поступающий на вход регистра 20 адреса. По новому адресу из памяти 21 по первому входу на регистр 22 заносится новая микрокоманда. Далее с выхода регистра 22 через элемент НЕ 3 в процессор поступает сигнал, сообшаюший ему о завершении ввода из ВУ.

Описанная структура работы устройства для сопряжения является наиболее характерной для большинства ВУ, однако не единственно возможной для данного устройства.

Блок 10 формирования выходного кода обратной связи работает следующим образом.

На регистр 31 кода обратной связи ири соответствующем значении второго выхода регистра 22 заносится код управления непосредственно из процессора через элемент

НЕ 2. Далее в регистре 31 с помощью сумматора 30 могут изменяться значения любых его разрядов, задаваемых кодом маски, поступающим из блока 1. Вновь получаемые коды управления из блока 10 выдаются на регистр 5.

Блок 9 анализа входного кода обратной связи работает следующим образом.

В регистр 29 при соответствующем состоянии четвертого выхода регистра микрокоманд может быть занесен из процессора код, соответствующий исходному состоянию выходных управляющих сигналов ВУ. При изменении состояния определенных разрядов на выходе регистра 8 сумматор 27 отслеживает это изменение и выдает соответствую ций код на первые входы. элементов И 25 и 26. На другие входы этих элементов из блока 1 поступают коды готовности и конца обмена. В слх чае сравнения информации (наличие «!») по каким-либо разрядам на выходах элементов

И 25 или элементов И 26 формируются сигналы готовности или конца обмена, которые через элемент ИЛИ 23 или 24 поступают в блок 1. При этом состояние регистра 29 с помощью сумматора 28 и кода маски, задаваемого из блока I, устанавливается в соответствии с тем конъюнктивным изменением, которое отслежено микропрограммой в блоке I с помощью сумматора 27.

Устройство для сопряжения процессора с внешними устройствам и, содержа и ее блок формирования выходного кода, группу элементов НЕ, блок анализа входного кода, элемент НЕ и пять регистров, причем блок анализа входного кода включает первый сумматор по модулю два, две группы элементов И, два элемента ИЛИ и регистр инверсии, выходы элементов HE группы соединены с информационным входом первого регистра, с первым информационным входом регистра инверсии и с информационным входом блока формирования выходного кода, выход которого подключен к информационному входу второго регистра, первый информационный вход третьего регистра соединен с выходом четвертого регистра, а второй информационный вход третьего регистра подключен к выходу пятого регистра и первому входу первого сумматора по модулю два, второй вход которого соединен с выходом регистра инверсии, выход первого сумматора по модулю два подключен к первым входам элементов И первой и второй групп, выходы которых соединены соответственно с группами входов первого и второго элементов ИЛИ, входы элементов НЕ группы являются входом устройства для подклк чения выходной шины данных процессора, выход элемента НЕ является выходом устройства для подключения входа прерывания процессора, выход первого регистра является выходом устройства для иодклк>чения входной информационной шины внешнего устройства, выход второго регистра и информационный вход пятого регистра являются соответственно выходом и входом устройства для соединения с шинами управления внешнего устройства, выход третьего регистра является выходом устройства для соединения с входнои шинои данных процессора, а информационный вход четвертого регистра является входом устройства для соединения с выходной информационной шиной внешнего устройства, orëï÷àê и1ееся тем, что, с целью повышения производительности устройства, в него введены

1381521

4биг .т

Составитель В. Вертлиб

Редактор И. Рыбченко Текред И. Верес Корректор М. Шароши

Заказ 844i46 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 блок шифрации команд, в блок анализа входного кода введен второй сумматор по модулю два, а блок формирования выходного кода содержит регистр кода обратной связи и сумматор по модулю два, причем первый и второй информационные входы блока шифрации команд соединены соответственно с выходами первого и второго элементов ИЛИ, третий и четвертый информационные входы блока шифрации команд являются входами устройства для подключения выходов сигналов начального адреса микропрограммы и сопровождения кода операции процессора, первый выход блока шифрации команд подключен к синхровходам первого, второго, четвертого и пятого регистров, второй, третий и четвертый выходы блока шифрации команд подключены соответственно к синхронизируюшим входам регистра кода обратной связи, третьего регистра и регистра инверсии, пятый выход блока шифрации команд соединен с входом элемента НЕ, шестой выход блока шифрации команд соединен с вторыми входами элементов И второй группы и первым информационным входом третьего сумматора по модулю два, выход которого соединен с первым информационным входом регистра кода обратной связи, второй информационный вход которого является информационным входом блока формирования выходного кода, выход регистра кода обратной связи соединен с вторым информационным входом третьего сумматора по модулю два и является выходом блока формирования выходного кода, седьмой выход блока шифрации команд подключен к вторым входам элементов И первой группы и к первому

15 информационному входу второго сумматора по модулю два, второй информационный вход которого подключен к выходу регистра инверсии, выход второго сумматора по модулю два соединен с вторым инфор2О мационным входом регистра инверсии.