Устройство для контроля магнитных интегральных схем памяти

Иллюстрации

Показать всеРеферат

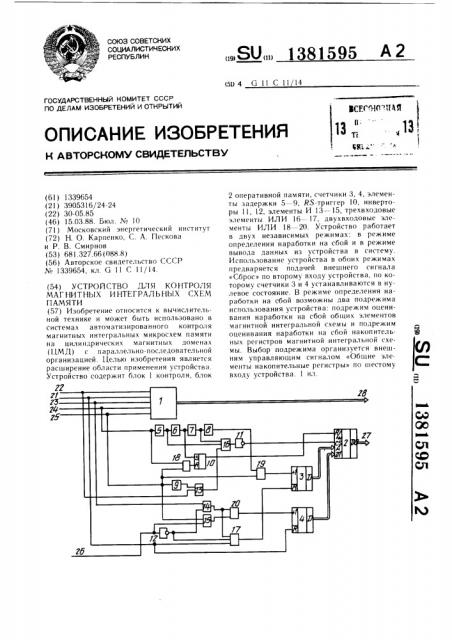

Изобретение относится к вычислительной технике и может быть использовано в системах автоматизированного контроля магнитных интегральных микросхем памяти на цилиндрических магнитных доменах (ПМД) с параллельно-последовательной организацией. Целью изобретения является расширение области применения устройства. Устройство содержит блок 1 контроля, блок 22 21 2 оперативной памяти, счетчики 3, 4, элементы задержки 5-9, / 5-триггер 10, инверторы 11, 12, элементы И 13-15, трехвходовые элементы ИЛИ 16-17, двухвходовые элементы ИЛИ 18-20. Устройство работает в двух независимых режимах: в режиме определения наработки на сбой и в режиме вывода данных из устройства в систему. Использование устройства в обоих режимах предваряется подачей внешнего сигнала «Сброс по второму входу устройства, по которому счетчики 3 и 4 устанавливаются в нулевое состояние. В режиме определения наработки на сбой возможны два подрежима использования устройства: подрежим оценивания наработки на сбой общих элементов магнитной интегральной схемы и подрежим оценивания наработки на сбой накопительных регистров магнитной интегральной схемы . Выбор подрежима организуется внешним управляющим сигналом «Общие элементы накопительные регистры по шестому входу устройства. 1 ил. $б / оо оо ел ;о ел К)

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (5D 4 G ll С ll 14

ВСГУЯР !ИИ

13 „",13

%R i.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCKOMY СВИДЕТЕЛЬСТВУ

71

74

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 1339654 (21) 3905316/24-24 (22) 30-05.85 (46) 15.03.88. Бюл. ¹ 10 (71) Московский энергетический институт (72) Н. О. Карпенко, С. А. Г1ескова и P. В. Смирнов (53) 681.327.66(088.8) (56) Авторское свидетельство СССР

¹ 1339654, кл. G 11 С 11/14. (54) УСТРОЙ СТВО ДЛ Я КО НТРОЛ Я

МАГ НИТНЫХ И НТЕГРАЛЬНЫХ СХЕМ

ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть использовано в системах автоматизированного контроля магнитных интегральных микросхем памяти на цилиндрических магнитных доменах (ЦМД) с параллельно-последовательной организацией. Целью изобретения является расширение области применения устройства.

Устройство содержит блок 1 контроля, блок

„„SU„„1381595 А 2

2 оперативной памяти, счетчики 3, 4, элементы задержки 5 9, RS-триггер 10, инверторы 11, 12, элементы И 13 — 15, трехвходовые элементы ИЛ И 16 — — 17, двух входовые элементы ИЛИ 18 — 20. Устройство работает в двух независимых режимах: в режиме определения наработки на сбой и в режиме вывода данных из устройства в систему.

Использование устройства в обоих режимах предваряется подачей внешнего сигнала

«Сброс» по второму входу устройства, по которому счетчики 3 и 4 устанавливаются в нулевое состояние. В режиме определения наработки на сбой возможны два подрежима использования устройства: подрежим оценивания наработки на сбой общих элементов магнитной интегральной схемы и подрежим оценивания наработки на сбой накопительных регистров магнитной интегральной схемы. Выбор подрежима организуется внешним управляющим сигналом «Общие элементы накопительные регистры» по шестому входу устройства. 1 ил.

1381595

Изобретение относится к вычислительной технике, может быть использовано в системах автомат (г<ировын!(огo контроля магнитных интегральных микросхем памяти ны ци лин.(рических доменах ()),М.ч) с параллельно-последовательной организацией и является toll(>лни гельным к;(вт. (3. № 1 339654.

Цсль из<)бретения ряс)пирение обло TH

I I P I t Ы Р П <э (3 И 51",с Р 0 Й Ст Г> (1 .

1Ь чер)< же изобр,)d (II;3 блок-схемы пр«;(Л а Г 3«ÃO угстр Ойета 1

У«(р()йстно (одерж(п блок контроля, блок ." >И«(.dl)3(3HOkt памяти, счетчики, 3, 4, первыи пятый элем«И)ы задержки 5 9, RS-триггсп I! t, первый 1 и второй 12 и)( верт:)ры, первыи гретий э,í менты И !3

15, первый 16 и нторои 17 трехвхолоныс эл«мсп)ь I, IJ! I(j i. il(()вый Гр< t l: . л)>ухнхо.(013<(« ).:, ме:i (ы j(, )И 8-- 2(). В i < (iiiH iх<. ) I)< ° )t3r) ), Ir !(> > 1, 13 <0(r (i I< |

С ПСРВЬ,1,X .>;(<;() r ... (>; и IHr< тРЕтлй НХ<,;

ВТО!)()1 <) 1 (>< (, > „ <))>< it > < t « . 1«l! i я И ° 1! и ()хо) >р; .: i i < гч „..: "i" лип(пы с H(()j)l

1)хо,(<,» ".. хс; !it. i, рьий нхол Вто )(); < эл, м«п Гя !! 14 i i)t, llitt . и (Ihklм входом 2,( >ст))<;!(и>, (и>ый is, ц, и)го лвухвх<> i()

В<)> ) .,(,!;! 1 1,)8 !! В:, i i: >>ьi)ão ->л(м(<1(:.

3(it <"„>;..; >,)< >ИП(П(! t I i,(. () ГhIM ()XO,(Î;!

"l()J )й н, I . <>Рог(;, l Уx .(ОВ,;; Mt (и ) ) ), !1! I :!, Вход пя)

-: I. м н;, „,,+;ки "..:i((Вь)й В,од T()(Гl.t, „ э. Ii..».« i>: . ., 5 !i (< < (i ii., В>,<) (),с рвОГi.> l)(х

I xti з(» ", .. "Ii i,1 (t l! <11 i ")(.,iktlt(iil (1>п,l ... ",) ("11>(ikt(" <);-! . Гi)()OН I (<> 1

11;«-:;:,::,; (! 1. ; )6,. р

)<Зч j)ri

Ikl;l ri > (i! (Ы«! >(-.

) ((i<>1i« <,: < i ОЛ il(:li:«>. i 31 "l!t )< (< 3,>:.

h! : > .,; i !. i r., I, J> i > -..l< (: H1.

)< ((((,(Stir ° ;. . . 1(H I I < I !), iii . (((.>;!

1fri

f).«H(;! ), )),!., .: 1>. ),< Г(.,;

t3lil X< ), l(i" .,< X « . ;, >>, i! f„; i >, 1, >1 0) ><)i (>

VI«Ii I iI t .Sr С,:,,! ° . (OV Т()<

l 0:i )r ((Ii >, (":,

f()ill < i.:,< „... °,, «.;и.!(l! (<) 1 (,, < . > () ri, . . . tiii, (iIlkl(!

h.! . . I(, . I, .: «!. ><." «I . з t,,i > ,.<)<,(!! <. (;,< (> О, I r It t(«II I

S 1Л<. !i К . . j) (Пrt \t , i t(j> ()Ог()

НХ< (;< °, <.. (!(П > . I I! !), i i Ход «< »ir Ii

: 0i r ., . ;(iI; i " .(l,! (И(.Ii, < it il;i> I> с (!()> н!,< и

< ) <, ; :;,, )< < <) ЭЛ(ilt ii I ° .

lI,,, i! i ) !<), НЫХ<)Л К<:)ор >; <)СЛИНС. СО СЧСT )" " . - i д («! !!> ) < ; ><)J)Mi3!(ИО (и. I

Вы.о (l()ор(гi) с<>(лпн(<;1,<р«< !! (>IM в <Ол();i>

<),!м t!t ()HOI элем«и(а ! I J, 1st!х >.(((<Г)< (><;.:> «<)слиll< H

С Тр! (»i < (>ХО,(ОM fi«(>(.<)I .); ()t XЬХ >, (0()(rt i) элсх!с ti 1 r! 5!.1 о d 1(M«li) <

И )4 < ослиноll с It(ðhым (;;О, (< .(1 трс !(...i

2 днуxH.ходового элемента ИЛИ 20 и с первым входом второго трехвхолового элемента

ИЛИ 17, выход которого соединен с входом сброся счетчика 3, выход третьего элемента

И 15 соединен с вторым входом третьего

) лнух В «>дового элеме(па ИЛИ 20, выход котор<>го соединен со ((егным входом счет.икя 4, информационный выход которого (о«5!H. ft H «входом д;!нных блока 2, выход (310()<>l 0 ипвертора 12 соединен с вторым

)((f3x0;10M !s1opoIo элем«ига И 14 и с вторым

Hx<).«)M t3TopoI о грс хвходового элемента

ИЛ(! 17. (jj)«, ëàãàåìoå устройство работа(т в

lf3t x независимых режимах: режиме Определения наработки Hd сбой, режиме вь)вода ! ) данных из устройства В систему. Исполь<Он; 1(и(xс«)ройств;3 В <>60ltx режимах пред()я! я< (ся )и)дачеи t! II(III!t(l сi)f нала «Сброс»

10 В(орому Входу 22 < (ройствя, fto которому

-):< I !Нк, 3 и счетчик 4 усг()навливаются в

)!) .<<..t b<>t < о«таяние. В J)t.dèM«определения

1,1!)И()огни 1(я сбой нозмо кны l(3d подрежима

<((fI(iль<0Вяния устройства: подрежим оцени (<(ия и;)работки на сбой общих элементов

,tt (и !Н>й ин г(грыльпой схемы; подрежим

,<>Нянин наработки ня сбой накопитель-> с

ji< Гис)рон магнитkl(>ki интегральной схе.:),! Р .6(>j> подрежимы Организуется вне)п-! и>и .;1));3(3;!H(o(((HM си< и )лом «06)цие элеltr. !), 1!< К )ПИтЕЛЬНЫ«()(> ИГ)Р(,!» ПО ШЕСТОМУ

><-.балх "!) . тройствя.

3r), (>(1.1;1f H«Mîå усгрои (но работает сле.: ))(1! м н>разом. ! «)Ним Опреде.(1(H>l и;)работки на сбой. ,«1()0))«(Вы ts . <, : р«жиме протекает

, ):. i. . I(it(0 ПРОЦ(((У С IHХ Ь!ВЯ НИ Я ИНфОР" .t ti r! f! < 1(ЯГНИТНОИ ИП ((i J)H.IЬНОИ СХЕМЬI.

) !,,: r! 3) kt Уll() «((3.()(I<> t)(33 M H (f(f ifrH. I (I!((k(Н ,+,ИМС- ЯВЛЯК)! H ВП<Ч(! ИЕ СИ: НЫЛЫ ! (i l 0Bhl5) ft(> lI il! <)х)> входу 25 усT:.:. i н;<, )и!ибкы» II() II(рвому в оду 21

<(Ihi> . Н >няя сl j)i)пины» по третьему ! (3 )И(ГН«1. III fir)Л << <СС!HИЫС ГОТОВ ); <сльс(ву«г > (О 1, (го с провсряеной ин!«, !ьной схемы считан

iI! <»!т. С.HI I ..;i.. .())Нибкя» указывает

< ) ) и (3 р > ж(I f i ) и ((i ) ks1l H дс- и и Р c H и та и3(ы. Онол(. (.и(ныл «Новая стра<)х<сс мс«fo 10l (H, когда начинается .,:,:tHlft flOISOf0 6;l

1»< 1,.1(,1,110<1 рябо! ы у 1 ðoéñòíà в режиме

I i I>(!«. t kl н н<3 (>або i к! 1(я (бой Явл Я(. т(Я .;<Нф );;я; .:! 0 числе сбоев, вы

:;>ППЫХ КыжЛЫМ Hrlh()flH «ЛЬНЫМ РЕГИСТРОМ ! ><ри <и><;м н ц«лг)м; 1:с)ко.l.!«Иие информации

i„t

X1<)M tr(П ЯХ ПОСЛЕДНИХ t (>ОС (S КажДОГО HdhO,:иi(ë<,>t<>(о (егистря и..: 06 цих элементов, 1 (31 tl и I k! ОИ ft и Гс Г()ы )вki ll () (M;rl. Инфор ма

I(kI5I <: ?????????????????? ????(>.,(<пу«тся блоком конт р(Б О., )h 2 заносят<5l дынные о моментах

1;Кir., i,(НИ51 T«К) 1>((>Л СбОЕВ. В ЯЧЕЙК(, )с нt,<,(1; (ресом фиксируется момент сбоя, -())(,> Х з, >((<«НТОВ, а В >l fi. и h«(! Х < «IДРЕСЯ МИ

138!595 с 1 по К-й — моменты сбоев 1 К накопительных регистров. По завершении испытаний в блоке 2 хранится информация о моментах возникновения последних сбоев, имев ших место в этих испытаниях. Данными для занесения в блок 2 служит содержимое счетчика 4, в котором формируется тот номер считанного с магнитной интегральной схемы бита, под которым этот бит проходил через исследуемый элемент прибора, Порядок прохождения битов через общие элементы магнитной интегральной схемы полностью совпадает с порядком их следования со схемы считывания, поэтому для подрежима определения наработки на сбой общих элементов в счетчике 4 фиксируется текущее число сигналов «Данные готовы».

Что касается порядка прохождения битов через отдельный накопительный регистр, то номер бита, вышедшего с некоторого накопительного регистра соответствует номеру считанного блока данных, поэтому для подрежима определения наработки на сбой накопительных регистров в счетчике битов фиксируется текущее число сигналов «Новая страница». Если считанный бит не совпадает с эталоном, о чем свидетельствует наличие сигнала «Ошибка», содержимое счетчика 4 заносится в блок 2.

Первый сигнал «Данные готовы» сбрасывает RS-триггер 10, устанавливая тем самым режим записи блока 2. Последовательность операций по каждому сигналу

«Данные готовы» следующая: в подрежиме определения наработки на сбой накопительных регистров содержимое счетчика 3 наращивается на «1», в то время как в подрежиме определения наработки на сбой общих элементов счетчик 3 постоянно находится в сброшенном состоянии, обеспечивая задание нулевого адреса блока 2; в подрежиме определения наработки на сбой общих элементов содержимое счетчика 4 наращивается на «1» в случае наличия сигнала «Ошибка» активизируется сигнал выборки блока 2, по которому осуществляется занесение содержимого счетчика 4 по текущему адресу блока 2.

Очередность действий организуется с помощью пятого элемента 9 задержки.

Для подрежима определения наработки на сбой накопительных регистров наращивание содержимого счетчика 4 на «1» происходит по сигналу «Новая страница», и, кроме того, по этому сигналу происходит обнуление счетчика 3 с целью получения соответствия между адресным пространством блока 2 и накопительными регистрами магнитной интегральной схемы.

Режим вывода данных из устройства в систему. Этот режим служит для выдачи в систему данных, сформированных в режиме определения наработки на сбой. Этими данными являются данные о числе сбоев каждого накопительного регистра и прибора в целом и данные о моментах последних сбоев накопительных регистров или обгцих элементов прибора. Управляющим сигналом для устройства в этом режиме служит внешний сигнал «Пересылка» по четвертому входу 24 устройства. Для передачи в систему

К слов, содержащих данные о количестве сбоев, и К слов, содержащих данные о моментах последних сбоев, требуется подать

К сигналов «Пересылка». Данные о кбличестве сбоев поступают на выход 28 устройства, 10 а данные о моментах последни сбоев — на второй выход 27 устройства с выхода данных блока 2.

Последовательность действий в этом режиме следующая: установка режима чтения

15 блока 2 (установка в «!»-состояние RSтриггера 10); активизация входа выборки блока 2, в результате чего очередное слово считывается из блока 2 и фиксируется на втором выходе 27 устройства; установка режима записи блока 2 (установка в «0»20 состояние RS-триггера 1О); активизация входа выборки блока 2, в результате чего нулевое содержимое счетчика 4 заносится в выбранную ячейку блока 2. Таким образом, считывание содержимого каждой ячейки

25 сопровождается ее очисткой (для подготовки блока 2 к новому циклу работы). Нулевое значение момента последнего сбоя в конце испытаний свидетельствует об отсутствии сбоя; содержимое счетчика 3 наращивается на «!».

30 Очередность операций организуется первым четвертым элементами 5- 8 задержки.

Формула изобретенач

Устройство для контроля магнитных инgg тегральных схем памяти по авт. св.

Ме 1339654, отличающеегя тем, что, с целью расширения области применения устройства, оно содержит оперативный блок памяти, счетчик и элементы задержки RS-триггер, инверторы, элементы И, трехвходовые эле40 менты ИЛИ и двухвходовые элементы ИЛИ, причем второй вход первого элемента И соединен с первым входом устройства, третий вход второго трехвходового элемента ИЛИ и вход сброса первого счетчика соединены

4 с вторым входом устройства, первый вход второго элемента И соединен с третьим входом устройства, первый вход первого двухвходового элемента И и вход первого элемента задержки соединены с четвертым входом устройства, второй вход второго двух50 входового элемента ИЛИ, вход пятого элемента задержки, первый вход третьего элемента И и второй вход первого двухвходового элемента ИЛИ соединены с пятым входом устройства, второй вход третьего элемента И и вход второго инвертора соединены

55 с шестым входом устройства, выход первого элемента задержки соединен с входом второго элемента задержки и вторым входом первого трехвходового элемента ИЛИ, вы1381595

Составитель Ю. Розенталь

Редактор М. Товтин ИТехред И. Верее Корректор О Кравцова

Заказ 824/49 Тираж 590 П одписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий ! 13035, Москва, Ж 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 ход которого соединен с входом первого инвертора, выход которого соединен с входом выборки блока оперативной памяти, выход которого является вторым выходом устройства, выход второго элемента задержки соединен с входом третьего элемента задержки и с S-входом RS-триггера, выход которого соединен с входом установки режима чтениязаписи блока оперативной памяти, выход третьего элемента задержки соединен с входом четвертого элемента задержки и с первым входом первого трехвходового элемента

ИЛИ, выход четвертого элемента задержки соединен с первым входом второго двухвходового элемента ИЛИ, выход которого соединен со счетным входом второго счетчика, информационный выход которого соединен с адресным входом блока оперативной памяти, выход первого двухвходового элемента

ИЛИ соединен с R-входом RS-триггера, выход пятого элемента задержки соединен с первым входом первого элемента И, выход которого соединен с третьим входом первого трехвходового элемента ИЛИ, выход второго элемента И соединен с первым входом третьего двухвходового элемента ИЛИ и с первым входом второго трехвходового элемента ИЛИ, выход которого соединен с входом сброса второго счетчика, выход третьего

10 элемента И соединен с вторым входом третьего двухвходового элемента ИЛИ, выход которого соединен со счетным входом первого счетчика, информационный выход которого соединен с входом данных блока оперативной памяти, выход второго инвертора

15 соединен с вторь1м входом второго элемента

И и с вторым входом второго трехвходового элемента ИЛИ.